Накапливающий сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть исполь-зовано в арифметических устройствах различного назначения. Цель изобретения - повышение быстродействия и помехоустойчивости. Накапливающий сумматор содержит вход 1 обнуления, вход 2 синхронизации, управляющие входы 3,4,п разрядов, в каждый из которых входят элементы И 5 и 6,синхронный счетный триггер 7, элемент ИЛИ 3, элемент сложения по модулю два 9, узел 10 формирования переноса. Сумматор имеет входы 11 и выходы 12. Элементы И 5,6 и ИЛИ 8 в каждом разряде сумматора образуют коммутатор 13. 2 ил.

щ С 06 Р 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВ 70РСИОМУ. СВИДЕТЕЛЬСТВУ у,0+x; 9Р;; (1.1) Si

Р, где у х.!

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

l10 ИЗОБРЕТЕНИЯМ И ОТНРЫТ1 ЕМ

ПРИ ГКНТ СССР

1 (21) 4704984/24 (22) 03.05.89 (46) 23 ° 04 ° 91. Бюл. N 15 (72) О.П.Кузнецов, С.В.Антонов и В.В.Исаков (53) 681.325.5 (088.8) (56) Авторское свидетельство СССР

11 1166099, кл. G Об F 7/50, 1984.

Авторское свидетельство СССР

И 813416, кл. С 06 Р 7/50, .1979. (54) НАКАПЛИВАЮЩИЙ СУММАТОР (57) Изобретение относится к вычислительной технике и может быть исполь;зоваио в арифметических устройствах

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах различного назначения.

Цель изобретения — повышение быстродействия и помехоустойчивости.

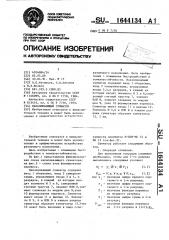

На фиг.l представлена функциональная схема накапливающего сумматора; на фиг.2 — схема узла формирования переноса.

Накапливающии сумматор содержит вход 1 обнуления, вход 2 синхронизации, управляющие входы 3 и 4, и разрядов, в каждый из которых входят элементы И 5 и б, синхронный счетный триггер 7, элемент ИЛИ 8,элемент сложения по модулю два 9,узел

10 формирования переноса. Сумматор имеет входы 11 и выходы 12. Элементы И 5, 6 и ИЛИ 8 в каждом разряде сумматора образуют коммутатор 13.узел

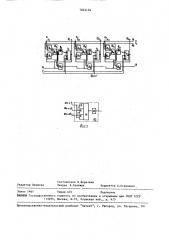

l0 может быть выполнен в виде сово..SU,, 1644134 А 1

2 различного назначения. Цель изобретения — повышение быстродействия и помехоустойчивости. Накапливающий сумматор содержит вход 1 обнуления, вход 2 синхронизации, управляющие входы 3,4,п разрядов, в каждый из которых входят элементы И 5 и б,синхронный счетный триггер 7, элемент

ИЛИ 8, элемент сложения по модулю два 9, узел 10 формирования переноса.

Сумматор имеет входы 11 и выходы 12.

Элементы И 5,6 и ИЛИ 8 в каждом разряде сумматора образуют коммутатор

13. 2 ил. купности элементов И-ИЛИ-НЕ 14 и

НЕ 15 (см.фиг.2), Сумматор работает следующим образом.

1. Операция сложения.

Для выполнения операции сложения необходимо, чтобы для i-го разряда выполнялись следующие условия:

P у, Ч х;у, V Р;х,, (1.2) значение цифры первого слагаемого в i-м разряде; значение цифры второго слагаемого в i-м разряде; значение функции переноса из младшего разряда; значение цифры суммы в i-м разряде; значение функции переноса из i-го разряда в (i+1)-й.

1644! 34

Для схемы на фиг.! значение выходных сигналов для i-го разряда определяется функцией

f0

I(Ф tht1 <(t1 "® (+1 ®

0 Р М 0;(i) (1. 3) Я (t Zt = Б,(ц (Ох;(ц а Р;(Ч У () (1.5) Р = Р ° S; l(S,õ;×Р;х;.

2. Операция сдвига.

Операция сдвига в сторону старших разрядов эквивалентна операции

З()= ()= !ц + З(ц ° (2 1)

Для выполнения операции сдвига необходимо на управляющие входы 3, 4 подать сигналы у = О и у

Затем по входу 2 подается импульс.

В этом случае будет происходить сложение и-разрядного числа S с самим собой, что соответствует операции сдвига в сторону старших разрядов.

3. Операция счета.

Для выполнения операции счета необходимо на входы 11 подать код приращения $S у = 1, у = О, тогда лрч подаче синхроимпульса к содержимому где у, и у („ — значения логичес (М ких уровней на управляющих входах 3 и 4 соответственно.

Дпя выполнения. сложения необходимо на управляющие входы 3 и 4 подать сигналы у = 1 и у О.

На входы 11 х,..., хя — одно из слагаемых.

При этом принимают, что второе слагаемое зафиксировано в триггерах сумматора (у, = S ).

Операция сложения выполняется после подачи импульса по входу 2.

На выходах суммы и переноса формируются следующие сигналы

25 сумматора будет прибавляться число

QS. Иожно, в зависимости от значения кода приращения, реализовать режим прямого и обратного счетов. Например, если необходим прямой счет с приращением K(О, то необходимо подать код прирацения Б = К(2), если необходим обратный счет, то gS = 2 — K 1, где п — разрядность сумматора.

Фо рмула и зоб ре те ния

Накапливающий сумматор, содержащий в каждом разряде счетный триггер и коммутатор, содержащий два элемента И и элемент ИЛИ, прячем первый вход первого элемента И соединен с входом данного разряда операнда сумматора, первый вход второго элемента

И соединен с .выходом счетного триггера данного разряда, вторые входы первого и второго элементов И соединены соответственно с первым и вторым управляющими входами сумматора, выходы первого и второго элемента И соединены с входами элемента ИЛИ, выход счетного триггера соединен с выходом данного разряда сумматора, отличающийся тем, что, с целью повышения быстродействия и помехоустойчивости, в каждый разряд сумматора введены узел формирования переноса и элемент сложения о модулю два, входы которого соединены с выходом элемента ИЛИ данного разряда сумматора и выходом узла формирования переноса предыдущего разряда сумматора, а выход подключен к счетному входу счетного триггера, тактовый вход которого соединен с входом синхронизации сумматора, входы узла формирования переноса каждого разряда сумматора соединены с .выходами счетного триггера и элемента ИЛИ данного разряда сумматора и выходом узла формирования переноса предыдущего разряда сумматора.

1644134 хд

Фиа1

Ome

Al2 2

Редактор Иванова

Заказ )46l Тираж 401 Подписное

БНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 и

Уеп 8

Omn Nl

Составитель В, Березкин

Техред А.Кравчук Корректор А.Осауленко