Д-триггер эсл - типа

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в интегральных схемах для построения блоков хранения и сдвига информации. Цель изобретения - упрощение и увеличение надежности , а также расширение функциональных возможностей. D-триггер ЭСЛ-типа содержит тринадцать транзисторов , пять источников тока и две шины опорного напряжения. Введение новых связей позволяет упростить D-триггер ЭСЛ-типа, а введение двух транзисторов позволяет расширить функциональные возможности за счет обеспечения функции асинхронного сброса. 1 з.п. ф-лы, 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 Н 03 К 3/286

ГОСУДАР СТ В Е ННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4669443/21 (22) 27.03.89 (46) 23.04.91. Бюл. М 15 (72) А.П.Голубев, С,Л.Афиногенов, Л.Б.Богод и В.В.Жук (53) 621.374 (088.8) (56) ЕС gate arrays at 2000 gate eguivalent.—

Electronlc Egeneerlrlg, 1985, February, р. 17.

Trowbridge Mattew. Low power-high

performance. — ЕС1 Gate Arrays

"Semiconductor1nt-82", Luton, 1982, р. 39 — 43.

Изобретение относится к импульсной технике и может быть использовано в интегральных схемах для построения блоков хранения и сдвига информации.

Целью изобретения является упрощение и увеличение быстродействия D-триггера, а также расширение функциональных возможностей.

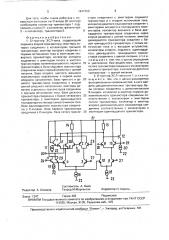

На чертеже представлена схема D-триггера ЭСЛ-типа.

0-триггер ЭСЛ-типа содержит тринадцать транзисторов 1 — 13, два резистора 14 и 15, пять источников 16 — 20 тока; шину 21 питания, общую шину 22, 0-вход 23, С-вход

24, выход 25, шины 26 и 27 опорного напряжения. Эмиттеры первого и второго транзисторов 1, 2 соединены с коллектором третьего транзистора 3, змиттер которого соединен с первым источником 16 тока и эмиттером четвертого транзистора 4, коллектор которогр подключен к змиттерам пятого и шестого транзисторов 5 и 6. Коллекторы шестого и первого транзисторов 6. Ж „1644368 А1 (54) D-ТРИГГЕР ЭСЛ-ТИПА (57) Изобретение относится к импульсной технике и может быть использовано в интегральных схемах для построения блоков хранения и сдвига информации. Цель изобретения — упрощение и увеличение надежности, а также расширение функциональных возможностей. 0-триггер

ЭСЛ-типа содержит тринадцать транзисторов, пять источников тока и две шины опорного напряжения. Введение новых связей позволяет упростить 0-триггер ЭСЛ-типа, а введение двух транзисторов позволяет расширить функциональные возможности за счет обеспечения функции асинхронного сброса. 1 э,п. ф-лы, 1.ил. и 1 и база седьмого транзистора 7 соединены через первый резистор 14 с шиной 21 питания. Базы второго, шестого, восьмого транзисторов 2, 6 и 8 подключены к первой шине 26 опорного напряжения. Базы третьего и девятого транзисторов 3 и 9 соединены с второй шиной 27 опорного напряжения, Эмиттеры девятого и десятого транзисторов 9 и 10 соединены с третьим источником

18 тока. База десятого транзистора 10 соединена с базой четвертого транзистора 4, с змиттером транзистора 11 и четвертым источником 19 тока.

База одиннадцатого транзистора 11 соединена с С-входом 24, база первого транзистора 1 соединена с D-входом 23. База пятого транзистора 5 соединена с эмиттером седьмого транзистора 7 и с вторым источником 17 тока. Коллектор-девятого транзистора 9 соединен с змиттерами восьмого и тринадцатого транзисторов 8 и 13.

Коллектор восьмого транзистора 8 и база двенадцатого транзистора 12 соединены че1644368

25

40

50

55 рез второй резистор 15 с шиной 21 питания.

Эмиттер двенадцатого транзистора 12 соединен с базой тринадцатого транзистора 13 и с пятым источником 20 тока и является выходом 25.

Коллекторы второго, седьмого, одиннадцатого, двенадцатого тринадцатого, транзисторов 2, 7, 11, 12 и 13 соединены с шиной 21 питания, Все источники 16 — 20 тока соединены с общей шиной 22, Коллектор пятого транзистора 5 соединен с коллектором восьмого транзистора 8, а коллектор десятого транзистора 10 — с шиной 21 питания.

На чертеже также указаны два дополнительных транзистора 28 и 29, объединенные базы которых являются дополнительным Rвходом 30. Коллектор и эмиттер первого дополнительного транзистора 28 соединены с коллектором и эмиттером пятого транзистора 5 соответственно. Коллектор и эмиттер второго дополнительного транзистора 29 соединены с коллектором и эмиттером одиннадцатого транзистора 11 соответственно.

0-триггер ЭСЛ-типа работает следующим образом, Пусть сигналы, подаваемые на С- и Dвходы 24 и 23 соответствуют низкому уровню (С = О; D = О). Тогда ток источника 16 тока течет по следующей цепи: шина питания 21, эмиттер-коллектор транзистора 2, эмиттерколлектор транзистора 3, при этом на базе транзистора 7 и, следовательно, на базе транзистора 5 будет высокий потенциал

Цепь, по которой течет ток источника 18, зависит от предыдущего значения на выходе 25.

Допустим, что на выходе 25 низкий логический уровень. Тогда ток источника 18 течет по следующей цепи: шина 21, резистор 15, эмиттер-коллектор транзистора 8, эмиттер-коллектор транзистора 9, Этот ток называет низкий потенциал на базе транзистора 12, на базе транзистора 13 и на выходе 25 сохраняется старое значение.

Пусть сигнал на О-входе 23 возрастет до высокого уровня (О = 1, С = О), Тогда ток источника 16 течет по следующей цепи; шина 21, резистор 14, эмиттер-коллектор транзистора 1, эмиттер-коллектор транзистора

3, при этом на базах транзисторов 7 и 5 возникают низкие потенциалы. Цепь протекания тока источника 18 остается прежней за счет положительной обратной связи: транзистор 13, транзистор 8, резистор 15, транзистор 12 и на выходе 25 сохраняется старое значение.

Пусть сигнал на С-выходе 24 возрастет до высокого уровня (О = l, С = 1). Ток источника 16 течет по следующей цепи; шина 21, резистор 14, эмиттер-коллектор транзистора 6, эмиттер-коллектор транзистора 4. Этот путь протекания тока поддерживается положительной обратной связью: транзистор 7, транзистор 5, резистор 14. Ток источника 18 течет от шины 21 через эмиттер-коллектор транзистора 10. На базах транзисторов 12 и

13 возникает высокий потенциал, соответствующий значению логической единицы на выходе 25. Таким образом происходит запись в схему значения сигнала на 0-выходе

23 по положительному фронту сигнала на

С-входе 24.

При уменьшении сигнала С до низкого уровня (С = О) предыдущее значение сигнала на выходе 25 обеспечивается положительной обратной связью: резистор 15, транзистор 12, транзистор 13, транзистор 8. Пусть сигнал С на входе 24 изменяется с низкого до высокого уровня при низком уровне сигнала на входе 23 (С = 1, 0 = О). (Предыдущее состояние схемы рассмотрено выше (С = О, 0 = О)). Тогда ток источника 16 течет по следующей цепи: шина 21. резистор 15, эмиттер-коллектор транзистора 5, змиттерколлектор транзистора 4, создавая низкий потенциал на базах транзистор" â 12 и 13 и на выходе 25, Следовательно, происходит запись в схему значения сигнала на О-входе

23 по положительному фронту сигнала на

С-входе 24, Таким образом, анализ работы предложенной схемы показывает, по запись информации (сигнал D) происходит по положительному фронту сигнала С и она сохраняется до прихода следующего положительного фронта сигнала С, Следовательно, схема работает как D-триггер.

При подаче на й-вход 30 сигнала высокого уровня, независимо от сигналов на входах 23 и 24, ток источника 16 течет по следующей цепи: шина 21, резистор 15, эмиттер-коллектор транзистора 28, эмиттер-коллектор транзистора 4, Этот ток вызывает низкий потенциал на базе транЯистора

12 и на выходе 25. В этом состоянии схема находится за счет положительных обратных связей до прихода положительного фронта сигнала С. Следовательно, предложенная схема работает как D-триггер с предварительной установкой.

Предложенная схема тактируется положительным фронтом сигнала С. Для того, чтобы схема тактировалась с отрицательным фронтом сигнала С, необходимо базы транзисторов 4 и 10 подключить к источнику

27 опорных напряжений, а базы транзисторов 3 и 9 — к эмиттеру транзистора 11, 1544 1бо

Составитель А. Янов

Редактор А, Шандор Техред М.Моргентал Корректор Н, Король, Заказ 1247 Тираж 483 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Для того, чтобы схема работала с инверсным сигналом íà D-входе (D-триггер) необходимо коллектор транзистора 1 подключить к шине 21, а коллектор транзистора

2 — к коллектору транзистора 6, 5

Формула изобретения

1. D-триггер ЗСЛ-типа, содержащий первый и второй транзисторы, эмиттеры которых соединены с коллектором третьего 10 транзистора, эмиттер которого соединен с первым источником тока и эмиттером четвертого транзистора, коллектор которого подключен к эмиттерам пятого и шестого транзисторов, коллекторы шестого, первого 15 транзисторов и база седьмого транзистора соединены через первый резистор с шиной питания, базы второго, шестого. восьмого транзисторов подключены к первой шине опорного напряжения, базы третьего и де- 20 вятого транзисторов соединены с второй шиной опорного напряжения, эмиттеры девятого и десятого транзисторов соединены с третьим источником тока, база десятого транзистора соединена с базой четвертого 25 транзистора, с эмиттером одиннадцатого транзистора и с четвертым источником тока, база одиннадцатого транзистора соединена с С-входом, база первого транзистора соединена с D-входом, база пятого транзи- 30 стора соединена с эмиттером седьмого транзистора и с вторым источником тока, коллектор девятого транзистора соединен с эмиттерами восьмого и тринадцатого транзисторов, коллектор восьмого и база двенадцатого транзисторов соединены через второй резистор с шиной питания, эмиттер двенадцатого транзистора соединен с базой тринадцатого транзистора, с пятым источником тока и с выходом устройства, коллекторы второго, седьмого, одиннадцатого, двенадцатого, тринадцатого транзисторов соединены с шиной питания, о т.л ич а ю шийся тем, что, с целью упрощения и увеличения быстродействия, коллектор пятого транзистора соединен с коллектором восьмого транзистора, а коллектор десятого транзистора — с шиной питания.

2. 0-триггер ЗСЛ-типа по п.1, о т л и ч аю шийся тем, что, с целью расширения функциональных возможностей, в него введены два дополнительных транзистора, базы которых соединены с дополнительным.

R-входом, коллектор и эмиттер первого дополнительного транзистора соединены соответственно с коллектором и эмиттером пятого транзистора, коллектор и эмиттер второго дополнительного транзистора соединены соответственно с коллектором и змиттером одиннадцатого транзистора.