Преобразователь последовательного кода в параллельный

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к устройствам приема и преобразования информации, и может быть использовано в аппаратуре сопряжения цифровых устройств с полудуплексными двухпроводными каналами связи. Изобретение позволяет формировать импульсы полезных сигналов, перекрывающие помехи, за счет чего обеспечивается повышение помехоустойчивости преобразователя. Преобразователь содержит регистр 1 сдвига, элемент ИЛИ 2, счетчик 3 импульсов , расширитель 4 импульсов, элемент 5 задержки и дополнительный расширитель 6 импульсов, выполненный на триггере 12, счетчике 13 импульсов , элементе ИЛИ 14, элементе И 15 и генераторе 16 импульсов, 1 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

O% (11) (щ) Н 03 М 7/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЬЗТИЯМ

ПРИ ГКНТ СССР (61) 1531225 (21) 4678093/24 (22) ft,04.,89, (46) 23.04.91. Бюл, Р 15 (72). И.З. Кузьменко,. Ю.Д. Карачев, P.Ì. Мотягина и B..Е. Зенин (53) 681.325(088.8) (56) Авторское свидетельство СССР

16 1531225, кл Н 03 М 7/00, 1988. (54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ (57) Изобретение относится к вычислительной технике, в частности к устройствам приема и преобразования информации, и может быть использовано в аппаратуре сопряжения цифровых устройств с полудуплексными двухпроводными каналами связи. Изобретение позволяет формировать импульсы полезных сигналов, перекрывающие помехи, за счет чего обеспечивается повышение помехоустойчивости преобразователя.

Преобразователь содержит регистр 1 сдвига, элемент ИЛИ 2, счетчик 3 импульсов, расширитель 4 импульсов, элемент 5 задержки и дополнительный расширитель 6 импульсов, выполненный на триггере 12, счетчике 13 импульсов, элементе ИЛИ 14, элементе И .15 и генераторе 16 импульсов. 1 з;п. ф-лы, 3 ил.

1644387

Изобретение относится к вычислительной технике, в частности к устройствам приема и преобразования информации, может быть использовано в аппаратуре сопряжения цифровых устройств с полудуплексными двухпроводными каналами связи и является усовершенст-! вованием изобретения по авт. св. 8"- 1531225. l0

Целью изобретения является повышение помехоустойчивости преобразователя.

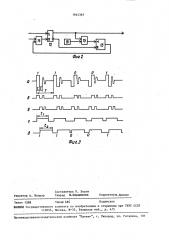

На фиг, 1 приведена блок-схема преобразователя; на фиг. 2 — блоксхема дополнительного расширителя импульсов; на фиг. 3 - временные диаграммы, поясняющие работу преобразователя.

Преобразователь содержит регистр сдвига, элемент ИЛИ 2, счетчик 3 импульсов, расширитель 4 импульсов, ° элемент 5 задержки и дополнительный расширитель 6 импульсов. На фиг. 1 позициями 7, 8.и 9 обозначены соответственно вход сброса, первый и.второй информационные входы преобразователя, позициями 10 и 11 - соответственно информационный и управляющий выходы преобразователя.

Дополнительный расширитель 6 импульсов содержит триггер 12, счетчик

13 импульсов, элемент ИЛИ 14, элемент, И 15 и генератор 16 импульсов, На фиг. 3 соответствующими позициями обозначены,.следующие сигналы; а — сигнал в канале связи;.б и в— сигналы на первом и втором информационных входах 8 и 9> ги д - сигналы на выходах расширителей 4 и 6 им- 40 пульсов; сплошными линиями показаны полезный входной сигнал, а также сиг налы на выходах элементов преобразо вателя при обработке полезного вход ного сигнала. Пунктирными линиями п 4 казаны входные помехи, а также сигналы на выходах элементов преобразователя, являющиеся следствием эти помех, Преобразователь работает следующим образом.

В исходном состоянии сигналом

"Сброс" на входе 7 преобразователь приведен s исходное состояние. Длительность положительного или отрицательного импульса канала связи равна

t. Период следования информационных битов равен Т. На информационные входы 8 и 9 преобразователя поступают импульсы единичных или нулевых битов информации, а также импульсы помех.

При поступлении иэ канала связи единичного бита информации информационный импульс на входе 8 появляется раньше píôîðìaöèoííoãî импульса на входе 9, Этот импульс поступает на вход расширителя 4 импульсов. На выходе расширителя 4 импульсов появляется расширенный импульс длительностью который поступает на информационный вход регистра 1 сдвига. После окончания информационного импульса на входе 8 появляется информационный импульс на входе 9, который поступает на вход расширителя 6 импульсов. На выходе расширителя 6 импульсов появляется расширенный импульс длительностью t который поступает на управляющий вход регистра 1 сдвига и счетный вход счетчика 3 импульсов.

При этом по переднему фронту расширенного импульса, формируемого расширителем 6 импульсов, совпадающему с передним фронтом информационного импульса на входе 9, в регистр 1 сдвига записывается сформированное к этому времени единичное значение информации с выхода расширителя 4 импульсов, а значение счетчика .3 импульсов увеличивается на единицу.

При наличии nîìåõ. (без расширителя

6 импульсов) по каждому импульсу на втором информационном входе 9, включая импульсы .полезного сигнала и импульсы помех, происходит запись в регистр 1 сдвига и увеличение значения счетчика 3 на единицу, что ведет к искажению значения истинной информации на информационном выходе 10, а также. к неправильному счету в счетчике 3 импульсов. Введение расширителя 6 импульсов позволяет выработать расширенные импульсы полезных сигналов второго информационного входа

9, по ширине перекрещивающие помехи, и тем самым исключить срабатывание регистра 1 сдвига и счетчика 3 импульсов от импульсов помех, При поступлении из канала связи нулевого бита информации информационный импульс на входе 9 появляется раньше, чем на. входе 8, Следовательно, к моменту появления переднего фронта импульса на информационном входе 9, и, следовательно, на выходе расширителя 6 импульсов и управляющем входе регистра 1 сдвига, на инФормула

1. Преобразователь последовательного кода в параллельный по авт. св. Р 1531225, отличающий25 с я тем, что, с целью повышения помехоустойчивости преобразователя, в него в веден дополнительный расширитель импульсов, установленный между вторым информационным входом преобра3р зователя и точкой объединения счетного входа счетчика импульсов и входа управления регистра сдвига соответственно своим первым входом и выходом, второй вход дополнительного расширителя импульсов объединен с вторым входом элемента ИЛИ.

2. Преобразователь по п. 1, о тл и ч а ю шийся тем, что . дополнительный расширитель импульсов вы40 полнея на триггере, счетчике импульсой, элементе ИЛИ, элементе И и генераторе импульсов, выход которого соединен с первым входом элемента И, выход которого соединен со счетным

45 входом счетчика импульсов, выход которого соединен с первым входом элемента ИЛИ, выход элемента ИЛИ соединен с входом сброса триггера, прямой выход которого соединен с вторым

gp входом элемента И и является выходом дополнительного расширителя импульсов, инверсный выход триггера соединен с входом сброса счетчика импульсов, второй вход эле55 мента ИЛИ и вход установки триггера являются соответственно вторым и пер вым входами дополнительного расширителя импульсов.

5 164 формационном входе регистра 1 сдвига находится нулевое значение расширителя 4 импульсов, которое записыва-, ется в регистр 1 сдвига. При этом значение счетчика 3 импульсов увеличивается на единицу.

При поступлении последовательности импульсов на информационные входы 8 и 9 преобразователя происходит последовательный сдвиг информации в регистр 1 сдвига и счет поступающих битов в счетчике 3 импульсов.

Для правильной работы преобразователя длительности расширенных импульсов t<, t< должны находитЬся в пределах t(t|, t (Ò вЂ” t. Чем ближе длительность t к верхнему разрешен2 ному пределу, тем выше помехоустойчивость преобразователя.

При поступлении последнего бита информационного слова на выходе счетчика 3 импульсов появляется управляющий сигнал на выходе 11. При приеме следующих байтов информации цикл работы преобразователя повторяется.

После приема каждого слова информации счетчик 3 приводится в исходное состояние сигналом на управляющем выходе 11, который через элемент 5 задержки и элемент ИЛИ 2 поступает на вход сброса счетчика 3 импульсов, подготавливая счетчик 3 импульсов для подсчета бит следующего слова. В том случае, если число бит информации равно коэффициенту пересчета счетчика 3 импульсов (например, число бит в слове равно десяти, а счетчик 3 им.пульсов — двоично-десятичный), то счетчик 3 автоматически переходит в исходное состояние после приема слоsa информации, При этом элемент.

ИЛИ 2 и элемент 5 задержки не используются, а вход -7 сброса преобразователя соединяется непосредственно с входом сброса счетчика 3 импульсов. т

Рассмотрим работу расширителя 6 им пульсов.

В исходном состоянии триггер 12 и счетчик 13 сброшены. При поступлении импульса на вход установки триггера 12 он устанавливается.

При этом сигнал с прямого выхода триггера 12 разрешает прохождение импульсов с выхода генератора 16 импульсов . на счетный вход счетчика 13.

После поступления на счетный вход счетчика 13 соответствующего числа

4387 6 импульсов на его выходе формируется импульс, поступающий через элемент

ИЛИ 14 на вход сброса триггера 12.

Последний сбрасывается, а сигнал с

его обратного выхода поступает на вход сброса счетчика 13 и сбрасываеч его. Таким образом, схема автоматически возвращается в исходное состояние. При этом на прямом выходе триг гера 12 формируется импульс, фронт которого совпадает с фронтом импульса, поступающего на вход установки триггера 12, а длительность равна

15 длительности импульсов генератора 16 импульсов, что составляет длительность С выходного импульса расширителя 6 импульсов. изобретения

1б44387

Составитель Б. Ходов

Техред Л.Сердюкова

Корректор N. демчик

Редактор А. Шандор

Заказ 1248 Тираж 464 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r Ужгород, ул. Гагарина, 101