Устройство защиты от ошибок

Иллюстрации

Показать всеРеферат

Изобретение относится к технике связи и вычислительной технике. Его использование в адаптивных системах передачи дискретной информации по каналам низкого качества позволяет повысить эффективность декодирования и быстродействие устройства. Устройство содержит регистры 1, 2 сдвига, блок 4 декодирования, элемент ИЛИ 5 и блок 8 постоянной памяти . Благодаря введению блока 3 коммутации , делителя 6 частоты и счетчика 7 импульсов в устройстве обеспечивается суперпозиция сегментов двух повторений кодового слова, что позволяет снизить общее число повторов . 2 ил.

СООЗ СОВЕТСНИХ

СОЦИАЛ ИСТИЧЕСНИХ

РЕаЪБЛИН (51}5 Н 03 M 13 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Ъ;

ГОСУДАРСТВЕННЫЙ НОМИ1 ЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

1 (21) 4704944/24 (22) 1 1 .,04. 89 (46) 2.3. 04. 91. Бюл. Р 15 (72) А.Ф. Крупецкий, Д.Е. Глазин, Э.И.Яновский, Ю.И. Николаев, Ф. Г,Афанасьев, А.Д. Никитина, А.К.Грешневиков и А.Я.Титов (53) 621.394.14:681.32 (088.8) (56) Авторское свидетельство СССР

У 1138947, кл. Н 03 M 1/00, 1982.

Авторское свидетель. ство СССР

Р 1444963, кл. H 03 M 13/00, 1985

Авторское свидетельство СССР

Р 866763, кл. Н 04 L 1/08, 1979. (54) УСТРОЙСТВО ЗАЩИТЫ ОТ ОНИБОК. (57) Изобретение относится к технике

Изобретение относится к технике связи и вычислительной технике и может быть использовано в адаптивных системах передачи дискретной информации по каналам низкого качества.

Цель изобретения — повышение эффективности декодирования и быстрогФ действия устройства.

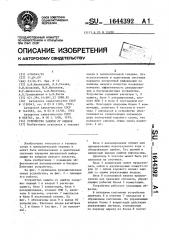

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 — принцип

его работы.

Устройство защиты от ошибок содержит первый 1 и второй 2 регистры сдвига, блок 3 коммутации, блок 4 декодирования, элемент ИЛИ 5, делитель 6 частоты, счетчик 7 импульсов и блок 8 постоянной памяти. На

° фиг. 1 обозначены вход 9 и выход 10 устройства.. Тактовые входы регистров

1, 2 и блока 4 (на фиг ° 1 не показа ны) .

„„SU„, jI 644392 А 1

2 связи и вычислительной технике. Его использование в адаптивных системах передачи дискретной информации по каналам низкого качества позволяет повысить эффективность декодирования и быстродействие устройства.

Устройство содержит регистры 1, 2 сдвига, блок 4 декодирования, элемент ИЛИ 5 и блок 8 постоянной памяти. Благодаря введению блока 3 коммутацйи, делителя 6 частоты и счетчика 7 импульсов в устройстве обеспечивается суперпозиция сегментов двух повторений кодового слова, что позволяет снизить общее число повторов. 2 ил.

Блок 4 декодирования служит для декодир ования исп оль зуемог о кода с обнаружением ошибок. Его прямой и инверсньп выходы ошибки импульсные.

Делитель 6 частоты может быть реализован на счетчике.

Блок 3 коммутации может представлять собой и двухвходовых коммутаторов (n — длина кодового слова) каждый со своим управляющим входом. Ф

Блок 8 постоянной памяти предна- Ж значен для хранения сигналов, управляюш х работой блока 3 коммутации.

Устройство работает следующим об- е разом.

В исходном состоянии устройства делитель 6 и счетчик 7 находятся в сброшенном состоянии. На управляющих входах блока 3 коммутации действуют управляющие сигналы, считываемые по первому адресу из блока 8 посто1644392 янной памяти, задаваемому нулевой комбин идей на выходах счетчика 7.

Первое и второе повторения кодовой комбйнации, поступающей на вход 9, записываются в регистры 1 и

2.Блок 3 коммутации Осуществляет коммутацию по управляющим сигналам, действующим на его управляющих входах из блока 8, своих вторых информационных входов (т.е. выходов второго регистра 2) с входами блока 4, где кодовая комбинация проверяется на Наличие ошибок. Если в кодовой комбинации имеются ошибки, то блок

4 формирует |а прямом выходе ошибки импульсной сигнал, который запускает счетчик 7 и делитель 6. На выходе счетчика 7 появляется следующая ком бинация, определяющая адрес считывания управляющих сигналов из блока

8 постоянной памяти. Блок 3 коммутации по этим управляющим сигналам осуществляет коммутацию своих первых информационных входов с входами блока 4, где (второе повторение) кодовая комбинация снова провер ет,.я на наличие.. ошибок. В случае нади .,яя ошибок ..а прямом выходе ошибки блока

4 появляется управляющий сигнал, увеличивающий состояние счетчика 7 и делителя б «а единицу. По адресу, задаваемому счетчиком 7, из блока 8 постояннсй памяти считываются следующие управляющие сигналы„ до которым блок 3 коммутации осуществляет коммутацию своих входов и выходов сnrласно схеме, представленной на фиг. 2. Как видно из этой схемы, каждое повторение кодового слова делится на гва сегмента (в нумерации на фиг, 2 индексы обозначают номера соответствующих сегментов в повороте). После этого формируют две новые комбинации путем суперпозиций сегментов из разных повторений. При наличии в каждой из новых комбинаций ошибок их сегменты снова делятся на две части, и формируются четьфе новых комбинации и т.д. На i-м шаге число, сегментов в каждом повторении

К = 2 .

Когда образованная в результате таких суперпозиций кодовая комбинация не будет содержать ошибок, блок

4 декоцирования формирует на инверсном выхоце ошибок управляющий сигнал, который поступает через элемент ИЛИ 5, сбрасывает делитель 6 и счетчик 7 в исходное состояние и разрешает стирание информации из регист.ров 1 и 2, Если же в случае перебора

5 всех М возможных комбинаций суперпозиционпых сегментов кодовых комбинаций для заданного числа ни одна из образованных кодовых комбинаций не удовлетворяет требованиям достоверности в блоке 4, то на выходе делителя 6, коэффициент деления которого равен N появляется сигнал переполнения, который через элемент ИЛИ 5 сбрасывает в исходное состояние делитель 6, счетчик 7 и регистры 1 и 2, а на выход 10 кодовая комбинация не поступает (т,е. стирается).

Вероятность правильного декодирования кодовой комбинации с N-ro повтора определяется выражением

t Н ч пА4 1 где Є— вероятность правильного

ПД1 декодирования кодовой ком25 бинации с 1-го повтора.

Предельно достижимое значение

Р „„достигается при К = n, т.е. когда длина каждого сегмента равна одно- . му биту. При этом кодовая комбинация будет неправильно декодирована в случае, если хотя бы в одной одноименной позиции двух комбинаций будет ошибка. Отсюда вероятность правильного декодирования

1 П

35 РЦ вЂ” (- Р ) ) где n — длина кодовой комбинации, à — .вероятность ошибки в диск0 ретном канале.

Например, при Р = 5 . 10 для получения Рп = 0,99 требуется шесть повторов кодовои комбинации вместо десяти у известных устройств.

Формула изобретения

Устройство защиты от ошибок, содержащее первый и второй регистры сдвига, блок постояьной памяти, блок декодирования, инверсный вход ошибки которого соединен с первым входом элемента ИЛИ, о т л и ч а ю щ е е— с я тем, что, с целью повышения эффективности декодирования и быстро55 действия устройства, в него введены блок коммутации, счетчик импульсов и делитель частоты, информационный вход первого регистра сдвига является входом устройства последова5 1644392 6 тельный выход первого регистра сдвига входам делителя частоты и счетчика соединен с информационным входом вто- импульсов, выходы которого соединены рого регистра сдвига, параллельные вы- с вхоцами блока постоянной памяти, ходы первого и второго регистров сдвига выходы которого подключены к управподключены соответственно к первыми ляющим входам блока коммутации, выход

S вторым информационным входам блока ком- делителя частоты соединен с вторым мутации,выходыкоторого соединены с вхо- входом элемента ИЛИ, выход которого дами блока декодирования, информационный подключен ко входам сброса регистров выход которого является выходом уст- 1О сдвига, делителя частоты и счетчика ройства, прямой выход ошибки блока импульсов. декодирования подключен к счетным

1- J шаг

2-й шаг

i-ci шаг

Й а2