Устройство для выделения сигнала фазового пуска

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

МЮ

РЕСГЬ БЛИК

А2 (51)5 Н 04 Т 7/00

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

IlPH ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ (61) 1429330 (21) 4701471/09 (22) 06,,06. 89 (46) 23,.04.91. Бюл. Л"- 15 (72), Г, Б. Галикеев, В. Н. Никитин. и Н.М. Суковицын (53) 621.394.662(088.8) (56) Авторское свидетельство СССР

1429330, кл. Н 04 L 7/00, 1986.

„„SU „„1644397

2 (54) УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ СИГНАЛА ,ФАЗОВОГО ПУСКА (57) Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости приема сигнала фазового пуска путем исправления одиночных ошибок на длине зачетного отрезка. Устройство содержит регистр 1 сдвига, сумматоры 2 и 26 по модулю

1644397 два, ключевые элементы 3, 5, 9, 11, 13, 14, 23 и 24, компаратор 4, элементы ИЛИ 6, 7 и 8, счетчики 10, 17, 19 и 20, реверсивный счетчик 12, дешифратор 15, триггеры 16 и 22 режима, дешифратор 18 конечных комбинаций и триггер 21 задержки на один такт.

В случае, когда синхронизирующая Мпоследовательность принимается из

Изобретение относится к технике электросвязи, может быть использовано для помехоустойчивого выделения синхропосылки и джазового пуска аппаратуры приема двоичной информации и является усовершенствованием устрой- 20 ства по авт. св. И - 1429330.

Цель изобретения — повышение помехоустойчивости приема сигнала фазового пуска путем исправления одиночных ошибок на длине зачетного отрез ка ° >

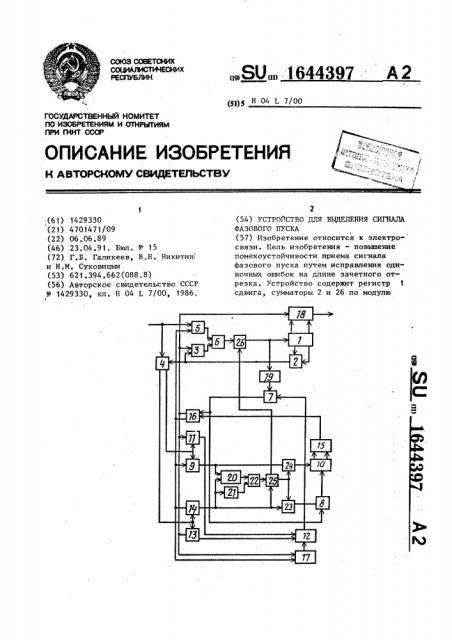

На чертеже показано предлагаамое ус тройство.

Устройство для выделения сигнала фазового пуска содержит регистр 1 сдвига, первый сумматор 2 по модулю 30 два, первый ключевой элемент 3, компаратор 4, второй ключевой элемент

5, первый, второй и третий элементы ИЛИ 6-8, третий ключевой элемент

9, первый счетчик 10, четвертый ключевой элемент 11, реверсивный счетчик 12, пятый и шестой ключевые элементы 13 и 14, дешифратор 15, первый триггер 16 режима, второй счетчик

17, дешифратор 18 конечных комбина- 40 ций, третий счетчик 19, четвертый счетчик 20, триггер 21 задержки на один такт, второй триггер 22 режима, седьмой, восьмой и девятый ключевые элементы 23-25., второй сумматор 26 45 по модулю два.

Устройство работает следующим образом.

Синхронизирующая М-последовательность поступает из канала связи на второй вход компаратора 4 и через первый вход открытого второго ключевого элемента 5 и первый элемент

ИЛИ 6, второи сумматор 26 по модулю два — на вход регистра 1 сдвига и од-. 55 новременно на вход третьего счетчика

19. Регистр 1 сдвига заполняется при нимаемой последовательностью символов. С выхода первого сумматора 2 по канала связи с ошибками .и расстояние между двумя соседними ошибками меньше

М/2 тактов, в устройстве каждая об-наруженная ошибка сигналом несовпадения со второго выхода компаратора 4 сбрасывает в нуль счетчики !О.и 20, подготавливая их к проверке очередных безошибочных интервалов синхронизирующей M-последовательности. 1 ил, модулю два результат проверки принятой последовательности на рекуррентность поступает на первый вход компаратора

4, В последнем производится сравнение результатов проверки с последовательностью, приходящей из канала связи.

При отсутствии ошибок в канале эти последовательности совпадают, Сигнал совпадения, последовательностей с первого выхода компаратора

4 через открытый третий ключевой элемент 9 поступает на второй вход четвертого счетчика 20 и на первый вход открытого девятого ключевого элемента 25, с выхода которого он поступает на первый вход первого счетчика 10, после того как число совпадений превысит порог М, заданный дешифратором 15, сигнал с его выхода поступа ет на установочный вход первого триггера 16 режима и ставит триггер в состояние "1". При этом второй 5, третий 9 и шестой 14 ключевые элементы закрываются, а первый 3, четвертый 11 и пятый 13 ключевые элементы открываются. Вследствие этого регистр 1 сдвига переходит в автономный режим работы.

Одновременно дается разрешение на работу дешифратора 18 конечной комбинации и устройство переходит в режим анализа качества канала, для чего на второй вход второго счетчика 17 поступает сигнал "1", Второй счетчик

17 отсчитывает интервал анализа в

К тактов, после чего с его выхода поступает сигнал ."Сброс" реверсивного счетчика 12. На интервале анализа на вычитающий вход реверсивного счетчика 12 через открытый четвертый ключевой элемент 11 поступает сигнал совпадения, а на суммирующий вход через открытый пятый ключевой элемент

13 поступает сигнал несовпадения.

44397

5 16

Если за время анализа число ошибок

I превышает емкость реверсивного счетчика 12, то считается, что произошло ложное фазирование и сигналом с выхода реверсивного счетчика 12 на вход "Сброс" первого триггера режима 16 устройство переводится в режим анализа последовательности, поступающей из канала связи, Рассмотрим работу устройства, когда синхронизирующая последовательность принимается из канала связи с ошибками.

Если расстояние между двумя соседними ошибками меньше М/2 тактов, то каждая обнаруженная ошибка сигналом несовпадения с второго выхода компаратора 4 сбрасывает в нуль первый счетчик 10 и четвертый счетчик

20, подготавливая их к проверке очередных безошибочных интервалов синхронизирующей последовательности.

Если при приеме синхропосыпки поступает М/2 неискаженных символов, то сигнал с выхода четвертого счетчика 20 переключает второй триггер

22 режима в "1", открыв тем самым седьмой ключевой элемент 23 и подготовив последующие узлы к исправлению возможной ошибки„ Если теперь на оставшихся М/2 тактах работы первого счетчика 10 компаратор .4 обнаруживает ошибки, сигнал несовпадения с второго выхода компаратора 4 через открытый шестой ключевой элемент 14 записывается в триггер 21 задержки, на один такт сбрасывает четвертый счетчик 20 через открытый первый выход седьмого ключевого элемента

23, поступает на второй вход второго сумматора 26 по модулю два, что приводит к инверсии символа, поступающего из канала связи. Таким образом, обнаруженная ошибка исправляется.

Одновременно, через второй выход седьмого ключевого элемента 23 этот сигнал поступает на вторые входы восьмого 24 и девятого 25 ключевых элементов, воспретив тем самым сброс в "0" первого счетчика 10„ На следующем такте работы схемы задержанный на один такт в триггере 21 сигнал несовпадения сбрасывает второй триггер 22 режима в "0", и устройство готово исправить следующую ошибку только после очередных К/12 неискаженных символов.

Таким образом, одна ошибка в синхрониэирующей последовательности, происшедшая после И/2 неискаженных символов, исправляется, Если теперь на оставшихся М/21 позициях синхропосылки приняты неискаженные символы, то сигнал с выхода дешифратора 15 переключает первый триггер 16 режима и устройство переходит в автономный режим работы. Но если на этих позициях есть хотя бы одна ошибка, то сигналом несовпадения счетчики

10 и 20 снова сбрасываются в "0" °

Если во время ожидания синхропосыпки или ее приема до перехода в автономный режим из канала связи поступает серия нулей (из-за обрыва канала связи или по какой-либо другой причине), которая могла бы, заполнив регистр 1, перевести его в автономный режим, то одновременно с заполнением регистра 1 начинает работать третий счетчик 19. После того как из канала поступит N "0" с выхода третьего счетчика 19 через третий элемент ИЛИ 7 на входы "Сброс" первого триггера 16 режима и первого счетчика поступает сигнал, который устанавливает их в исходное состояние. Тем самым исключается возможность ложного перехода регистра в автономный режим при приеме серии "0"

После перехода устройства в автономный режим работы, в момент появления в регистре 1 сдвига комбинации, на которую настроен дешифратор 18 конечной комбинации, последний выдает синхроимпульс фазового пуска, который используется для запуска аппаратуры передачи двоичной информации.

Формула изобретения

Устройство для выдсления сигнала фазового пуска по авт. св. Р 1429330, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости приема сигнала фазового пуска путем исправления одиночных ошибок на длине зачетного отрезка, введены седьмой, восьмой и девятый ключевые элементы, четвертый счетчик, триггер задержки на один такт, второй триггер режима и второй сумматор по модулю два, при этом выход первого элемента ИЛИ соединен с входом регистра сдвига через второй сумматор по модулю два,, 1644397

Составитель Г. Лерантович

Техред Л.Сердюкова

Редактор А. Шандор

КорректоР О.ципле

Заказ 1248 Тираж 394 Подписное

ВНИИПИ Государственного комитета по изобретениям н открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина,101 к второму входу которого подключен первый выход седьмого ключевого элемента, к первому входу которого через второй триггер режима подключены выходы четвертого счетчика и триггера задержки на один такт, йри этом выход третьего ключевого элемента подсоединен к первому входу первого счетчика через девятый ключевой элемент, а выход шестого ключевого элемента соединен с вторым входом третьего элемента. ИЛИ через восьмой ключевой элемент, к второму входу которого и второму входу девятого ключевого элемента подсоединен второй выход седьмого ключевого элемента, к второму входу которого, а также.к первому входу четвертого счетчика и,входу триггера задержки на один такт подключен выход шестого ключевого элемента, а выход третьего ключевого элемента подключен к второму входу четвертого счетчика.