Устройство для подсчета количества объектов на изображении

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

КСПж МН

„„SU„„164

А1 06 К 9/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

М АВТОРСКОМУ С8ИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ HOMHTET

ПО ИЗОТ.КтКНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4273841/24 (22) 30.06.87 (46) 30.04.91. Бил, Ф 16 (71) Киевский институт автоматики, нм. XXV сьеэда KPCC (72) Р.Л, Беэусяк и В,Н. Остапчук (53) 681.327.12(088.8) (56) Авторское свидетельство СССР

Р 610441, кл. С 06 К 9/00, 1978.

Авторское свидетельство СССР

Ф 1277154, кл. С 06 К 9/00, 1986.

2 (54) УСТРОЙСТВО Щ1Я ПОДСЧЕТА КОЛИЧЕСТВА ОБЪЕКТОВ HA ИЗОБРАЖЕНИИ (57) Изобретение относится к автоматике и вычислительной технике и монет быть использовано в процессе распознавания образов для подсчета количества обьектов на изображении. Цель изобретения — упрощение устройства.

Устройство содержит телевизионный датчик 1, блок 2 квантования, блок

3 задержки, синхронизатор 4, блок 5 дифференцирования, компаратор 6, триггер 7, блок 8 ламяти с соответств чОщнми связямие 2 sе.па ф maр 3 ил

1645976

Изобретение относится к автоматике и вычислительной технике и может быть использовано в процессе распознавания образов для подсчета количе5 ства объектов на изображении.

11ель изобретения — упрощение устройстна.

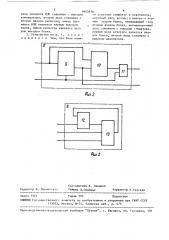

На фиг. 1 представлена блок-схема устройства; на фиг. 2 — схема блока дифференцирования; на фиг. 3 — схема блока памяти.

Устройство содержит телевизионный датчик 1, блок 2 квантования, блок 3 задержки, синхронизатор 4, блок 5 дифференцирования, компаратор 6, триггер 7 и блок 8 памяти.

Блок 5 дифференцирования состоит йз регистра 9, компаратора 10, элемента ИЛИ 11.

Блок 8 памяти содержит сумматор

12 и накопитель 13.

Устройство работает следующим образом.

Видеосигнал с выхода телевизионно- 25 го датчика 1 поступает на вход блока

2 квантования, в котором под воздействием тактовых импульсов с выхода синхронизатора 4 осуществляется его дискретизация и квантование на необходимое число уровней, соответствующее выбранному числу классов. Информационное слово, соответствующее яркости объекта, находится на выходе блока 2 квантования в течение времени его сканирования. С выхода блока

2 квантования коды яркости элементов изображения поступают на вход блока

5 дифференцирования. Компаратор 10 сравнивает код с выхода блока 2 квантования и код, задержанный регистром

9 на один такт. При неравенстве кодов на выходе компаратора 10 формируется сигнал "0", который, будучи простробнрованным отрицательными им- 45 пульсами в элементе ИЛП 11, своим задним фронтом устанавливает триггер

7 в состояние "1" и осуществляет запись информации в накопитепь 13. Подаваемая на информационные входы на50 капителя 13.в момент записи информация с выхода сумматора 12 увеличивается на единицу, если триггер 7 находится в состоянии "1". Состояние триггера 7 в момент записи определяется тем, было ли н течение времени

55 постоянство кодов с выхода блока 2 квантования. Если в течение времени код на входе блока 5 дифферснциронания не изменялся, то значение кода в накопителе 13 не увеличивается на единицу. В противном случае в блоке

8 памяти по адресу, соответствующему классу, к которому относится анализируемый объект, увеличивается содержимое на единицу.

В конце цикла работы после завершения Формирования одного кадра в блоке 8 памяти получают распределение числа изояркостных односвязных объектов по их классам. Причем каждому из классов ставится в соответствие адрес накопителя 13, а содержимое ячейки по этому адресу соответствует числу иэояркостных односняэных объектов.

Таким образом, введение блока дифференцирования, синхронизатора, триггера и блока памяти позволяет сократить аппаратурные затраты. формулаизобретения

1. Устройство для подсчета количества объектов на изображении, содержащее телевизионный датчик, выход которого подключен к первому входу блока квантования, блок задержки, первый вход которого соединен с выходом блока квантования и одним из входов компаратора, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит блок памяти, синхронизатор, триггер и блок дифференцирования, информационный вход которого соединен с выходом блока квантования, спнхрониэирующий вход с выходом синхронизатора, другой вход компаратора соединен с выходом блока задержки, а выход с R-входом триггера, S-вход которого соединен с первым выходом блока дифференцирования, второй выход которого соединен с информационным входом блока памяти, управляющий вход которого соединен с первым выходом блока дифференцирования, адресный вход соединен с выходом триггера, второй вход блока квантования соединен с выходом синхронизатора.

2, Устройство по и„ 1, о т л и ч а ю щ е е с я тем, что блок дифференцирования содержит элемент.ИЛИ, компаратор и регистр, первый вход которого является первым входом блока, второй вход вторым входом блока, а выход соединен с первым входом компаратора, второй вход которого соединен с перным входом блока, первый

Риг.2

Фиг. д

Составитель Н. Давыдов

Техред Л,Олийнык Корректор Н.Ревская

Редактор Л. Пчоли.;. кач

Заказ 1351 Тираж 393 Подписное

ВНИИПИ Государственногс комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r, Ужгород, ул. Гагарина, 101

1 вход элемента ИЛИ соединен с выходом компаратора, второй вход соединен с вторым входом регистра, выход элемента ИЛИ является первым выл<одом блока, выход регистра является вторым выходом блока.

3. Устройство по и. 1, о т л и ч а ю щ е е с я тем, что блок памя645976 ти содержит сумматор и накопитель, адресный вход которого являет я первым входом блока, управляющий -..õîä

5 вторь входом блока, иньормационньп" вход соединен с выходом сумматора, первый вход которого является входом блока, второй вход соединен с выходом накопителя.