Дельта-кодер

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи и предназначено для преобразования аналоговых сигналов в цифровую форму. Целью изобретения является расширение динамического диапазона преобразуемых сигналов. Для достижения поставленной цели в дельтакодер, содержащий компаратор, триггер, селектор пачек символов и цифровой интегратор, дополнительно введены перемножающий ПАП, цифровой слогоььгм Фильтр и блок инверторов. Использовл- .ние в устройстве двойной адаптации, т.е. одновременного управления уровнем входного сигнала компаратора и величиной шага квантования в соответствии с параметрами преобразуемого сигнала, позволяет, помимо улучшения качества преобразования, снизить тпебования к характеристикам элементной базы. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) 01) щ) Н 03 N 3/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГННТ СССР (21) 4462125/24 (22) 18,07 ° 88 (46) 30,04.91. Бюл. ) 16 (71) Рижский погитехнический институт им. А.Я.Пельше (72) Г.H Êîòîâè÷, A.À.ÏóHäÓÐ у

К.Г.Комгров и В,В.XоФмapкс (53) 681.325(088.8) (56) Авторское свидетельство СССР

)1 1381716, кл, Н 03 11 3/02, 1987.

Авторское свидетельство ГССР

N - 1197088, кл. Н 03 N 3/02, 1984. (54) ДЕЛЬТА-КОРЕР (57) Изобретение относится к электросвязи и предназначено для преобразования аналоговых сигналов в цифровую форму. 1(елью изобретения являИзобретение относится к электро, связи, предназначено для преобразования аналоговых сигналов в цифровую форму и может быть использовано в специализированных электронных АТС малой емкости и средней емкости, а также в других областях электронной техники, где требуется высококачественное аналого-цифровое преобразование сигналов.

11елью изобретения является расширение динамического диапазона преобразуемых сигналов.

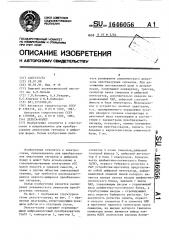

На фиг. 1 изображена структурная схема дельта-кодера; на фиг. 2 — временные диаграммы, иллюстрирующие принципы работы его отдельных узлов.

Дельта-кодер содержит перемножающий цифроаналоговый преобразователь (ЦАП) 1, компаратор 2, триггер 3, ется расширение динамического диапазона преобразуемых сигналов. Для достижения поставленной цели в дельтакодер, содержащий компаратор, триггер, селектор пачек символов и цифровой интегратор, дополнительно введены перемножаюший ПАП, цифровой слоговый

Фильтр и блок инверторон. Использова.ние в устройстве двойной адаптации, т.е, одновременного управления уровнем входного сигнала компаратора и величиной шага квантования в соотве;— ствии с параметрами преобразуемого сигнала, позволяет, помимо улучшения качества преобразования, снизить требования к характеристикам элементной базы. 2 ил, селектор 4 пачек символов, цифровой слоговой фильтр 5, цифровой интегратор 6 и блок 7 инверторов. Совокупность арифметико-логического блока (АЛБ), первого буферного регистра и

11АП устройства-прототипа представляют собой цифровой интегратор, информационной входной шиной которого является первая группа входов арифметико логического блока, выходом — выход

ПАП, управляющим входом †.управляющий вход арифметико-логического блока, а стробпрующим входом — стробирующий вход первого буферного регистра, Совокупность регистра сдвига, первого и второго элементов И и элемента ИЛИ в прототипе является селектором пачек символов, на выходе которого (выходом селектора пачек является выход элемента ИЛИ) логические единицы Форми3 1646056 4

Дельта-кодер работает следующим образом.

Входной аналоговый сигнал V(t) поступает на вход опорного напряжения перемножающего ЦАП 1 и появляется на его выходе, ослабленный в К раз.

Коэффициент ослабления К определяется двоичной кодовой комбинацией на информационных входах перемножающего П,АП 1:

50 ивь1» ААв

А»

11 ех где г — разрядность перемножающего

HAP 1у

А — кодовая комбинация на инфорА мационных входах перемножающего ЦАП 1, представленная

55 руются в случае наличия в дельта-модулированном (ДМ) потоке двух и более элементных пачек (следующих подряд однотипных символов), ИнАормационным и стробирующим входами селектора пачек являются информационный и стробирующий входы регистра сдвига соответственно.

В качестве цифрового слогового

Аильтра, в частности, может быть использован цифровой PN-фильтр„ Аппаратурно данный Аильтр может быть реализован множеством способов, например на регистре сдвига, наборе буферных регистров с параллельной записью и сумматоре, причем на информационный вход Фильтра поступает цифровой ДМ-поток, который с приходом тактовых импульсов на стробирующий вход регистра заполняет его разряды. Каждый бит ДМ-потока поступает на один из информационных входов соответствующего буферного регистра, все остальные входы которого заземлены. Исполь- 25 эование тех или иных входов буферных регистров зависит от конкретных требований к характеристикам цифрового слогового Аильтра, Характеристики фильтра, в свою очередь, определяют- З0 ся конкретными условиями применения дельта-кодера, а также типом и параметрами входного сигнала.

Появление логических единиц в разрядах регистра сдвига вызывает Аорми- З рование заданных двоичных чисел на выходах соответствующих буферных регистров. Просуммировавшись сумматором, эти числа Формируют отклик цифрового фильтра на входное воздействие. 40 в десятичной системе счисления.

Если предположить, что в момент начала работы двоичная кодовая комбинация на выходе цифрового слогового фильтра 5 соответствует числу 0 в десятичной системе счисления (комбинация 000...000), то проинвертированная блоком 7 инверторов комбинация (111...111) на информационных входах перемножающего ПАП 1 соответствует

r числу 2 -1 в десятичной системе счисления, а следовательно, входной сигнал U(t) коммутируется на выход перемножающего ЦАП с максимальным коэАФициентом передачи,, Этот сигнал поступает на вход компаратора 2, где сравнивается с аппроксимирующим сигналом U+(t), присутствующим на другом входе компаратора 2.

В случае, если U(t) ) U (t), на выхоА де компаратора 2 формируется логический ноль, При U(t) (V () компаратор

2 выдает логическую единицу. Двухуровневый сигнал с выхода компаратора 2 поступает на инАормационный вход триггера 3, на стробирующий вход которого подаются тактовые импульсы с шины синхронизации. С приходом каждого тактового импульса логический потенциал, присутствующий на информационном входе триггера 3 записывается в него, появляется на его выходе и поддерживается там как минимум до прихода следующего импульса тактовой последовательности. Таким образом, Формируются биты выходного ДМ-сигнала, каждый иэ которых поступает на выход устройства, à также одновременно на информационный вход селектора

4 пачек символов и на управляющий вход цифрового интегратора 6. С приходом очередных тактовых импульсов фрагмент цифрового ДМ-потока последовательно записывается в селектор

4 пачек символов и анализируется последним на предмет наличия двух и более элементных пачек. Принцип Аормирования выходного сигнала селектора 4 пачек символов при использовании в нем двухразрядного (для наглядности) регистра сдвига иллюстрируется временными диаграммами на

Аиг. 2.

Сигнал Y (t) с выхода селектора

М

4 пачек символов (фиг. 1) поступает на информационный вход цифрового слогового фильтра 5, усредняется им

6056 6

5 164 и поступает в ниде кодовой комбинации, пропорциональной средней плот ности цифрового сигнала Y+(t) на информационные входы цифрового интегратора 6.

Подача на управляющий вход цифрового интегратора битов цифрового ДМсигнала v(t) (с одновременной подачей тактовых импульсов по его стробирующему входу) приводит к тому, что величина аппроксимирующего напряжения U (t) на выходе цифрового интегратора 6 изменяется (либо увеличивается, либо уменьшается) в каждом такте работы устройства на величину, пропорциональную двоичной кодовой комбинации, присутствующей в момент прихода тактового импульса на информационных входах интегратора 6, причем, если текущий бит ДМ-потока соответствует логическому нулю, происходит уменьшение аппроксимирующего напряжения U+(t), в случае же, если текущий бит Y(t)="1", происходит увеличение напряжения U"(t) .

Очевидно, что реализованная таким образом обратная связь приводит к тому (фиг. 2), что аппроксимирующее напряжение U+(t) всегда будет изменяться таким образом, чтобы уменьшить разность (U (t)-U(t)(, т,е. напряжение U4(t) будет аппроксимировать входной сигнал U(t) °

Для улучшения качества преобразования (уменьшения разности между

U+(t) и U(t) и расширения динамического диапазона) в устройство введена адаптация параметров (компандирование) .

Известно, что двух-, трех- и болееэлементные пачки формируются в цифровом ДМ-сигнале тогда, когда аппроксимирующее напряжение U (t) на протяжении двух, трех и более тактов не может

"догнать" быстроизменяющийся входной сигнал V(t). Иаличие в ДМ-сигнале

Y(t) большого числа таких фрагментов (многоэлементных пачек) на протяжении длительного времени свидетельствует о необходимости изменения соотношения амплитуды (уровня) входного сигнала компаратора 2 и величины шага квантования, Это соотношение может быть изменено двумя способами: путем воздействия на величину шага квантования и путем регулирования уровня входного сигнала компаратора 2 (сигнала, поступающего

35 на его первый вход). В устройстве используются обе возможности такого регулирования, которое производится следующим образом. Кодовая комбинация с выхода цифрового слогового фильтра

5, величина которой пропорциональна средней плотности цифровог, РМ-потока (следовательно, амплитуде и частоте входного сигнала V(t), поступает на информационные входы цифрового интегратора 6, а также проинвертированная блоком 7 инверторов на информационные нходы перемножающего ЦАЛ 1. При таком включении величина шага квантования, с которым цифровой интегратор 6 производит аппроксимацию входного сигнала, прямо пропорциональна уровню и частоте входного сигнала, а коэффициент передачи перемножающего ЦАП 1 (по входу опорного напряжения) обратно пропорционален этим величинам. В результате в устройстве производится высокоэффективное компандирование, которое приводит к расширению динамического диапазона преобразуемого сигнала. Любое увеличение крутизны входного сигнала U(t) приводит к увеличению двоичной кодовой комбинации на выходе цифрового слогового фильтра 5, а следовательно, к увеличению шага аппроксимирующего напряжения U (t), уменьшению уроння сигнала на входе компаратора 2 и стабилизации отношения сигнал/шум квантования, что эквиналентно расширению динамического диапазона преобразуемых сигналов. формула изобретения

Дельта-кодер, содержащий компаратор, выход которого подключен к информационному входу триггера, выход которого является выходной шиной и соединен с информационным входом селектора пачек символов и управляющим входом цифрового интегратора, выход которого подключен к первому входу компаратора, а стробирующий вход объединен со стробирующими входами триггера и селектора пачек символов и является шиной синхронизации, о тл и ч а ю шийся тем, что, с целью расширения динамического диапазона преобразуемых сигналов, в него введены цифровой слоговый фильтр, блок инверторов и перемножающий цифроаналоговый преобразователь, при1146П Ь

" J I LLLL 1 LLLLJ

Фиг. 2

Составите л ь Б.11ахна нов

Редактор Л .. 1ежнпна Техред С.11 и улова Корректор H.Ðåâñêàÿ

Заказ 1353 Тираж 463 Подписное

3НЯ11ЦИ Государственного коллитета по изобретениям и открытиям при ГКНТ СССР

113035, Москв», И-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент", r. Ужгород, ул, Гагарина, 191 чем BblxoJl, селектора пачек символов соединен с информационным входом цифрового слогового фильтра, стробирующий вход которого является шиной синхронизации, а выходы соединены с соответствующими информационными входами цифрового интегратора непс средственно и через блок инверторов с соответствующими информационными входами перемножающего цифроаналогового преобразователя, выход которого соединен с вторым входом компаратора, а вход опорного напряжения является входной шиной, 1