Цифровой измеритель электрической энергии многофазной сети

Иллюстрации

Показать всеРеферат

Изобретение относится к электроизмерительной технике и может быть использовано при построении высокоточных цифровых устройств для измерения электроэнергии многофазной сети. Целью изобретения является повышение точности. Цель достигается введением масштабного преобразователя (МП) 4, второго и третьего ключей 24 и 25, преобразователя 6 напряжения вкод(ПНК), комбинационного сумматора 7, двух многоцелевых регистров 8, 18, генератора 9, четырех счетчиков 10, 11, 12, 17, блока 13 выбора частоты, блока 14 фор041 И мирования заполняющих импупьоов ческого элемента 2И 15, двух элементов 2И-НЕ 21, 22, дешис} j , элемента 20 задержки, -входоио i- ческого элемента j И-НЕ 16, fier. , . частоты, п управляемых делителей 20 i,. , 26.п частоты (УДЧ), п регистров 27 1,. ., 27 п п дифференцирующих цепей 28 1, , 28 п n-входового логического элемента п-ИЛИ 29, блока 30 индикации Измерение злекг роэнергии многофазной сети д.. -„я без распараллеливания структурной ,емь по числу фаз. Применение введенм -ч .,иф ровых узлов позволяет путем отп-г вующего опроса всех фаз о лсоят суммарную электроэнергию сети при это1 синхронизация перемчожителя Б и ПИК позволяет исключить влияние коммутации -. ных выбросов на точность устройстеа. Биг тродействующий выбор коэффициентов передач МП 4 и УДЧ отдельно по каждо фазе дает возможность с высокой точностью измерять пофазно энергию. Устройство также содержит п трансформаторов 1.1, ..., 1.п напряжения, п трансформаторов 2.1 2.п тока, первый ключ 3. 2 з.п.ф-лы, 5 ил. Н§ Јь 2 4 СО Щиг1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Па

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4622932/21 (22) 19,12,88 (46) 07,05,91. Бюл, ¹ 17 (71) Институт электродинамики АН УССР (72) А.И.Покрас, B.È.Ïèâîâàð, 1О,Ф,Тесик . и О.КЗ.Чурин, (53) 621.317.76 (088.8) (56) Заявка ФРГ

¹ 3329761, кл, G 01 R 11/00, 1985, Заявка ФРГ

¹ 3534085,,кл. G 01 R 22/00,,1987, (54) ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ МНОГОФАЗНОЙ СЕТИ (57) Изобретение относится к злектроизмерительной технике и может быть использовано при построении высокоточных цифровых устройств для измерения электроэнергии многофазной сети. Целью изобретения является повышение точности.

Цель достигается введением масштабного преобразователя (МП) 4, второго и третьего ключей 24 и 25, преобразователя 6 напряжения в код (П Н К), комбинацион ного суммато. ра 7, двух многоцелевых регистров 8, 18, генератора 9, четырех счетчиков 10, 11, 12, 17, блока 13 выбора частоты, блока 14 фор„„Я2„„1647443 А1 мирования заполняющих импульсс в, ло, . ческого элемента 2И 15, двух лоп носках элементов 2И-НЕ 21, 22, деши<1 ра;:Ч . элемента 20 задержки, j-входово.:::: ческого элемента j И-НЕ 16, делнтс-.:,.-,:

Частоты, и управляемых делителей 26, i,..., 26,пчастоты (УДЧ),,и регистров 27,1, ..., 27 и п дифференцирующих цепей 28.1, .„, 28л и-входового логического элемента и-ИЛИ

29, блока 30 индикации, Измерение электроэнергии многофазной сети д;.".—.:.-.":÷ без распараллеливания струк гурией !.,хемь. по числу фаз. Применение введенн:. .; цифровых узлов позволяет путем бь:.:о-дс . твующего опроса всех фаз и; еря; . суммарную электроэнергию се1и, при зто синхронизация перемножителя 5 и ПНК : позволяет исключить вл MRние коммутацжнных выбросов на точность устройства. Бь.с тродействующий выбор коэффициентов передач МП 4 и УДЧ отдельно лс; кажда:. фазе дает возможность с высокой точностью измерять пофазно энергию. Устройство также содержит и трансформаторов

1.1, ..., 1.п напряжения, и трансформаторов 2.1, ..., 2.п тока, первый ключ 3, 2 з,п.ф-лы, 5 ил.

1647443

Изобретение относится к электроизмерительной технике и может быть использовано IIp11 по1 троении высокоточных цифровых устройств для измерения электроэнергии многофазной сети, Целью изобретения является повышение точности измерения электроэнергии многофазной сети.

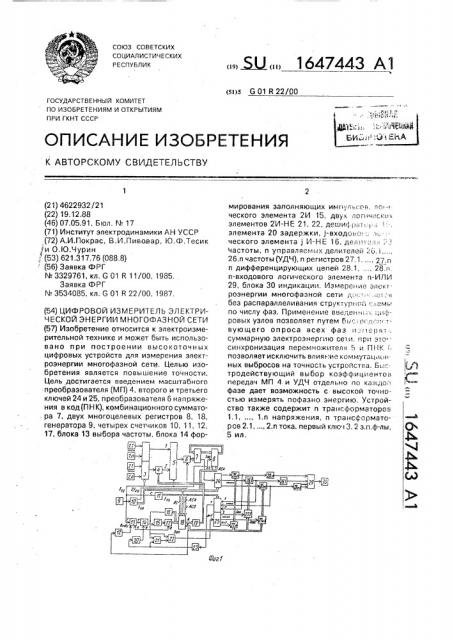

На фиг. 1 представлена блок-схема цифрового измерителя электрической энергии многофазной сети, на фиг, 2 а-в — блок-схе-. мы умножителя, блока выбора частоты и блока формирования заполняющих импульсов соответственно; на фиг. 3 и 4 — временные диаграммы работы устройства; на фиг, 5 — характеригтики умножителя.

Цифровой измеритель электрической энергии м11ого1за".Hoé сети содержит входные тра1 1сформаторь1 1.1, ..., 1.п напряжения, входные трансформаторы ".1, ...„2.п тока, первый ключ 3, масштабный преобразователь 4, умножитель 5, преобразователь

6 напряжения в код., комбинационный о Мматар 7., первый многоцелевой регистр 8, L 8I.IBpBTGp 9, IT8pBbIA, второй и третий чики 10 — 12 соответственно. блок 13 выбора частоты, блОк 14 формирования заполняющих импульсов, логический элемент . : "1 15, логический элемент jN-HE 16, четвертый счетчик 17; второй многоцелевой регистр

18, дешифратор 19, элемент 20 задержки, первый и второй логические элементы 2ИНЕ 211 и 22 соответственно, делитель 23 частоты, второй и третий ключ 24 и 25, управляемые делители 26.1...„26.п частоты, регистры 27,1, ..., 27.п, дифференциру1ощие цепи 28.1, ..., 28.п, логический элемент

ПИЛИ 19 и блок 20 индикации.

Трансфор1латоры 1,1, ..., 1 и напряжения и трансформаторы 2.1, „„2.п тока подключены к первым и и к вторым и входам ключа 3 соответственно. Первый выход ключа 3 соединен с первым входом умножителя

5, а второй выход через масштабный преобразователь 4 — к второму входу умножителя

5, выход которого через преобразователь 6 напряжения в код соединен с вторым входом комбинационного сумматора 7, Выход последнего подключен к входу многоцелевого регистра 8, который первым. выходом соединен с первым входом комбинационного сумматора 7. Выход генератора 9 подключен к входу записи многоцелевого регистра 8, входу управления умножителя 5, к тактовому входу блока 13 выбора частоты, через счетчик 11 — к входам адреса записи и адреса считывания В многоцелевого регистра 18 и к управляющему входу ключа 25, а также непосредственно к входу счетчика 10, первый выход которого подключен к управляю цему входу преобразователя 6 напряжения в код, а второй выход — к управляющим входам ключей 3 и 24, к входам первого адреса считывания А многоцелевых регист-. ров 8 и 18 и,к входу адреса записи многоцелевого регистра 8. Выход блока 13 выбора частоты через блок 14 формирования запоминающих импульсов соединен с вторым входом логического элемента 2И 15, выход которого через счетчик 17 подкл1очен к входам многоцелевого регистра 18 и логического элемента )И-HE 16, который выходом соединен с первыми входами логических элементов 2И-НЕ 21 и 22.

Первый выход А многоцелевого регистра 18 через дешифратор 19 подключен к управляющему входу масштабного преобразователя 4, а его второй выход В через регистры 27.1, „27.п — к управляющим входам управляемых делителей 26.1, .„, 26.п частоты соответственно, Младший разряд второго выхода В многоцелевого регистра

18 через счетчик 11 соединен с входом выбора частоты блока 13 выбора частоты, Выход переноса комбинационного сумматора

7 подключен к входу ключа 24, первый выход которого через управляемый делитель 26.п

-астоты и дифференцирующую цепь 28.п подкл10чен к первому Входулогического элемента ПИЛИ 29. Выходы ключа 24 со второго

-а п-й через управляемые делители 26.1...„

26.(г.-1) частоты и через дифференцирующие цепи 28.1, .„28,(п-1) соединены с входами логического элемента ПИЛИ 29 с второго по и-й соответственно, выход которого соединен с входом блока 30 индикации.

Выходы управляемых делителей

26,1, „., 26.п г1одключены к соответствую щим входам ключа 25 с первого по п-й.

Первый выход ключа 25 через делитель 23 частоты и элемент 20 задержки соединен с входами сброса блока 13 выбора частоты, блока 14 формирования заполняющих импульсов и счетчика 17, а через делитель 23 частоты — с вторым входом логического элемента 2И-НЕ 21, выходом подключенного к второму входу логического элемента 2И-НЕ

22. Выход последнего соединен с входом записи многоцелевого регистра 18 и с (и+1)-м входом ключа 25, выходы которого с второго по (и+1)-й подключены к входам записи регистров 27.1...„27.п соответственно.

Умножитель 5 (фиг, 2а) содержит аналого-цифровой преобразователь 31 (АЦП 31) и

55. умножающий цифроаналоговый преобразователь 32 (ЦАП 32), Второй вход умножителя

5 через АЦП 31 подключен к входу ЦАП 32, вход опорного напряжения которого соединен с первым входом умножителя 5, а выход — с выходом умножителя 5, управляющий вход

1647443 которого подключен к управляющему входу

АЦП 31.

Блок 13 вы бора частоты (Б В Ч 13) (фиг. 2б) содержит пятый счетчик 33, инвертор 34, второй логический элемент

2И 35, логический элемент ЗИ и первый и второй логические элементы 2 ИЛИ 37 и 38 соответственно. Тактовый вход БВЧ 13 подключен к счетному входу счетчика 33, первый выход которого соединен с первыми выходами логических элементов 35 и

36, которые выходами подключены к первому и второму входам логического эле мента 37, выход последнего подключен к выходу БВЧ 13 и к первому входу логического элемента 38, второй вход которого соединен с входом сброса БВЧ 13, а выход — с входом сброса счетчика 33. Вход выбора частоты БВЧ 13 подключен через инвертор

34 к второму входу логического элемента 35 и непосредственно — к третьему входу элемента 36, второй вход которого соединен с вторым выходом счетчика 33.

Блок 14 формирования заполняющих импульсов(БФЗИ 14) (фиг. 2в) содержит второй элемент .39 задержки, счетчик 40 с . предварительной установкой и счетчик — распределитель 41 импульсов . Тактовый вход БФЗИ 14 подключен к счетному входу счетчика 40 с предварительной установкой, вход сброса которого соединен с входами сброса счетчика-распределителя

41 импульсов и БФЗИ 14. Выход БФЗИ 14 соединен со счетным входом счетчика 41, с выходом переноса счетчика 40 и через элемент 39 задержки — с входом записи счетчика 40, вход предварительной установки которого подключен к выходу счетчика 41.

Устройство работает следующим образом.

Работа блоков цифрового измерителя электрической энергии синхронизирована выходными импульсами частоты f>y генератора 9, а также кодами на втором выходе управляющего счетчика 10 и на выходе управляющего счетчика 11, которые циклически изменяются с частотами fzy и f3y соответственно. Кроме того, для управления запуском АЦП 31 в умножителе 5 и преобразователя 6 напряжения в код используется импульсная последовательность частоты 2fzy с первого выхода счетчика 11. Причем

12у = ", 3„=, (1)

f1, fl

2 q где z, q — целые числа, причем 1 < z < q (поэтомУ f1y > fzy > тэу)

В результате этого с частотой опроса f2ó происходит переключение ключей 3 и 24, а

55 также циклическое изменение адреса записи многоцелевого регистра 8 и адресов считывания А многоцелевых регистров 8 и 18, а с более низкой частотой опРоса f3y — пеРеключение ключа 25 и циклическое изменение адресов записи и считывание В многоцелевого регистра 18.

Многоцелевые регистры 8 и 18 представляют собой устройства, которые записывают входную информацию по переднему фронту сигнала на входе записи в ячейку с адресом, установленным на входе адреса записи, и производят считывание информации на выходы А и В из ячеек, адреса которых определяются управляющими кода: ги на входах адреса считывания А и В соответственно. При этом количество используемых ячеек в регистрах 8 и 18 определяется количеством фаз и в сети. Многоцелевой регистр 8 в совокупности с комбинационным сумматором 7 образует и-фаэный накапливающий сумматор, а многоцелевой регистр 18 используется в предлагаемом цифровом измерителе для приема, хранения и считывания сформированных кодовых значений MF, определяющих коэффициенты усиления К4,1, ..., К4 и масштабного преобразователя 4 и коэффициенты деления частоты К26.1, ..., К26,п управляемых делителей

26,1, ..., 26.п частоты отдельно по каждой фазе. Причем для каждой F-й фазы эти коэффициенты определяются выражением

К4.F = К26.F = 2 " (где Ме — целое число) и автоматически подбираются таким образом, что умножитель 5 и преобразователь 6 напряжения в код постоянно работают на узком оптимальном участке своих рабочих характеристик независимо от величин фаэных токов.

Выходные сигналы трансформаторов

1.1, .;., 1.п напряжения и 2,1, ..., 2.п тока с частотой f2y ЦикЛичЕСКИ ОпРашиваются пРи помощи ключа 3, С такой же частотой fzy изменяются коэффициенты усиления

К4.1, ..., К4.п масштабного преобразователя 4, которые для F-й фазы поступают из

F-й ячейки многоцелевого регистра 18 на его выход А и далее через дешифратор 19— на управляющий входданного масштабного пРеобРазователЯ. ВРемЯ Т t = 1/fzy поДключения сигналов напряжения и тока F-й фазы к входам умножителя 5 назовем тактом, а время Тц = n/fzy опроса ключом 3 всех п фаз — циклом измерения.

Таким образом, при кратковременном подключении напряжения и тока F-й фазы на выходе умножителя 5 на -м такте сформируется аналоговая выборка мгновенной мощности PF(i) l647443

PF (i) = @.F K2.F K4F К5 .

Й7 .

Ug sin(1 !+ о ) Р 1

iP.sin(„„v.l+q i„) (2) где КьF, Кг.F, К!.F, К вЂ” коэффициенты передачи, нумерация которых совпадает с номерами соответствующих блоков;

Ю Ю

U F, F — амплитудные значения напряжения и тока и-й гармоники F-й фазы,причем1 v m,О F и;

N — отношение частоты f2 к частоте

;"! первой гармоники входных сигналов, К = f2 / 1

g uF, ф — фазовые сдвиги напряжеУ V ния и тока F-й фазы v -й гармоники относительно нуль-перехода напряжения первой фазы первой гармоники, Управляющие импульсы с первого выхода счетчика 10 запускают в начале каждого i-ra такта АЦП 31 умножитель 5 и преобразователь 6 напряжения в код, Поэтому по окончании i ãî такта измерения при подключении F-й фазы на выходе преобразователя 6 формируется кодовое значение выборки Рг(!) мгновенной мощности, когорое хранится на его выходе в течение всего следующего (!+1)-го такта. 8 течение i-ro такта на выходе преобразователя 6 напряжения в код хранится код мгновенной мощности Р(р-1)(!-1) предыдущей фазы, который поступает на вход и-фазного накапливающего сумматора, состоящего из сумматора 7 и регистра 8. Многоцелевой регистр 8 тактируется по входу записи выходными импульсами генератора 9 с частотой f>y, которая в Z раз превышает частоту

f2 . При этом запись и считывание в многоцелевом регистре 8 осуществляется через ячейку с номером F, что определяется соответствующим кодом на его входах адреса записи и адреса считывания А, который также поступает и на управляющий вход ключа

24, Таким образом, в течение !-го такта измерений при подключении ключом 3 сигналов напряжения и тока F-й фазы в F-й ячейке многоцелевого регистра 8 с высокой частотой f>y суммируется кодовое значение выборки Р(г-1!(!-1)(F-1) F-й фазы, сформированное по окончании предыдущего такта

SF (i) = 7 Kl,F К2:F K4F К5 К6 .

° l F.g . sin(" v (i — 1)+ ф iF ),(3) где Яр(!) — сумма кодовых значений выборки мощности P(F->)(l-1), которые Z раз течение

i-готакта просуммировались через F-ю ячейку и-фазного накапливающего сумматора;

Кв — коэффициент передачи преобразователя 6.

В результате этого на выходе переноса сумматора 7 на протяжении l-го такта измерения с частотой, пропорциональной значению Р(-1)(!--1), формируется пачка импульсов, которая подключается ключом

24 через соответствующие управляемый делитель 26.(F-1) частоты и дифференцирующую цепь 28.(F-1) к (F-1)-му входу элемента

ПИЛИ 29 и накапливается в блоке 30 индикации. Такое высокочастотное тактирование п-фазного накапливающего сумматора позволяет намного повысить быстродействие при выборе коэффициентов передачи преобразователя 4 и делителей 26.1, ..., 26 и.

Коэффициенты усиления масштабного преобразователя 4 и управляемого делителя

26.F частоты для любой F-й фазы равны, поэтому средние частоты импульсов на выходах управляемых делителей 26,1, ..., 26.п частоты однозначно определяют количество электроэнергии соответствующих фаз. Отсюда наряду с общим значением электроэнергии и-фазной сати, формируемым в блоке 30 индикации, можно с высокой точностью измерять электроэнергию отдель40 нь х фаз

Таким образом, за L циклов измерения в блок 30 индикации предлагаемого цифрового измерителя поступит количество импульсов Е!ч(!), пропорциональное

46 измеренной электроэнергии многофазной сети в соответствии с выражением

n m

ЕМ(L) =7 7, К>.F Кг.F QF

1=! г =--1й=1

50 % Ke Кз Кгб г

UF sin!, (пь+Р)+ ф Г ) ! г sin(„(п1+Е) + ф ), (3) где - номер цикла;

Кб, К7,8, K26F — коэффициенты передачи соответствующих по нумерации блоков;

Рассмотрим кратко процесс выбора коэффициентов передачи, время которого

1647443

10 определяется для каждой из фаз периодом тз, = 1Лз,.

Выходные импульсы генератора 9 с чаСтОтай f1y ПОСтУПаЮт На таКтОВЫй ВХОД

БВЧ 13, который в зависимости от единичного или нулевого сигнала на входе выбора частоты вырабатывает на своем выхоДе импУльсы с частотой fey = 11у/х или f5y = 2f1y/Зх = 214у/3 соответственно, (где х — целое число), Эти импульсы поступают на тактовый вход БФЗИ 14 и вызывают формирование на его выходедвоичной последовательности заполняющих импульсов, период поступления каждого следующего из которых в два раза больше предыдущего (фиг. 3, б), В течение времени Тзу пачки импульсов с выхода управляемого делителя 26.F частоты одной из фаз, проходя через ключ 25 и управляющий делитель 23 частоты, преобразуются в последовательность импульсов с относительно равномерным периодом, Далее эти импульсы при единичном выходном сигнале элемента 16 через логические элементы 21 и 22 поступают на вход записи многоцелевого регистра 18 и через ключ

25 — на вход записи соответствующего регистра 27, F. 8 резул ьтате этого в течение каждого периода выходных импульсов делителя 23 частоты, пропорциональных энергии F-й фазы, в счетчике 17 накапливаются выходные импульсы БФЗИ 14. По окончании каждого периода импульсов на выходе делителя 23 частоты происходит запись выходногo,êoäý MF счетчика 17 в F-ю ячейку многоцелевого регистра 18 и через выход

— в соответствующий регистр 27.F, после чего в целях синхронизации происходит сброс блоков 13 и 14 и счетчика 17 и весь процесс повторяется снова, При этом адрес ячейки F определяется кодом F, поступающим на входы адреса записи и адреса считывания В с частотой fey, s (q/z) раз меньшей частоты fry Отсюда частота считывания коэффициентов усиления по выходу А и коэффициентов деления по выходу В в многоцелевом регистре 18 различна и отличается в (q/z) раз.

Логический элемент 16 необходим для надежного установления максимального коэффициента усиления К4,Г для F-й фазы с нулевой или минимальной нагрузкой. В этом случае период выходных импульсов делителя велик, и при появлении на выходе счетчика 17 максимального кода (все единицы) перепад в ноль выходного сигнала логического элемента |N-HE блокирует элемент

2И 15, запрещая дальнейший счет в счетчике 17, а также, проходя через элементы 21 и

22, осуществляет запись этого максимального кода Мр " в многоцелевой регистр 18 и через его выход  — в соответствующий регистр 27.F.

При вариациях нагрузки и неравномер5 — ности выходных импульсов делителя 23 частоты могут возникать сбои и неустойчивый выбор коэффициентов передачи преобразователя 4 и делителя 26.1, ..., 26.п. Для устранения этого явления в предлагаемое

55 устройство введены счетчик 12 и блок 13

Если при одной выходной частоте ВВЧ 13 происходят сбои по младшему разряду выхода В многоцелевого регистра 18, то выходной логический уровень счетчика 12 изменяется на противоположный. что изменяет и выходную частоту ББЧ 13 на д;и...., Поэтому сбои и неустойчивая pç,iîiл .х:..t устраняются полностью.

Умножитель 5 (фиг. 2 а) перемножение кода фазного;-,, л, ветствующую аналоговую выборк . напряжения путем совместного фу; ционирования АЦП 31 и ЦАП 32. C:L.! ронизация умножителя 5 происхоДит по е. в управляющему входу.

БВЧ 13 (фиг. 2 б) производит делен.; х раз счетчиком 33 входной пгслсдов .г.,;. ности импУльсов частоты f! y. ф::Ð!-л1Ров:-л" .. на выходах логических элементов 2I:". 3 - i-.,:i

36 сигналов частоты fpy или 15, соотп; т. «!но в зависимости от уровня сигнал» выбора частоты на входе инвертора 34, и далее выдачу на выход управляющих импул,с;; . через элемент 2ИЛИ 37. Импуль -.",!1 на ь,<, де сброса БВЧ 13, проходящим через .: . мент 38 на вход сброса счетчика 3 производится синхронизация данного г i ка.

Рассмотрим работу БФЗИ 14 (фиг 2 г

Сигнал сброса устанавливает счетчики О „

41 в нулевое состояние. После этого ы:",:. ходе счетчика 40 с предварительной ус-;- новкой формируется импульс, поступа о ций на счетный вход счетчика 41 распределителя импульсов и с некоторой задержкой — на вход записи счетчика 40, В результате этого счетчик 40 предустанавливается в состояние 20. Каждый импульс, поступающий на счетный вход счетчика 40, вызывает вычитание единицы из числа, записанного в ходе предварительной установки. При достижении нуля на выходе переноса счетчика 40 с предварительной установкой вновь появляется импульс, в результате чего на следующем по старшинству выходе счетчика 41 распределителя импульсов появляется сигнал логической единицы, и счетчик 40 предустанавливается в состояние 2 . Далее

1 процесс повторяется до тех пор, пока на входы сброса счетчиков 40 и 41 не поступит

1647443

HF

U умн5 (mtn ) 40

55 следующий импульс, который устанавливает их s нулевое состояние.

Таким образом, каждый импульс с выхода делителя 23 частоты, поступающий через элемент 20 задержки на вход сброса БФЗИ

14, вызывает появление серии импульсов на выходе последнего. При этом временные интервалы между моментом сброса БФЗИ

14 и каждым следующим импульсом, появляющимся на его выходе, удваиваются.

На фиг. 3 а, б, в, r представлены временные диаграммы сигналов на тактовом входе

БФЗИ 14, на выходе БФЗИ 14, на выходе делителя 23 частоты и на выходе элемента

20 задержки соответственно. Число импульсов, поступивших из БФЗИ 14 в счетчик 17 за интервал времени между двумя импульсами сброса на их входах сброса, представляют собой число MF, которое далее записывается в F-ю ячейку многоцелевого регистра 18, определяя значения коэффициентов К4.р и К25.р для соответствующей фазы.

На фиг. 4 изображена зависимость числа MF от периода выходного сигнала делителя частоты. Как видно из графика, благодаря функционированию блока выбора частоты характеристика имеет гистерезис для каждого значения MF, что повышает надежность и точность устройства из-за отсутствия ложных срабатываний схемы. На фиг. 4 Тв — минимальное пороговое значение периода выходного сигнала делителя частоты.

Таким образом, в устройстве повышена точность измерения, Измерение электроэнергии многофазной сети в предлагаемом цифровом измерителе электроэнергии достигается без распараллеливания структурной схемы по числу фаз исследуемой сети, что привело бы к увеличению аппаратурных затрат. Применение введенных цифровых узлов позволяет путем быстродействующего опроса всех фаз измерять суммарную электроэнергию сети, при этом синхронизация умножителя и преобразователя напряжения в код позволяет исключить влияние коммутационных выбросов на точность устройства. Быстродействующий выбор коэффициентов передачи масштабного преобразователя и управляемых делителей частоты отдельно по каждой фазе дает возможность с высокой точностью измерять пофазную энергию, Построение большинства блоков на базе цифровых элементов позволяет при необходимости перевести данную структуру на БИС, так как аналоговые регулировки и подстройки при реализации устройства практически отсутствуют, 5

Использование изобретения позволяет повысить точность измерения по сравнению с известными многофазными счетчиками электроэнергии за счет того, что независимо от величин токов в каждой из и фаз {которые в общем случае могут и существенно отличаться друг от друга) умножитель 5 в предлагаемом цифровом измерителе работает на узком линейном участке своей рабочей характеристики, не превышающем трех (фиг. 5, где 42 и 43 — идеальная и реальная рабочие характеристики умножителя):

Н Р"",„ 3 р умн5 (min )

U умн5 = C0ASl., вх1

tl1gg

При Mr- = 7 в предлагаемом устройстве полный динамический диапазон HF изменения токов по каждой из фаз составляет вх2 ах -ю - (UyMs5, 01 мн5 — СИГНаЛЫ На ПЕРВОМ И ВтОвх1 вх2 ром входах умножителя, пропорциональные фазным напряжению и току) с погрешностью у определяемой на

HF"м" = 3. В тО жЕ ВрЕМя В ПрататИПЕ дпя достижения такого же диапазона умножитель должен работать в диапазоне у н °

HF- = 3, что неизбежно приводит к увеличению его мультипликативной погрешности и возрастанию погрешностей нелинейности и, следовательно, к снижению точности. 8 известных многофазных счетчиках электроэнергии по этим же причинам достижение высокой точности затруднено из-за неидеальности рабочих характеристик умножителей (фиг. 5).

Формула изобретения

1. Цифровой измеритель электрической энергии многофазной сети, содержащий и трансформаторов напряжения, и трансформаторов тока, умножитель и ключ, причем выходы и трансформаторов тока и и трансформаторов напряжения соединены с информационными входами ключа, о т л ич а ю шийся тем, что, с целью повышения точности, в него введены масштабный преобразователь, управляемый делитель частоты, блок индикации, второй и третий ключи, преобразователь напряжения в код, комбинационный сумматор, два многоцелевых регистра, генератор, четыре счетчика, блок выбора частоты, блок формирования заполняющих импульсов, логический элемент 2И, два логических элемента

2И-НЕ, дешифратор, элемент задержки, 13

1647443

10

50

j-входовой логический элемент)И-НЕ, делитель частоты, и управляемых делителей частоты, и регистров, и дифференцирующих цепей и и-входовой логический элемент пИЛИ, причем первый выход первого ключа подключен к первому входу умножителя, а второй его выход через масштабный преобразователь — к второму входу умножителя, выход которого через преобразователь напряжения в код соединен с вторым входом комбинационного сумматора, который выходом подключен к входу первого многоцелевого регистра, а первым входом — к первому выходу первого многоцелевого регистра, выход генератора соединен с.входом записи первого многоцелевого регистра и с тактовым входом блока выбора частоты, через второй счетчик — с входами адреса записи и второго адреса считывания второго многоцелевого регистра и с управляющим входом третьего ключа, а также непосредственно с входом первого счетчика, первый выход которого подключен к управляющим входам умножителя и преобразователя напряжения в код, а второй выход— к управляющим входам первого и второго ключей и входам первого адреса считывания первого и второго многоцелевых регистров и к входу адреса записи первого многоцелевого регистра, выход блока выбора частоты через блок формирования заполняющих импульсов подключен к второму входу логического элемента 2И, выход которого через четвертый счетчик соединен с входом второго многоцелевого регистра и с входом логического элемента jVI-HE, который выходом подключен к первым входам логического элемента 2И, первого и второго логических элементов 2И-НЕ, первый выход второго многоцелевого регистра через дешифратор соединен с управляющим входом масштабного преобразователя, а его второй выход через и регистров — с управляющими входами и управляемых делителей частоты соответственно. младший разряд второго выхода второго многоцелевого регистра через третий счетчик подключен к входу выбора частоты блока выбора частоты. выход переноса комбинационного сумматора соединен с входом второго ключа, выхо и которого через п управляемых делителей частоты и через и дифференцирующих цепей соединены с входами логического элемента п ИЛИ соответственно, выход которого соединен с входом блока индикации, выходы и управляемых делителей частоты подключены к соответствующим п первым входам третьего ключа, первый выход которого через делитель частоты и элемент задержки соединен с входами сброса блока выбора частоты, блока формирования заполняющих импульсов и четвертого счетчика, выход делителя частоты также соединен с вторым входом первого логического элемента 2И-НЕ, выход которого подключен к второму входу второго логического элемента 2И-НЕ, выход которого соединен с входом записи второго многоцелевого регистра и с (и+1}-м входом третьего ключа, выходы которого с второго по (и +1)-й подключены к входам записи регистров с первого по и-й соответственно.

2. Измеритель по и. 1, о т л и ч а ю щ и йс я тем, что блок «ыбора частоты содержит пятый счетчик, инвертор, второй логический элемент 2И, логический злеменпг 3I1 и двэ логических элемента 2ИЛИ, причем тактовый вход блока выбора частоты подключсн к счетному входу пятого счетчик:ка, первый выход которого соединен с первыми входами второго логического элемен TB 2И н логического элемента 3И, выходы которых подключены к первому и второму входам первого логического элемента 2ИЛИ, который выходом подключен к выходу блока р!,! бора частоты и к первому входу в;оро;о логического элемента 2ИЛИ, второй вход которого соединен с входом сброса блэ .; выбора частоты, а выход — с входом сброса пятого счетчика, вход выбора частсты блока выбора частоты подключен через инвертор к второму входу второго логического элемента 2И и непосредственно — к третьему входу элемента 3И, второй вход которого соединен с вторым выходом пятого счетчика.

3, Измеритель по и. 1, о т л и ч а ю щ и йс я тем, что блок формирования заполняющих импульсов содержит второй элемент задержки, счетчик с предварительной уст"новкой и счетчик-распределитель импульсов, причем тактовый вхоц блока формирования заполняющих импульсов подключен к счетному входу счетчика с предварительной установкой, вход сброса которого соединен с входами сброса счетчика-распределителя импульсов и блока формирования заполняющих импульсов, выход которого соединен со счетным входом счетчика-распределителя импульсов, с выходом переноса счетчика с предварительной установкой и через второй элемент задержки— с входом записи счетчика с предварительной установкой, вход предустановки которого подключен к выходу счетчика-распределителя импульсов.

1647443

1647443

1647443

Составитель С. Хромов

Техред М.Моргентал Корректор А. Осауленко

Редактор А. Шандор

Заказ 1396 Тираж 415 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва. Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул,Гагарина, 101 дю

9ки5

Уин 5(иин)

Фиаб 8 .2

У ® У(вакс)