Устройство для вычисления функции аrстg х/у

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в специализированных ЦВМ и вычислителях для определения аргумен-г та комплексного числа и преобразования координат в реальном масштабе времени. Целью изобретения является повышение точности и быстродействия вычисления таблично-алгоритмическим методом. Устройство содержит десять регистров, четыре блока памяти, вычислитель , сумматор, схему ИСКЛЮЧАЮЩЕЕ ИЛИ, триггер и два сдвиговых регистра. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

5 А1 (19) (ll) (g))5 С 06 F 7/548

1.1

1 с d.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТ0РСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

IlQ ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР! (21) 4623822/24 (22) 21.12 .88 (46) 07.05.91. Вюл. У 17 (72) В.А.Волохов, А.Н.Зайченко и И.Ю.йшдт (53) 681. 325 (088. 8) (56) Авторское свидетельство СССР

1319024, кл. (06 Р 7/548, 1986.

Авторское свидетельство ЧССР

tl- 227756, кл. (: 06 F 7/552, 1982. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ arctg Х/Y (57) Изобретение относится к вычис-

Изобретение относится к вычислительной технике и предназначено для ускоренного вычисления функции .arctg х/у в специализированных вычислителях, например преобразователях координат.

Цель изобретения — повышение точности вычисления и быстродействия.

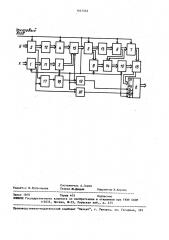

На чертеже приведена структурная схема устройства.

Устройство содержит регистры 1-10, блоки 11-14 памяти, вычитатель 15, сумматор 16, элемент t7 ИСКЛЮЧАИ(ЕЕ

ИЛИ, триггер 18 и два сдвиговых регистра t9 н 20.

Работа устройства основана на использовании следующего алгоритма нахождения оценки фазы вектора Ч) для . различных частей плоскости

2 лительной технике и может быть использовано в специализированных ЦВМ и вычислителях для определения аргумента комплексного числа и преобразования координат в реальном масштабе времени. Целью изобретения является повышение точности и быстродействия вычисления таблично-алгоритмическим методом. Устройство содержит десять регистров, четыре блока памяти, вычислитель, сумматор, схему ИСКЛЮЧАЮЩЕЕ ИЛИ, триггер и два сдвиговых регистра. 1 ил.

С:: агсtg((х//)у) ), если х>0, у70 °

Я

2 + arctg () y ) /) х ) ), если х>0, ус0

))+агс 8()х)//у)), если хс0, уСО;

+2+агсе8()У) /)х(), если хс0, у>о,:

Вычисление отношения аргументов производится по формуле: а 0) а)х) 0 а / J /

)уГ

«)у Софа ) I «у а I x )

)x/

Ф где а — некот орая конс таит а .

Устройство работает следующим образом.

KB aTypHbte составляющие вектора — значения аргументов Х и Y

Х=Ав1п(; Y=Acosg, с соответствующих входов устройства поступают на входы регистров 1

16475 и 2 соответственно. Первым синхроимпульсом, поступающим на тактовый вход устройства в регистры 1 и 2, записываются значения усеченных аргу5 .ментов Х- и Y"-: х*=Х-Ь,, и=к-Л,, где, g (0,1) и Ь, E(),1) — погрешности, вызванные конечной разрядностью регистров 1 и 2. С выходов ре- lp гистров 1 и 2 абсолютные значения усеченных аргументов (Х " и (Y(* поступают на входы блоков 11 и 12 памяти, а знаки h u k аргументов Х" и Y+ (Π— для положительных чисел, 1 — для 15 отрицательных чисел) со знаковых разрядов регистров 1 и 2 — на входы схемы 17 ИСК ПОЧАЛ (ЕЕ ИЛИ.

Количество Р разрядов адресных входов блоков 11 и 12 связано с моду- 20 лем А вектора соотношением:

Pj =log<

Блоки 11 и 12 представляют собой логарифмические преобразователи, выходные данные которых имеют соответ- 25 ственно вид:

c=lcgc(x*I- д-; а 1O82IY*l ь2сi где 2зС(0 1) и С (0 " погреш 3р ности выходных данных блоков 11 и 12, вызванные конечной разрядностью выходов ф ф

35 где / — количество разрядов на выходе блоков памяти.

Вторым синхроимпульсом, поступающим на тактовый вход устройства, в регистры 3,4 и триггер 18 записывают- 4р ся данные с выходов блоков 11 и 12, которые подаются на вычитатель 15.

Этим же синхроимпульсом в регистры 1 и 2 записываются новые зна ения аргументов Х р и Y*.

Вычитатель формирует (+t)-разрядную разность Я выходных данных б =(-1) В (с-1), изменяя знаки операндов с и d под действием управляющего сигнала Ь.

Третьим синхроимпульсом число Е записывается в регистр 5. Число Е", представленное /3 старшими разрядами числа Я, с соответствующих разрядов выхода регистра 5 поступает на адресный вход блока 13 памяти.

Е

Я*=- 29 где 8=)++1-P, 55 4

Ь б(0, 1) — погрешность, вызванная конечной разрядностью адресного входа Р блока 13.

Число З =Я-2 Я"=2 6, представлен3., 9 ное g младшими разрядами числа Я с соответствующих разрядов выхода регистра 5 поступает на вход регистра 9.

На выходе блока 13 формируется грул бая оценка (фазы по алгоритму:

h Р j®% л

2(+i

11 где II, E (О;д+-,) " погрешность, вызванная конечной разрядностью выхода блока 13;

II д; - — цена единицы младшего разряда ко-, л да Чгр

Четвертым синхроимпульсом грубая л оценка фазы (г записывается в регистр 6, а число (в регистр 9. С выходов регистров 6 и 9 эти числа по".ступают на адресные входы блока 14 памяти, причем над разрядов адресного входа подается число, а на осталь" л ные — усеченное значение ц грубой оценки фазы, со старших азрядов выхода регистра 6: л

=(г, 2 р, Ц где (0 — — ) — погрешность выл 2Р+

i званная пренебл режением в Ц

1-р младшими раз рядами 1 „

На выходе блока 14 формируется л поправка 11 к оценке фазы (P, л

tt =-sin2$ 1na- 3, где о 5 6 (О, - -.—,) — погрешность, вы-. н званная конечной разрядностью выходных данных блока 14,.

С

П

2 У+Т вЂ” — — цена единицы младшего разряда поправки, равная цене единицы младшего разряда грубой оценки фазы

Пятым синхроимпульсом значения

"л грубой оценки фазы, и поправки Г1 записываются соответственно в регистры 7 и 10 и подаются на первый и второй входы сумматора 16. На выходе л Ф,л

=ah+-b+(О .

Устройство для вычисления функции

arctg х/у, содержащее первый и второй регистры, первый, второй и третий блоки памяти, вычитатель и элемент ИСКЛЮЧАЮ@ЕЕ ИЛИ, причем выходы первого и второго регистров соединены с адресными входами соответственно первого и второго блоков памяти, первый и второй входы элемента ИСКЛ10ЧАИЩЕЕ ИЛИ . соединены с выходами знаковых разрядов соответственно первого и второго регистров, информационные входы которых соединены с входами соответственно первого и второго аргументов устройства, тактовый вход которого соединен с входами синхронизации первого и второго регистров, о т л и— ч а ю щ е е с я тем, что, с целью повышения точности и увеличения быстродействия, в него введены с третьего

164 сумматора 1б формируется уточненная оценка фазы

h и

=(и

II

=(0 + PP(0 —, — —,— — ) ., фр

12 ) gyt

Нестым синхроимпульсом значение (. . записывается в младшие разряды регистра 8.

Таким образом, цена младшего разIi ряда числа в регистре 8 равна

20 +

В два старших разряда регистра 8 записываются числа h и Ь, имеющие цену единицы П и и /2 соответственно и поступающие с выходов регистра 1 н триггера 18 через сдвиговый регистр 20 с .задержкой в 5 тактов и через сдвиговый регистр 19 с задержкой в 4 такта соответственно. !

На выходе регистра 8 формируется искомая оценка фазы вектора, Формула из о бр ете ния

7555 по десять|В регистры, (етвертый блок памяти, триггер, сумматор и два сдннг >вых регистра, причем выходы первого второго блоков памяти соединены с нформационными входами соответственно третьего и четвертого регистров, выходы которых соединены с входами соответственно вычитаемого и уменьшаемого вычитателя, управляющий вход которого соединен с выходом триггера, выход вычитателя соединен с информационным входом пятого регистра, выходы старших и младших разрядов которого соединены соответственно с адресным входом третьего блока памяти и информационным входом шестого регистра, выходы которых соединены соответственно с информационным входом

20 седьмого регистра и первым адресным входом четвертого блока памяти, выход которого соединен с информационным входом восьмого регистра, выход которого соединен с входом первого сла25 гаемого сумматора, выход и вход второго слагаемого сумматора соединены соответственно с входом младших раз рядов девятого регистра и выходом десятого регистра, информационный

3р вход которого соединен с выходом седьмого регистра и вторым адресным входом четвертого блока памяти, выход элемента ИСКЛНЧА3ЯЕЕ ИЛИ соединен с информационным входом триггера, выход которого соединен с информационным входом первого сдвигового регистра, выход знакового разряда второго регистра соединен с информационным входом второго сдвигового регистра, 40 выходы первого и второго сдвиговых регистров соединены со старшими разрядами информационного входа девятого регистра, выход которого соединен с выходом устройства, вход такто4 вых импульсов котоРого соединен с вхо:дами синхронизации с третьего по десятый регистров, триггера, первого и второго сдвиговых регистров.

1647555

Редактор В.Бугренкова

Заказ 1400 Тирак 403 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Иосква, %-35, Раущская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Укгород, ул. Гагарина, 101

7 мтоAw

Ю Р

Составитель А.Зорин

Техред К.Дидык Корректор Н.Король