Устройство для суммирования массива чисел

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных устройствах обработки цифровой информации. Целью изобретения является расширение области применения за счет осуществления суммирования чисел с разными знаками . Цель достигается тем, что в устройство , содержащее запоминающий блок, сумматор для группового сложения чисел и выходной регистр, введены одноразрядный многовходовый сумматор, постоянный запоминающий блок и параллельный сумматор, а также новые связи. Устройство может суммировать числа в дополнительном и обратном коде. Суммирование чисел с различными знаками осуществляется путем добавления корректирующего кода, считанного из постоянного запоминающего блока по адресу , являющемуся кодом числа отрицательных чисел, к сумме мантисс чисел. 2 ил. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (19) (И) (51)5 G 06 F 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4637444/24 (22) 13.01.89 (46) 07.05.91. Бюл. № 17 (72) С.В.Антонов, Ю.Н.Долгин, Г.И.Васильев и В.В.Храмов (53) 681.325.5(088.8) (56) Авторское свидетельство СССР № 1322261, кл. С 06 F 7/50, 1985.

Введение в кибернетическую технику./Под ред. Б.Н Малиновского.

Киев, Наукова Думка, 1979, с. 127, рис. 37. (54) УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ МАССИВА ЧИСЕЛ (57) Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных устройствах обработки цифровой. информации.

Изобретение относится к вычисли,тельной технике и может быть исполь.— зовано в высокопроизводительных устройствах обработки цифровой информации е

Целью изобретения является расширение области применения за счет осу.— ществления суммирования чисел с разными знаками.

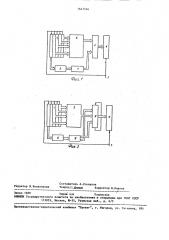

На фиг. 1 приведена структурная схема устройства; на фиг. 2 — вариант построения структурной схемы устройства для суммирования массива чисел в . обратном коде.

Устройство для суммирования массива чисел содержит запоминающий блок 1, сумматор 2 для группового сложения чи2

Целью изобретения является расширение области применения за счет осуществления суммирования чисел с разными знаками. Цель достигается тем, что в устройство, содержащее запоминающий блок, сумматор для группового сложения чисел и выходной регистр, введены одноразрядный многовходовый сумматор, постоянный запоминающий блок и параллельный сумматор, а также новые связи.

Устройство может суммировать числа в дополнительном и обратном коде. Суммирование чисел с различными знаками осуществляется путем добавления корректирующего кода, считанного из постоянного запоминающего блока по ад- с е ресу, являющемуся кодом числа отрицательных чисел, к сумме мантисс чисел.

2 ил.

С:: сел, одноразрядный многовходовый сумматор 3, постоянный запоминающий блок

4, параллельный сумматор 5, выходной регистр 6 и вход 7 синхронизации.

Запоминающий блок 1 представляет собой группу из N n-разрядных регистров или ячеек памяти с возможностью одновременного обращения ко всем регистрам (ячейкам) одновременно и может быть выполнен и в виде ассоциативного запоминающего устройства.

Сумматор 3 предназначен для определения количества единиц в знаковом срезе слагаемых.

Устройство осуществляет суммирование К и-разрядных двоичных чисел, представленных в виде (п-1) -разряд1647556

П-2 п-3 о

2 +q „2 +...+q,„г;

»»-2 n-b o

2 +quay 2 +...+q n2

50 »»2 а +q

» 2

1 » м н-э 6

Ч»» 2 +Ч N> 2 +...+%1»„ 2 исходного массива прибавить число

n+g(o,Nj-»» УЕо,1»Г-г

Р,К (2 +2 +...Ф яйся

Знаковый разряд

+2 ).. ной мантиссы и одного знакового разряда.

В основе работы устройства лежит следующий метод. 5

° Пусть слагаемые массива представлены в виде: и-» о

q((К +q» К +...+q»n К

»»-»»»-2,,о, » 2» К + » гг К + .+ »zn 1 10

Ьf n-2 о

q „К +q „К +...+(1»,» К где К вЂ” основание системы счисления; — коэффициент, принимающий соответствующее значение при 15 представлении чисел в системе счисления с основанием К.

Ддя двоичной системы К=2, q, =»й, lj.

Представим тот же массив слагаемых в двоичной системе разрядности резуль-20 тата, т.е. разрядности n+)log

"1Ео,н(-» n+$00g,74(-2

q»» 2 +q 2 +.. 25 о

+ +q»n )po)INC 2

2n+JQogz N».- + 2" jÖß1 "(2

2 » яр о

+ ° .+qz.,)Åoó,N 2

2 1 » » М2 о Ъ)Ео,wf Поскольку разрядность исходных слагаемых п, то все отрицательные чис-З5 ла при представлении их в обратном или дополнительном кодах разрядности

n-» п+)1од И» в позициях, начиная с 2 по 2 " 1 Ч " будут иметь единиць», которые назовем фиктивными, так как 40 они отсутствуют в исходных кодах слагаемь»х, Пусть отрицательных чисел в массиве будет,К. Тогда для получения правильного результата сложения разнознаковых чисел необходимо к сум- 45 ме мантисс

При получении сум»чь» массива разнознаковых слагаемых очевидно следует учитывать форму представления слагаемых.

Так, если слагаемые представлены в дополнительном коде, все единицы переноса, превышающие разрядность

n+jlog N(, игнорируются.

Если числа представлены в обратном коде, все единицы переноса, пре,вышающие разрядность n+glog NP, циклически в соответствии со своими позициями складываются с младшими разрядами полученной суммы.

Преобразуя значение Р,, можно получить в следующем виде

«1ео,нC 38og» - о

Р =2 К ° (2 +2 +...+2 ) при этом К пробегает в общем случае значения от 1 до N. Поскольку любое

И число Р», кратно 2, для получения окончательной суммы необходимо знать числа

geog, М (gEog,НС-»

Р„=к (2, +2 +...+2 ), которые можно хранить в памяти. При этом для считывания из памяти нужного числа необходимо знать число единиц в знаковом срезе (т.е. число отрицательных слагаемых), которое является адресом числа Р .

Для получения окончательной суммы необходимо суммировать сумму мантисс исходных слагаемых с числом Рк, сдвинутым относительно этой суммы íà и-1 разряд влево.

Устройство работает следующим об-, разом..

Разрядные срезыслагаемых »оступают на соответствующие входы сумматора 2, а разрядный срез знакового разряда - на вход сумматора 3, формирующего код количества единиц в этом срезе, т.е. количество отрицательных чисел в массиве, Данный код является (2 glog N))разрядным, при этом если слагаемые представлены в дополнительном коде, то в разрядах постоянного запоминающего блока 4 (Д1оВ Jf+1)-го по (2 )lo32N()-й содержатся нули, т.е. эти разряды не используются. При суммировании чисел в обратном коде параллельный сумматор 5 должен содержать цепь циклического переноса (Фиг.2). Результат суммирования заносится в регистр 6 по заднему фронту импульса синхронизации по. входу 7.

Рассмотрим для примера суммирование чисел в дополнительном коде. Сум5 1647 1 определяется следующим ма мантисс образом

1И1 1О1

11Π— — 11

101 1

111

111 ю- - ——

0 1 1 — ---"- - 10101

1О1 - " ——

101

111

111

100001

15

Так как разрядность результата равна семи, то на выходе сумматора 2 получают число 0.100001.

; Так как в массиве садержится три отрицательных числа, то на выходе сумматора 3 будет сформирован код 011, т.е. 3 в двоичном коде ° Этот код является адресом дпя считывания Рэ,,которое является суммой фиктивных единиц и знаков из блока 1, т.е. будет считано число Р =1101. Оконча тельно сумма массива определится как; 0. 100001

1. f01

1О.ОО1ОО1 = +9 единица переполнения игнорируется.

Формула изобретения

Устройство для суммирования масси35 ва чисел, содержащее запоминающий блок, сумматор для групповогб сложе-. ния чисел и выходной регистр, .причем выходы групп одноименных разрядов слагаемых запоминающего блока соедипены с соответстнующими входами сумматора для группового сложения чисел, отличающееся тем,что, с целью расширения области применения эа счет осуществления суммирования чисел с разними знаками, устройство дополнительно содержит одноразрядный многовходовый сумматор, постоянный запоминающий блок н параллельный сумматор, причем выходы знаковых разрядов слагаемых запоминающего блока соединены с входами одноразрядного многовходового сумматора, выход которого соединен с адресным входом постоянного запоминающего блока, разряды выхода сумматора для группового сложения чисел соединены с соответствующими разрядами первого входа параллельного сумматора, разряды второго входа которого с первого rro )log MP-й

2 .соединены с разрядами выхода постоянного запоминающего блока с ()log Nj+1)-ro по (2 1оя И()-й, а разряды с п-го по (n+Jlog2N(-1)-й соединены с разрядами выхода постоянного запоминающего блока соответственно с первого по )log>Nf-й, где

N — число слагаемьж, а n — разрядность слагаемых, выход параллельного сумматора соединен с инйормацнонным входом выходного регистра, выход которого является выходом результата устройства, вход синхронизации запоминающего блока соединен с входом синхронизации выходного регистра и подключен к входу синхронизации устройства, свободные разряды входов параллельного сумматора соединены с шиной нулевого потенциала устройства.

1647556

Составитель А.Степанов

Техред И.Дидьщ .. Корректор Н. Король у"

Редактор В.Бугренкова

Заказ 1400 Тира к 404 Подписное

8HHNIH Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Иосква, Ж-35, Раушская наб,, д. 4/5

Производственно-издательский комбинат "Патент", r. Укгород, ул. Гагарина, 101