Устройство для вычисления кратного интеграла

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для вычисления кратного интеграла от одномерной решетчатой функции с постоянным шагом дискретизации, в частности , может быть использовано в качестве блока в устройстве идентификации или имитации линейных стационарных объектов. Цель изобретения - повышение точности. Устройство для вычисления кратного интеграла содержит интеграторы , выходной блок, состоящий из регистров, узла суммирования и узла умножения на постоянный коэффициент . Цель достигнута за счет коррекции результата интегрирования на основании значений интеграла, вычисленных на (1-1)-м шаге, где i - крат-t ность интегрирования. 3 ил. с S

СООЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) Ai (51)g С 06 F 7/64

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4694272/24 (22) 02.03.89 (46) 07.05.91. Бюл. Ф 17 (71) Институт проблем моделирования в энергетике АН УССР (72) Н.А.Максимович (53) 681.8 (088.8) (56) Коган Б.Я. Электронные моделирующие устройства и их применение для исследования систем автоматического регулирования. — И.: Гос. издво физ.-мат. л-ры, 1963, с. 371, рис. 213.

Авторское свидетельство СССР

Ф 1361510, кл. С:)6 F 7/64, 1985. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КРАТНОГО ИНТЕГРАЛА (57) Изобретение относится к вычиспиИзобретение относится к вычислительной технике и предназначено для вычисления кратного интеграла от одномерной решетчатой функции с постоянным шагом дискретизации, в частности, может быть использовано в качестве блока в устройствах идентификации или имитации линейных стандартных объектов.

Целью изобретения является повышение точности.

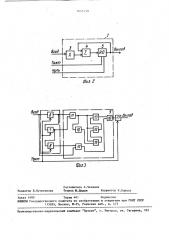

На Фиг. 1 изображена структурная схема устройства; на фиг. 2 — возможный вариант реализации схемы интегратора; на фиг. 3 - схема выходного блока для случая вычисления четырехкратного интеграла. тельной технике и предназначено для вычисления кратного интеграла от одномерной решетчатой функции с постоянным шагом дискретизации, в частности, может быть использовано в качестве блока в устройстве идентификации или имитации линейных стационарных объектов, Цель изобретения — повышение точности. Устройство для вычисления кратного интеграла содержит интеграторы, выходной блок, состоящий из регистров, узла суммирования и узла умножения на постоянный коэффициент. Цель достигнута за счет коррекции результата интегрирования на основании значений интеграла, вычислен- Я ных на (i-1)-м шаге, где i — крат. ность интегрирования. 3 ил.

Устройство (фиг. 1) состоит из (1. — кратность интегрирования) интеграторов 1 и выходного блока 2.

Интегратор (фиг. 2) состоит из умножителя 3 на постоянный коэффициент, сумматора 4 и регистра 5.

Выходной блок для случая i=4 (фиг. 3) состоит иэ трех регистров 6 — 8, узла 9 суммирования, содержащего регистр 10 сдвига ка три бита, шести сумматоров 11 — 16, н узла 17 умножения на постоянный коэффициент.

Устройство работает сле ующнм образом.

Перед началом пронесся иит грирования обнуляют вых нные j) ãècтры 5

1647559 всех интеграторов 1 и регистры 6 — 8.

С приходом первого тактового импульса начинается процесс интегрирования.

При постоянном шаге дискретизации точ5 ное значение кратного интеграла на выходе будет получено с задержкой на тактов относительно такта поступления на вход устройства очередного значения интегрируемой решетчатой функции.

С математической точки зрения принцип действия устройства основан на использовании априорной информации D гладкости интегрируемой функции. Так, исходная функция имеет степень гладкости не хуже скачка, после первого интегратора — не хуже линии, после второго — не хуже параболы и т.д., что позволяет построить квадратурную формулу, не имеющую методической погрешности.

Каждое дискретное значение входно- 25

ro сигнала проходит через цепочку из последовательно соединенных интеграто-!. ров 1 и поступает на вход выходного блока 2. В регистрах 6 — 8 в каждый момент времени хранится несколько (по числу регистров в групне) последних дискрет входного сигнала выходного блока 2, которые с различными весовыми коэффициентами суммируются в узле 9, затем умножаются на постоян-З5 ный коэффициент в узле 17 и образуют очередную дискрету выходного сигнала устройства.

Выбор расчетной формулы осуществлен на основании экспериментальных исследований.

Узел 9 суммирования осуществляет сложение с учетом весовых коэффициентов, вычисляемых по формуле Р (Z)=

3 ) 1

=(— 1) D (- — ) где D=Z--- j =i-1 .

Й

Z-1 dZ

Формула из обретения

Устройство для вычисления кратного интеграла, содержащее i интеграто-. ров, причем тактовый вход устройства соединен с тактовыми входами интеграторов, информационный вход устройства подключен к входу первого интегратора, вход j-го (j=l, i-1) интегратора соединен с информационным входом ()+1)-го интегратора, о т л и ч а ющ е е с я тем, что, с целью повышения точности, в него введены i-1 регистров, узел суммирования и узел умножения на постоянный коэффициент, причем выход i-ro интегратора соединен с информационным входом перво-.. го регистра, выход j-го (j=l, i-1) регистра соединен с j ì входом узла суммирования, выход которого соеди . нен с информационным входом узла ум" ножения на постоянный коэффициент, выход которого соединен с выходом устройства, тактовый вход устройства

4 соединен с тактовыми входами регист" ров и узла умножения на постоянный

1соэффициент, выход j-ro (j=l, i-2) регистра соединен с информационным входом ()+1 ) -го регистра .

Составитель А.Чеканов

Техред И.Дидык Корректор Н.Король

Редактор В. Бугренкова

Заказ 1400 Тирам 401 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113/35, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101