Микропрограммное устройство управления с контролем

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИНas Я0(, I

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

f (21 ) 4691641/241 469254 6/24 (22) 17 05.89 (46) 07,05,91. Бюл. У )7 .,(71) Ленинградский электротехнический институт им, В.И.Ульянова (Ленина) (72) А.С.Календарев, В.П.Крюков, И.Ю.Матвеев, Д,В,Пузанков и И.БД1апиро (53) 681.325(088.8) (56) Авторское свидетельство СССР

У 966694, кл. С 06 F 9/22, 1980.

Авторское свидетельство СССР

Я 1411743 кл. G 06 F 9/22, 11/00, 1987 ° (54 ) МИКРОПРОГРАММНОЕ УСТРОЙСТВО

УПРАВЛЕНИЯ С КОНТРОЛЕМ (57) Изобретение относится к вычислительной технике и может быть использовано для построения микропрограммируемых микропроцессорных систем.

Целью изобретения является повышение

Изобретение относится к вычислительной технике и может быть использовано для построения мнкропрограммируемых микропроцессорных систем.

Целью изобретения является повышение достоверности функционирования устройства за счет обеспечения возможности самоконтроля.

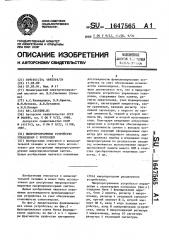

На фиг,l представлена функциональная схема устройства; на фиг.2функциональная схема блока формирования адресов; на фиг.З и 4 - примеры фрагментов граф-схем алгоритмов (1)5 G 06 F 9/22, 11/00, 9/34

2 достоверности функционирования устройства за счет обеспечения возможности самоконтроля. Поставленная цель достигается тем, что в микропрограммное устройство управления контролем, содержащее блок памяти, регистр микрокоманд, узел формирования адреса, сигнатурный анализатор, схему сравнения, введены регистр эта лонной сигнатуры, с первого по третий элементы И, первый и второй элементы HE первый и второй мультиплексоры. Благодаря введенным аппаратным средствам в устройстве обеспечиваются возможность снятия с выходов устройства значений сформированных сигнатур для последующего анализа; анализ признака ошибки и изменения хода микропрограммы по результатам анализа;.возможность использования микропрограммной памяти вместо ПЛМ в качестве преобразователя эталонных сигнатур. 4 ил, (I CA) микропрограмм реализуемых устройством

Микропрограммное устройство управ.ления с сигнатурным контролем (фиг.1) содержит блок 1 формирования адреса, блок 2 памяти, регистр 3 микрокоманд, регистр 4 эталонной сигнатуры, третий элемент И. 5, второй элемент НЕ б, вход 7 кода условия устройства, вход 8 синхронизации устройства, выход 9 микроопераций регистра

3 микрокаманд, выход 1О сигнатуры регистра 4 эталонной сигнатуры.

1б475б5

Блок формирования адреса (фиг.2) содержит узел 1 формирования адреса, сигнатурный анализатор !2, схему

13 сравнения, первый и второй мульти-, .плексоры 14 н !5, первый элемент.

НЕ 16, первый и второй элементы И !7 и !8, кроме того, на фиг..2 обозначены: выход !9 управления тестированием и вьиод 20,, признак анализа логи- !(1 ческого условия регистра микрокоманд„ вьиод 21 поля кода инструкции регист«з микрокоманд, выход 22 поля адреса регистра микрокоманд, выход 23 адреса блока формирования адреса.

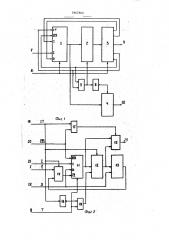

Фрагменты ГСА (фиг..З, 4) содержат операторные, условные и конечные вершиные

Устройство работает следующим образом. 2О

Условные переходы при !ТО могут быть осуществлены по значению признака на входе 7 устройства, Его различным значениям соответствуют различные трассы контролируемого участка микро- 25 программы. Код, выработанный на вьиоде блока 1 Формирования адресов,.поступает на адресный вход блока 2 памяти, из которого при наличии сигнала выборки кристалла осуществляется счи- go тывание очередной микрокоманды (МК).

При запрете считывания из блока 2 памяти на вход разрешения регистра 4 эталонной сигнатуры поступает сигнал, который разрешает запись кода с выхода блока 1 в регистр 4 эталонной сиг натуры, Таким образом, в режиме выдачи сигнатуры в регистр 4 записывается значение сигнатуры на заданном . контролируемом участке. С выхода ХО сигнатура может быть считана для анализа пользователем, Узел !! Формирования адреса выпол-. няет Функцию Формирования адресов микрокоманд. Код адреса следующей 45 микрокоманды вырабатывается на выходе узла !1 Формирования адреса и через мультиплексор 15 поступает на вьиод

23 блока l .

В качестве узла 11 может быть использована БИС И804ВУ4.

Сигнатурный анализатор 12 работа ет по параллельному принципу действия и содержит поразрядные триггеры и сумаматоры по модулю два, а также сумматоры по модулю два в цепи обратной связи. Сигнатуриый анализатор предназначен для получения сигнатур последовательности адресов, формируе" мьи на вьиоде узла 11.

Работа блока 1 формирования адреса осуществляется следующи образом, При переходе значения сигнала 1Т из единицы в ноль, сигнатурный анализатор 12 устанавливается в начальное состояние (например, в единичное).

По фронту синхроимпульса Т в узле !! начинает вырабатываться адрес следующей микрокоманды, который поступает на информационный вход сигнатурного анапиэатора !2 и на вход мультиплексора 15. В случае TT Q синхровмпульс проходит через элемент

И 18 на вход синхронизации сигнатурного анализатора, который срабатывает по cреэу синхроимпульса. Таким образом, при 1ТО, в сигнатурном анализаторе !2 осуществляется свертка кодов адресов МК„ вырабатываемых иа вьиоде узла !1, коды адреса через мультиплексор 15 поступают на выход

23 блока Формирования адреса, Условные переходы при !Т=О осуществляются по значению признака иа входе 7 блока 1, Их различным значениям соот« ветствуют различные трассы контролируемого участка микропрограммы, а следовательно, различные сигнатуры контролируемого участка, формируемые в сигнатуриом анализаторе 12. Каждой из возможных трасс соответствует своя эталонная сигнатура S . Здесь

tI

D — - номер контролируемого участка микропрограммы, р - номер трассы контролируемого участка. При !T=l, ССЕ=О в блоке осуществляется режим сравнения полученной сигнатуры с эталонной. В этом спучае сигиатурный анализатор !2 переходит в режим хранения полученной на предыдущем такте сигнатуры (носколъку синхроимпульс на его синхрозход не проходит}. На вход 2! блока 1 подается код инструкции второго типа, при которой на вход

22 блока подается код эталонной сигнатуры, Значение .эталонной сигнатуры поступает на второй вход схемы

13 сравнения и сравнивается с находящимся на первом входе кодом сигнатуры, сформированным в сигнатурном анализаторе !2. Результат сравнения определяет направление ветвления из текущей мнкрокоманды - код адреса следующей микрокоманды на выходе

23. Таким образом, в режиме сравнения код адреса следующей микрокоманды

I 647565

35

45

50 зависит от того, совпали лн коды полученной и эталонной сигнатур или нет.

При lTI, CCEl в блоке 1 осуществляется режим выдачи сигнатуры. Сигна турный анализатор 2 находится в режиме хранения, сформированная сиг натура через мультиплексор 35 поступает.на выход 23 блока ) .

На фиг.З и 4 представлен фрагмент

ГСА, ° реалиэуемый микропрограммным устройством управления с сигнатурным контролем. Здесь использованы следующие обозначения: 0„ - конечная пои следняя микрокоманда n-.ro контролируемого участка, содержащего р раэ п n личных трасс ° С,. ° .С - микрокоманда, реализующая в пре лагаемом устройстве режим сравнения с эталонными л и ь+ сигнатурами 8,...,S . О, - начальная (первая) мнкрокоманда (n+I)-го контролируемого участка. В" - микрокоманда, реализующая в предлагаемом устройстве режим выдачи полученной сигнатуры на выход устройства, Z— результат сравнения схема 33 сравнения.

Формула изобретения

Микропрограммное устройство управления с контролем, содержащее блок памяти, регистр микрокомаид, узел формирования адреса, сигнатурный анализатор, схему сравнения, причем выход блока памяти соединен с информационным входом регистра микрокоманд, выход поля управления формированием адреса которого соединен с входом кода операции узла формирования адреса, выход которого соединен с информационным входом сигнатурного анализатора, выход которого соединен с первым входом схемы сравнения, выход паля адреса регистра микрокоманд соединен с информационным входом узла формирования адреса и с вторым входом схемы сравнения, выход призна ка анализа логического условия регистра микрокомаид соединен с входом разрешения анализа логических условий узла формирования адреса, вход синхронизации устройства соединен с

25 входами синхронизации узла формирования адреса и регистра микрокомаид, выход поля микроопераций которого подключен к выходу микроопераций устройства, о т л и ч а ю щ е е с я тем, что, .с целью повышения достоверности функционирования за счет обеспечения возможности самоконтроля, дополнительно содержит первый и второй мультиплексоры, с первого по третий элементы К, первый и второй элементы НЕ, регистр эталонных сигнатур, причем выход признака управления тестированием регистра микрокоманд соединен с первыми входами первого и третьего элементов И, входом разрешения работы сигнатурного анализа-., тора, управляющим входом первого муль" типлексора, входом первого элемента

НЕ, выход которого соединен с первым входом второго элемента И, выход которого соединен с входом синхронизации сигнатурного анализатора, выход которого соединен с первым информа- . ционным входом .второго мультиплексора, выход которого соединен с адресным входом блока памяти и с информационным входом регистра эталонных сигнатур, выход которого соединен с выходом сигнатур устройства, выход признака анализа логического условия регистра микрокоманд соединен с вторы" ми входами третьего и первого элементов И, выход первого элемента И соединен с управляюшим входом второ- го мультиплексора, выход третьего элемента И соединен с входом выборки блока памяти и с входом второго элемента HE выход которого соединен с входом синхронизации регистра эталонных сигнатур, вход логического условия устройства соединен с первьм информационным входом первого мультиплексора, выход которого соединен с входом логического условия узла формирования адреса, выход которого соединен с вторым информационным входом второго мультиплексора, вход сиихронизации устройства соединен с вторым входом второго элемента И, выход схемы сравнения соединен с вторым ин- формационныч входом первого мультинлексора.

1647565

Г=0

ССЕа1

ТТ1

ССЕФО аф

ЖО

Фиг Э

Составитель А.Сопжин

Редактор В.Бугренкова, Техреду.яндык Корректор Л.Патай

ЗаКаз 1401 Тираж 420 Подписное

ВНИИПИ Государственного комитета по изобретениям и открьггиям прн ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101