Устройство для цифровой фильтрации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть испольчовано в вычислительных системах , Аункционирукщих в реальном масштабе времени. Цель изобретения - расширение области применения за счет выполнения нелинейной фильтрации комплексных сигналов. Поставленная цель достигается за счет того, что в состав устройства входят блок 1 синхронизации, К вычислительных блоков (К - длина обрабатываемой последовательности ) 2{ -2 к и блок 3 комплексного умножения. 4 ил.

09} Ol) СООЭ СОВЕТСИИХ

СОЦИАЛИСТИЧЕСНИХ . РЕСПУБЛИН

ОПИСЛНИЕ, ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОЩРЬ ТИЯМ

ПРИ ГКНТ СССР (21) 4620417/24 (22) 14.12.88 (46) 07.05.91. Бил. Р 17 (72) С.В.Омельченко и П.В.Сахон (53) 681.32(088.8) (56) .Авторское свидетельство СССР

Р 1211748, кл. 0 06 Р 15/31, 1986.

Авторское свидетельство СССР

Р 1325511, кл. G 06 Р 15/353, 1987. (54) УСтРойстВО Для ЦИФРояой ФИЛ}.тРАЦ}6} (57) Изобретение относится к вычисли(Я)5 (: 06 Г 15/353, Н 03 Н 21/00

2 тельной технике и.монет быть использовано в вычислительных системах, функционирующих в реальном масштабе времени. Цель изобретениярасширение области применения за счет выполнения нелинейной фильтрации комплексных сигналов. Поставленная цель достигается за .счет того, что в состав устройства входят блок

1 синхронизации, К вычислительннх блоков (К - длина обрабатываемой последовательности) 2 -2 к и блок 3: комплексного умножения. 4 ил.

1647592

Пзо()ретение относится к вычислительной технике и может быть использовано в вычислительных системах, функционирующих в реальном масштабе времени.

Целью изобретения является расши- рение области применения за счет выполнения нелинейной йильтрации комплексных сигналов. 10

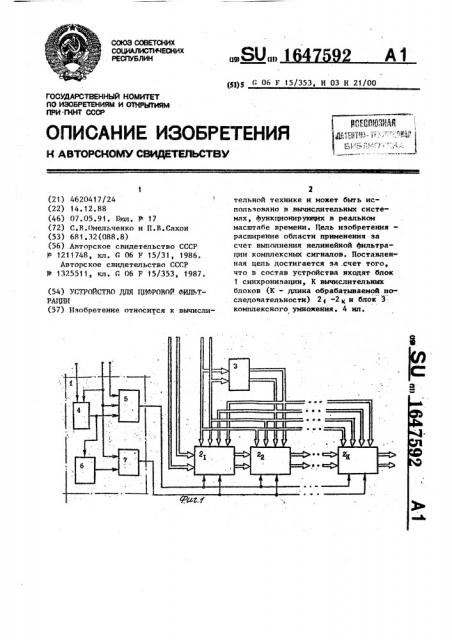

На фиг.1 приведена схема устройства; на фиг.2 — схема вычислительного блока; на йиг.3 — схема блока комплексного умножения; на йиг.4— схема умножителя комплексных чисел. 15

Устройство для цифровой йильтрации (фиг.1) состоит из блока 1 син,хронизации К, вычислительных блоков

21.. 2 к (где К вЂ” длина входной последовательности) и блока 3 комплек- 20 сного . умножения. Блок 1 синхронизации содержит счетчик 4, коммутатор

5, дешифратор 6 и эпемент ИЛИ-НЕ 7. каждый вычислительный блок 2 ...2к (фиг.2) содержит узел 8 постоянной па- 25 мяти коэффициентов, регистр 9 коэйАициентов, группу умножителей

10 ...10,« комплексных чисел, сумма-. торы 11 и 1.2, регистры 13 и 14, мультиплексор 15.

Блок 3 комплексного .умножения (фиг.3) содержит 2d регистров 16»...

16,«, 17 ...17,(и группу умножителей

18, 19 ° .,19)) комплексных чисел, 201... 211, 2 1 ° .. 21 .

Умножитель комплексных чисел (фиг,4) содержит умножители 22-25,. вычитатель 26 и сумматор 27, Устройство работает следующим образом. 40

30 э )

>

Устройство работает следующим образом. .45 В исходном состоянии регистр 9 коэффициентов, первый 13 и второй 14 регистры всех вычислительных блоков

2 < 2ц, первые 16(16 «и вторые

17 ...17 регистры блока 3 находятся

50 в нуле. Па первый и второй инйормационные входы устройства. постоянно подается код "0", на тактовый вход поступают тактовые импульсы. На тре I тьи,и четвертые информационные входы устройства поступают отсчеты входной последовательности в виде кодов, «соответствующих вещественной и мнимой частям фильтруемого сигнала, со скоростью одного отсчета на такт

В

+ КеИ ХшС) где

Лредварительно рассмотрим работу умнонителя комплексных чисел. Выполнению операции комплексного умножения соответствует выражение:

В С = (ReB + j XmB) х х (ReC + j ImC) ReB ReCФ

ХшВ ХшС + 3 (ReC ImB +

4 I

ReB КеС вЂ” код реальной (синфазной) составляющей комплексных сигналов В и С соответственно;

ImB, ImC — код мнимой (квадратурной) составляющей комплексных сигналов

В и С соответственно.

На первый, второй, третий и четвертый входы умнох(ителя поступают соответственно следующие сигналы: ReB, ImB ReC ImC.

На первом умножителе 2? производится умножение ReB ReC на втором умножителе 23 — ИеС ImB, на третьем умножителе 24 - ReB ImC на четвертом умножителе 25 — ImB ImC. Вычитатель 26 кодов производит операцию вычитания ReB ReC - ImB ImC u выдачу первого выходного кода. Сумматор 27 производит операцию суммирования ReC ImB + ReB ХшС и выдачу второго выходного кода.

При выполнении нелинейной фильтрации одномерных комплексных сигналов согласно йормуле

К

y(n) =.,, «x(n-:)+)) w(j) +I

J =K

+ „ х(п-3+1) х(п-1+3 + 1) х

1 -"!

3 — j+1) x(n-j+j +1) х(п — j +

1647592

TaI;= ™его из яч=йкк с адресом К счи%/ тываются коэЫ)ици(нты w(lc» +1 }, де w(-)) I(> j} w(j 1) >R{1

k), w(1,0,О), (е(),,0),...,)(.1, k рые в течение всей операции фиксируются в " åãèñòðå 9 коэЬЬициектаеЧерез промежуток времени, равный по крайней мере одному такту,,с момента подачи сигнала "Одномерная обработка" на вход умкожителя !0 вычислительного блока 2 со скоростью отсчетов на такт начинают одновременно поступать

15 Отсчеты входной поспедоватепьности х(1 е ° ° еx(j} x(j) ех(1) x(j 1) )1 ° е °

Х()) Х(1 1 )»ее ° R>(.) Х()) Х()}

?.(j) х{1) x(j-k ), x(j), x(j-1} x(I-1),...,х(1) хЦ-k ((} х(1-k ), где

2О принимает значекче от 1 до К и изменяет свое значение на единицу с каждым приходом следующего импульса тактовой частоты.

С целью упрощения описания даль25 нейщей работы определяют базовую операцию A,ïpè которой формируется повторяющаяся сочокупность действий„ выполняемых в течение одного такта в вычислительном блоке 2ее

Базовая операция выполняется следующим образом.

В исходный момент времени в первом 13 и втором 14 регистрах результатов хранятся некоторые промежуточные результаты КеЬ1 и ХщЬ, а операнды КеА, ImA>,Re(Aj, A> ), Хл(А;,А>, },...,Re,А, А , А i),...,Re(A>, А1 (, А Ptt} Хл1)(Аj Аj „., Aj I,R) поступают ка третьи и четвертые входы умножителей 101 блока 3,, ка первые и вторые входй которых поступают коэффициенты, I

+ Хлх(1) ° Rex(j — 1 } (3) 40

Выходные сигналы, идущие на третий и четвертый ик(1)ормационные входы устройства, к полученные выходные отсчеты первой и второй групп с умножителей блока 3 подаются на входы умножителей 101...10 каждого из вычислительных блоков 2 ... 2 к.

Иод воздействием сигнала "Одномерная обработкз", поступающего на вход задания режима работы устройства, на выходе элемента ИЛИ-HH 7 формируется уровень логического "О", передаваежй на управляющий вход мультиплексора 15. Под воздействием этого же сигнала "Одномерная обр аботка" на выходе коммутатора 5 припускается код числа К, передаваемый на адресные входы узлов постоянной памяти 8 все блоков 2 ..е2!, в резуль45 ф Зв

Rew(j }, Хпй(1) где

I г

1

R. x(), Iw (u), y = 1,...,Nj, которые записываются соответстве. ко в первые 161... 1() и вторые 171 е .. 17 ф регистры сдвига блока 3, где с помощью умножителей 18, 19),, 19), 20t...20, !1<...21- происходит комплексное умножение с получением результата в виде реальной и мнчмой составляющих, Выходные отсчеты на умножителях

191...19() (первой группы) можно представить в виде:.! 1

Rex(j, 1 ) = Кех(1) Rex(j —. 1 ) 1 . 1

Х (3} .Х- (1 j ) злчх(),1 ) = Кех(1) Imx(j — i ) +

Полученные выходные отсчеты попарно перемкожаются между собой умкожителями 20 1... 20, 21 1... 21, на выходах которых также выделяется реальная и мнимая составляющие:

tt a

Rex(j, 1, j ) = Rex (j. j ) ) It I х Rex/ j — 1 } — Хпи(i(, 1 ) ° IIIIx(j,. я

) е .у

Хтчх(1. 1, j ) = Rex(j, j ) Хщх(1

П ° ..t.... II

) + Хщх(ч, j ) Rex(j — j ), (4) Г . -+

Rew(j) = LRew(j), Rew(j,О), Rew(j,1),... Rew(j,k), Rew(з,О,0),Rew(j,1,0),...

Rew(j,k, О), Rew(j,0, 1),..., Rev(j, k, k ));

Ie4(i) = (Ь»е()), 1еее(1,0), i (j 1)...,,IIIII,r(j, 1 ), 1647592 (5}

\ 1

+ Imw(j) Rex(n-3+1) 20

30

+ 1-1" ))1

n-k N

} Хп jx(n

j °

+1-k) х(п35 (j k, k

1) ° x(n — 3

ImCd = Rew

1 + (6) + 1, k +.3 ") (8) Imw(3, 0,0,), Imw(3, 1, О),..., Imw(j, k, О), Imw(j,0,1),.. ° °

Imw(j, k,,k )j.

Затем в умножителях 101...10(Формируются произведения комплексных чисел.10

Так, для умножителя 10 4 справедливо

Rei = Rew(j) Rex(n-1+1) — 1гп (3 ) ° Ijjjx (n-3+1) 1

Ф

ХлС = Rew(j) Imx(n-3+1) + а для умножителя 10

ReCg = Rew(j, k, k ) Re(x(n-j + 1а к

- k ) x(n-3+1-k ) х(п-j +

+ 1}) — Imw(j, k,,k ) Im(x(пю

+ t) х (n-j+1-k ) ° x(n - j + е Ч

-.1+1 — k )1 + I (j, k, k ) Re fx(n — j + 1) ° x (nи 140

j + 1 k ) ° x(n 3 + 1 k )J) причем реальные и мнимые составляющие раздельно подаются на первые 11 и вторые 12 сумматоры, соответственно. Одновременно с выходов первого

13 и второго 14 регистров результата с вычислительного блока 2 на вто-. рой информационный вход мультиплексора 15 выцаются промежуточные результаты КеЬ1. и ХтЬ )(, которые (поскольку на управляющий вход мультиплексора 15 подан логический "О") передаются на входы первых l1 и вторых 12 сумматоров соответственно.

Первый 11 и второй 12 сумматоры формируют суммы

1 ,(, ReC + Reb 1, О, Imi. ° + Imb

1! Ф, 1 1 которые с приходом импульсов тактовой частоты записываются в первый

13 и второй 14 регистры результатов..

Рассмотрим формирование произвольного отсчета y(n) выходной последовательности согласно выражению

К э ° — ьTr у(п) = . „х(п-3+1) ° w (j) (7) дФ4 где x(i) = (x(j), x(i,О),x(j,1),..., x(j,k ), x(j,0,О), х(3,1,0),..., x(j, k, 0}, x(j,0,1),..., x(jR R k )

w(j) = fw(j), w(j,О),w(j,1),..., w(3 k ), w(l О, О,), w(3,1,0),...,w(3,k О), w(j,0,1),...,w(j,k, k ) Такт n-k = 1. На первый и второй .входы умножителя 10 поступают новые входные отсчеты х(п-k+1).

В вычислительном блоке 21 выполняется базовая операция А, в результате которой сумма

y(n) = х(п - k + 1) w(k) +х (n - k+

+1) x(n "k- j +1) ° w,(k, К К

k + j ) +,." х(и1 -О 3"= О

-k+1) x(n-k+1- j ) x(n-k+1" j -j ) w(k, k+

° I ° к записывается в первые 13 и второй 14 регистры результатов вычислительного блока 2 .

Такт п-k+2. На первый и второй входы умножителя 10(поступают новые входные отсчеты х(п-k+1). В вы1647592 числительном блоке 2 выполняется базовая операция А, результате которой сумма у (n) = у,(n) + x(n-k+3).w (k-1) (9) записывается в первый 13 и второй 14 регистры результатов вычислительно- 10

rn блока 2д, Такт п. В блоке 3 < выполняется базовая операция, в результате которой окончательное значение

У„() = y„(n) + x(n) М "(1) (1О) е= 35

f(.

+ 1) w(1, j) +,, x(m—

) д e =-о

1, f

1+1,1,п — j+1,1)" 40

)(w(1, 1,, j )+

Ь;

+ «,, » x(m — 1

„ 1 -1 Е - Е"1 1 45 н

1, и- j+1, j,) ) (11) У

f,j ) =

) гдеx(m — 1+ 1,1, n — j +

=x(m-1+ 1, 1, n— - j+,с Г и

+ 1, j ) х(m — (1 — 1 ) + 1, n — -..

I (Л 1)+ 1)1

mn =k k+1 N. записывается в первый 13 и второй

14 регистры результатов вычислительного блока ?1(, откуда поступает на 20 выход устройства.

Таким же образом выполняется фор» мирование других отсчетов у(1) с той лишь разницей, что формирование результата и вычислительном блоке 24 происходит в такте i-k+1, а в вычислительном блоке 2к — B такте 1, тем самым осуществляется корреляция одномерных нелинейных сигналов.

При выполнении нелинейной фильтра- 30 ции двумерных комплексных сигналов согласно выражению

k f(y(mfn) =,.,(»,х(ш — 1 + ", и — 3 +

При этом указанные коэААициенты получают в блоке 3 способом, аналогичным описанному для одномерной нелинейной циАровой фильтрации, Устройство работает следуюр)им образом.

F исходном состоянии счетчик 4 (по модулю k) обнулен. Затем на вход задания режима работы устройства поступает сигнал "Двумерная обработка", под воздействием которого счетчик 4 начинает реагировать на поступающие на его вход импульсы тактовой частоты, осуществляя их счеr по модулю k.

Под воздействием этого же сигнала

"Двумерная обработка " на вход коммутатора 5 пропускается содержимое счетчика 4, передаваемое затем на адресный вход узлов Я постоянной паJ" мяти. В результате этого в течение такта с номером Т (где Т вЂ” 1, 2,...) таким, что Т = 1 из ячейки узла Ят постоянной памяти, с адресом 1-1 происходит микрооперация считывания вектора коэААициентов:

v(k — 1. + 1, k) = (w(k — 1 + l,k), w(k — 1 +1,0,k,О),тт(1,0, k, 1),..., w(k — 1 + 1, 1,k,k),..., w(k — 1 +

I

+ 1, k, k, k ), w(k - 1 + 1, О, I

О 1; О О),, ъ)Ос 1+ 1 k

k, k, k, k ) которые в течение следующего такта

Аиксируются в регистре 9 коэфАициента.

Содержимое счетчика 4 дешифрируется с помощью дешифратора б, на выходе которого в течение такта с номером Т таким, что Т = 1 mode, вырабатывается уровень логической "1", под воздействием которого на выходе элемента ИЗБ-НЕ 7 Аормируется уровень логического "О", передаваемый на управляющий вход мультиплексора

15 . В течение остальных тактов на выходе элемента ИЛИ-HF, 7 формируется уровень логического "О", передаваемый на управляющий вход мультиплексора 15.

Таким образом, в течение такта с номером Т таким, что Т = f mudK, в вычислительном блоке 2 выполняет3 ся базовая операция А.

1647592 (13) +1, k — (1+1) где

15

- Тг

20 п — 1+ 1),w (1, у), (12) (d-1) х гие х(1,1) = Pa(1, ), х (1,0,),0), х(1,0,j,1),...,x(l, 1, j,k ),..., 25

35 (14) 40

В блоке 2„выполняется базовая операция В, в результате которой в первый 130 и второй 14g регистры

45 результата в такте К = k + j2 (И— — k) — 1j k 0 + k b eaaace>aaecca cywма

Рассмотрим работу устройства по тактам.

Такт R (d 1) k + (? (N k)

- 1)k q+bk+d.

На выходы умножителей 101...10д с блока 3 подаются отсчеты, соответству0 ющие вектору х(а + q, Ь + d). В блоке выполняется базовая операция А (или В), в результате которой вычисляется:

d+ 1)

) 55

В течение остальных тактов в вычислительном блоке 2 выполняется базовая операция В, которая отличается от базовой операции А линь тем, что мультиплексор 15 (поскольку на его управляющий вход поступает логическая "1") передает на вход первого 11 и второго 12 сумматоров промежуточный результат, хранящийся в первом 13 и втором 14 регистрах результата.

Рассмотрим формирование произвольного отсчета у(н,n) выходного массива согласно выражению! ( у(и,и) =,0 х (п - 1

8=< х(1, k, j, k), х(100j О, Ц,

О),..., х(1, k, k, j, k

k ))1

w(l, ) = (w(l,j), (1,0,j,î), 1

w(1,0,j,1),...,w(1,1,j,k ),...., w(l, k, 1, k ), w(l,0,0,j,0, О),...,w(1, k, k, 1,k, k )), к, н, ю н где Tr — операция транспортирования вектора.

Обозначим н = k + q, n = k + Ь, 1 = k — а + 1, j = k — d + 1.

y(k+ q, k+d)(d — 1) k+ а

=y(k+ q, k+ b)(d - 1) k+ а

-Ф вЂ” Ф

+ х(а + q, b + d) w(k — а +

d — - номер вычислительного блока (d = 1,k); а — номер отсчета первой переменной текущего суммирования входного двумерного сигнала (а = 1,k) °

b — - номер переменной, определяющей цикл суммирования для первого индекса k + Ъ (Ь =

О, 1-k); номер переменной, определяющей цикл суммирования для второго индекса двумерного сигнала (q = 0 N-k); k+a — номер очередного суммирования для одного выходного отсчета, причем при и = 1 выполняется базовая операция А, а в остальных случаях выполняется базовая операция В.

Например, при (1 = 1, q = О, Ь=О, а=1.

Такт R = d.k + 1 для вычислительного блока с индексом d вычисляется следующим образом:

y(k,k) d k+1 = y(k,k) d k + ф -y )Г

+ х(1,1+d) w (k,k-d) К

y(k+ q, k+ Ъ) = К M x(a+ а=t

- Тг

+q, b+d) w (k à+1, k— при замене переменных k + q = m

k+h=n, 1=k-а+1, j =k

+ 1, соответствующая выражению!

1647592

pl9п kó N-k!

k

1 -Ф у(ш,п) = -.- х(т-1+1, ug е Тг

+ 1). v(1.,1) (16) которая с выхода первого 13 и второго t4» регистров результата посту- 10 пает на выход устройства.

По Аормулам (2), (11) производятся соответственно одномерная и двумерная свертки третьего рода комплексного фильтруемого сигнала и комплекс- 15 ных коэААициентов с узлов Я ...В постоянной памяти, что соответствует нелинейной фильтрации комплексных сигналов. формула изобретения

Устройство для циАровой Аильтрации, содержащее К вычислительных блоков.(К вЂ” длина импульсной характеристики) и блок синхронизации, ад.ресный и управляющий. выходы котороFo подключены соответственно к адресным и управляющим входам всех вычислительных блоков, тактовые входы которых соединены с тактовым входом бло-З0 ка синхронизации и являются тактовым входом устройства, входом задания которого является вход режима блока синхронизации, причем К-й (К = 1,К) вичислительный блок содержит регистр коэААициентов, первый сумматор, пер35 вый регистр и узел постоянной памяти коэффициентов, выход которого подключен к инАормационному входу регистра коэффициентов, тактовый вход которого соединен с тактовым входом первого регистра и является тактовым входом вычислительного блока, адресным входом которого является адресный вход узла постоянной памяти коэффици- „ ентов, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения за счет выполнения нелинейной

Аильтрации комплексных последовательностей, в него введен блок комплексного умножения, первый и второй вы50 ходы которого подключены к входам соответственно первого и второго коэААициентов К-го вычислительного блока, первый и второй информационные входы которого соединены соответ. тзен но с первым и вторым входами бл-..ка комплексного умножения и являются входами соответственно ре ihHof: и мнимой частей входных отсчетов устройства, выходами реальной и мнимой частей результата которого являются соо;ветственно первьй и второй выходы К-го вычислительного блока, первый и второй выходи i-го (i = 1, li-1) вычислительного блока подключены соответственно к третьему и четвертому инАормационним входам (i+1)-ro вычислительного блока, причем в К-й вычислительный блок введены группы умножителей комплексных чисел, второй сумматор, второй регистр и мультиплексор, первый H второй выходы которого подключены к первым входам сооТветственно первого и BToporo сумматоров, выходы которых подключены к инАормационным входам соответственно первого и второго регистров, выходы которых являются соответственно первым и вторым выходами вычислительного бпока и подключены соответственно к первому ч второму информационным входам мультиплексора, управляю Н вход которого является управляющим- входом вичислительного блока, (2j-1)-й и ?j-й (j =- 1,N, М вЂ” число умножителей в группе) выходы регистра коэффициентов подключены соответственно к первому и второму входам

j-го умножителя комплексных чисел группы первый и Второй Выходы ко торого подключены к (j+1)-м входам соответственно первого и второго сумматоров, третий и четвертый входы умножителя комплексных чисел группы являются соответственно первым и вторым информационными входами вычислительного блока, входами первого и второго коэффициентов которого являются соответственно соединенные между собой третьи и четвертые входы всех умножителей комплексных чисел группы, кроме первого, третий.и четвертый информационные входы мультиплексора являются соответственно третьим и четвертым инАормационными входами вычислительного блока, к тактовому входу которого подключен тактовый вход второго регистра.

1647592

1647592

Составитель A.Áàðàíoâ

Редактор Н.Гунько Техред Л.Олийнык Корректор Н.Ревская

Заказ 1402 . - Тираж 413 Подписное

ВНИИПИ Государственного коиитета по изобретениям и открытиям при ГКНТ СССР

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101