Устройство для программирования схем постоянной памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных комплексов. Целью изобретения является расширение области применения устройства за счет увеличения класса программируемых микросхем постоянной памяти. Поставленная цель достигается тем, что устройство для программирования схем постоянной памяти содержит первый, второй, третий и четвертый формирователи импульсов, многофазный одновибратор, коммутатор адреса, коммутатор данных и выходной коммутатор, при этом в устройство можно записать информацию о данных нескольких классов постоянных запоминающих устройств, каждый из которых включает десятки типов. 6 ил. сл С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (st)s G 11 С 29/00

ГОСУДАРCTBEННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛ6СТВУ (21) 4615811/24 (22) 05,12.88 (46) 07.05.91. Бюл. N. 17 (71) Белгородский технологический институт строительных материалов им. И.А.Гришманова (72) А.В,Белоусов, В.Г.Рубанов,А.Д.Лагутин и А .Н.Потапенко (53) 681.327.66(088.8) (56) Авторское свидетельство СССР

N. 1285535, кл. G 11 С 17/00, 1983.

Авторское свидетельство СССР

N 796909,,кл. G 11 С 29/00, 1980.

Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных комплексов для автоматизации разработки цифровых устройств с перенастраиваемой структурой.

Цель изобретения — расширение области применения за счет увеличения класса программируемых микросхем постояйной памяти.

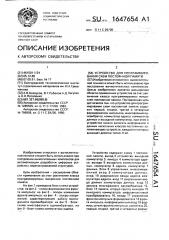

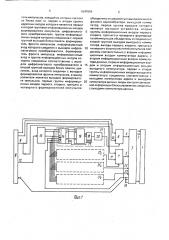

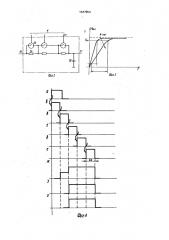

На фиг.1 приведена блок-схема устройства; на фиг,2 — схема формирователя фронта импульса; на фиг.3 - эпюры изменения фронта импульса: на фиг, 4 - эпюры напряжений,:характеризующих работу многофазнбго одновибратора; на фиг.5 - блоксхема многофазного одновибратора; на фиг.б - блок — схема коммутатора адреса, „„Ж„„ 1647654 Al (54) УСТРОЙСТВО ДЛЯ ПРОГРАММИРОВАНИЯ СХЕМ ПОСТОЯННОЙ ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных комплексов.

Целью изобретения является расширение области применения устройства за счет увеличения класса программируемых микросхем постоянной памяти. Поставленная цель достигается тем, что устройство для и рограммирования схем постоянной памяти содержит первый, второй. третий и четвертый формирователи импульсов, многофазный одновибратор, коммутатор адреса, коммутатор данных и выходной коммутатор, при этом в устройство можно записать информацию о данных нескольких классов постоянных запоминающих устройств, каждый из которых включает десятки типов. б ил.

Устройство содержит схему 1 постоянной памяти, выход 2 устройства, выходной 0 коммутатор 3, выходы 4 коммутатора адре- ф са, выходы 5 выходного коммутатора дан- ных, коммутатор 6 адреса. коммутатор 7 g данных, блок 8 управления, информационный вход 9 коммутатора данных, вход 10 разрешения ввода адреса коммутатора адреса, вход 11 разрешения ввода данных коммутатора данных, вход 12 запуска многофазного одновибратора 13, а блок 14 памяти, вторую группу выходов 15 выходного коммутатора, цифроаналоговый преобразователь 16, входы 17 управления фронтом импульса формирователя 18 фронта импульса, информационный вход 19 формирователя фронта импульса, усилитель 20, первый, второй, третий и четвертый форми-

1647654 рователи 21 импульсов, первый 22 и второй

23 информационные входы выходного коммутатора, резистор 24, ключ 25, конденсатор 26 и выход 27 формирователя фронта импульса, одновибратор 28, конденсатор

29, резистор 30 и шифратор 31 многофазного одновибратора 13, Устройство работает следующим образом.

К коммутатору 3 через выход 2 подключается программируемая схема постоянной памяти, Из блока 8 код адреса, необходимый для программирования, записывается в коммутатор 6, а в коммутатор 7 записывается слово данных, которое необходимо запрограммировать по данному адресу.

После записи в коммутатор 7 устройство обладает всей необходимой информацией для осуществления цикла программирования, который инициируется подачей сигнала с выхода 12 блока 8. Многофазный одновибратор 13 отрабатывает на своих выходах многофазный сигнал (фиг,4 а-е) в от-. вет на запускающий импульс с выхода 12 блока 8. Длительности импульсов на каждом выходе многофазного одновибратора равны и определяются минимально необходимым временем дискретизации временной диаграммы программирования.

Амплитуда сигналов программирования определяется m-разрядным словом, записанным во втором формирователе 21, и определяется коммутатором 3 и кодом с выхода многофазного одновибратора, 3а одно обращение к схеме 1 задается не только амплитуда импульсов программирования, но и изменяется их постоянная времени с помощью формирователя 18.

8 одном формирователе 21 можно записать информацию о нескольких классах

ПЗУ, каждый иэ которых включает порядка десятков типов, поэтому устройство приобретает весьма высокую гибкость за счет достаточно простых аппаратных решений, при этом программное обеспечение получается простое, так как для отработки цикла программирования необходимо только подать сигнал запуска, далее устройство все отрабатывает автономно. Такое программное обеспечение берет на себя функции формирования адресов, контроля записанной информации и не требует изменения при появлении новых типов ПЗУ.

Количество формирователей 21 равно четырем, так как в общем случае схемы памяти различаются числом адресных входов, входов данных, напряжений питания и выбора кристалла или входа для импульса программирования.

Таким образом, структура устройства получается с весьма высоким уровнем регулярности, что особенно важно в условиях массового производства, Блок 8 может быть выполнен в виде стандартного параллельного интерфейса для ввода и вывода цифровой информации, Формирователь 18 работает таким образом, что с входа 17 в соответствии с информацией на входах 17 подаются сигналы на ключи 25, которые коммутируют резисторы 24, изменяя постоянную времени RC-цепи, что позволяет регулировать фронт программирующих импульсов (фиг.3).

Многофазный одновибратор работает следующим образом.

На вход 12 первого одновибратора 28 подается сигнал запуска с блока 8, на выходе получают сигнал, длительность которого определяется времязадающей цепочкой

29,30 (фиг.5). Сигнал, снимаемый с интерфейсного выхода, запускает следующий одновибратор. Аналогично работают остальные одновибраторы. Таким образом происходит формирование многофазной последовательности (фиг.4 а — е).

В результате предложенных изменений значительно расширилась область применения предлагаемого устройства эа счет обеспечения оперативной регулировки длительности фронта импульсов программирования, улучшилась при этом ремонтопригодность и технологичность за счет более регулярной структуры устройства и, кроме того, упрощена аппаратная реализация устройства за счет введения кодирования временной диаграммы программирования и гибкого разделения функций аппаратной и программной частей.

Формула изобретения

Устройство для протраммирования схем постоянной памяти, содержащее блок управления, коммутатор адреса, вход разрешения ввода адреса которого соединен с первым выходом блока управления работой устройства, коммутатор данных, вход разрешения ввода данных которого соединен с вторым выходом блока управления работой устройства, первые информационные входы коммутатора адреса и коммутатора данных объединены и соединены с группой выходов блока управления работой устройства, о тл и ч а ю щ е е с я тем, что, с целью расширения области применения устройства эа счет увеличения класса программируемых микросхем постоянной памяти, оно содержит многофазный одновибратор, вход запус«а которого соединен с четвертым выходом блока управления работой устройства, первый, второй, третий и четвертый формирова1647654 тели импульсов, каждый из которых состоит из блока пам ти, первая и вторая группа адресных входов которого-являются первой и второй группами информационных входов формирователя импульсов, цифроаналогового преобразователя, группа информационных входов которого соединена с первой группой выходов блока памяти, формирователь фронта импульсов, информационный вход которого соединен с выходом цифроаналогового преобразователя, Формирователь фронта импульса, информационный вход и группа информационных входов которого соединены соответственно с выходом цифроанагового преобразователя и второй группой выходов блока памяти, усилитель, вход которого соединен с выходом формирователя фронта импульсов, а выход усилителя является выходом формирователя импульсов, первые группы информационных входов первого, второго, третьего и четвертого формирователей импульсов объединены и соединены с выходами многофазного одновибратора, выходной коммутатор, первая группа выходов которого является выходом устройства, вторые

5 группы информационных входов первого, второго, третьего и четвертого формирователей импульсов объединены и соединены с второй группой выходов выходного коммутатора, выходы первого, второго, третьего и

10 четвертого формирователей импульсов соединены соответственно с вторым информационным входом коммутатора адреса, с вторым информационным входом коммутатора данных, первым информационным вхо15 дом и вторым информационным входом выходного коммутатора, первая и вторая группы информационных входов выходного коммутатора соединены соответственно с выходами коммутатора адреса и выходами

20 коммутатора данных, входы контроля записанной информации блока управления соединены с выходами коммутатора данных.

1647654

1647654

6Ьге

Составитель Б. Венков

Техред М,Моргентал Корректор В. Гирняк

Редактор А. Мотыль

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101

Заказ 1405 Тираж 354 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5