Способ преобразования угла поворота вала в код и устройство для его осуществления

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной технике и может быть использовано для связи аналоговых исто чников информации с цифровым вычислительным устройством. С целью повышения точности путем повышения разрешающей способности и помехоустойчивости по способу преобразования угла поворота вала в код, основанному на формировании линейно изменяющегося во времени опорного кода, формировании из опорного кода синусоидального электрического сигнала, модулировании синусоидального электрического сигнала по фазе в функции угла поворота вала, формировании кода утла путем определения значения опорного кода при определенном значении напряжения модулированного синусоидального сигнала, измеряют напряжение модулированного синусоидального сигнала через равные временные интервалы т. раз за период, формируют для каждых измеренных значений разность значений текущего 1-го измерения и предыдущего (l-k)-ro измерения, формируют напряжение ступенчатого фазового сигнала путем последовательного суммирования разностей, в момент смены полярности напряжения ступенчатого фазового сигнала формируют его текущее напряжение в виде кода и определяют значение опорного кода, которое явпяется старшими разрядами выходного кода, а младшие разряды выходного кода формируют в виде обратной величины кода текущего напряжения ступенчатого фазового сигнала в момент смены его полярности. В устройство для осуществления способа, содержащее генератор 1 импульсов, делитель 2 частоты, блокЗ питания. (Ьазовоащатель4, первый регистр 6, введены аналого-цифровой преобразователь 5, второй 7 и третий 8 регистры, блок 9 оперативной памяти, вычитатель 10, накапливающий сумматор 1i, формирователь 12 импульсов, шина 13 сброса. 2 с.п. ф-лы, 5 ил. сл ю

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РеспуБЛик (я)s Н 03 M 1/64

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4628386/24 (22) 30.12.88 (46) 07 05.91. Бюл, Мт 17 (71) Научно-исследовательский физико-технический институт при Горьковском государственном университете им. Н,И.Лобачевского (72) H.Н.Макаров и В.И.Гоносков (53) 681,325 (088.8) (56) Авторское свидетельство СССР

М 1365354, кл. Н 03 M 1/64, 1986.

Авторское свидетельство СССР

N 994422110011, кл. Н 03 M 1/64, 1980. (54) СПОСОБ ПРЕОБРАЗОВАНИЯ УГЛА ПОВОРОТА ВАЛА В КОД И УСТРОЙСТВО ДЛЯ

ЕГО ОСУЩЕСТВЛЕНИЯ (57) Изобретение относится к области автоматики и.вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. С целью повышения т.очности путем повышения разрешающей способности и помехоустойчивости по способу преобразования угла поворота вала в код, основанному на формировании линейно изменяющегося во времени опорного кода, формировании из опорного кода синусоидального электрического сигнала, модулировании синусоидального электрического сигнала по фазе в

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством, Целью изобретения является повышение точности преобразования угла поворота

„„5 „„1647901 Al функции угла поворота вала, формировании кода угла путем определения значения опорного кода при определенном значении напряжения модулированного синусоидального сигнала, измеряют напряжение модулированного синусоидального сигнала через равные временные интервалы ITI раэ за период, формиру.от для каждых измеренных значений разность значений текущего

i-ro измерения и предыдущего (I-k}-ro измерения, формируют напряжение ступенчатого фазового сигнала путем последовательного суммирования разностей, в момент смены полярности напряжения ступенчатого фазового сигнала формируют его текущее напряжение в виде кода и опредеllBIoT значение опорного кода, которое является старшими разрядами выходного кода, а младшие разряды выходного кода формируют в виде обратной величины кода текущего напряжения ступенчатого фазового сигнала в момент смены его полярности. В устройство для осуществления способа. содержащее генератор 1 импульсов, делитель

2 частоты, блок 3 питания. Ьаэовоащатель 4, первый регистр 6, введены аналого-цифровой преобразователь 5, второй 7 и третий 8 регистры, блок 9 оперативной памяти, вычитатель 10, накапливающий сумматор формирователь 12 импульсов, шина 13 сброса. 2 с.п. ф-лы, 5 ил. ! вала в код путем повышения разрешающей способности и помехоустойчивости.

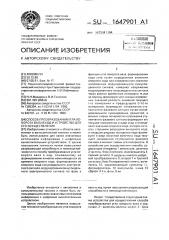

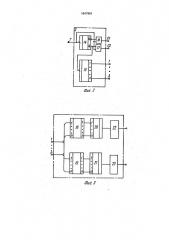

На фиг, 1 представлена структурная схема устройства для осуществления способа преобразования. угла поворота вала в код; на фиг. 2 —; на фиг. 3 — блок

1647901 питания; на фиг. 4 — накапливающий сумматор; на фиг, 5- формирователь импульсов, Устройство содержит генератор 1 импульсов, делитель 2 частоты, блок 3 питания, фаэовращатель 4, аналого-цифровой преобразователь (АЦП) 5, пврвый 6, второй

7 и третий 8 регистры, блок 9 оперативной памяти, вычитатель 10, накапливающий сумматор 11, формирователь 12 импульсов, шину 13 сброса.

Делитель 2 частоты (фиг. 2) содержит триггер 14, счетчик 15, элементы И 16 и 17.

Блок 3 питания (фиг. 3) содержит блоки 18 и

19 постоянной памяти, цифроаналоговые преобразователи 20 и 21, усилители 22 и 23.

Накапливающий сумматор 11 (фиг. 4) содержит комбинационный сумматор 24 и регистр 25, Формирователь 12 импульсов (фиг. 5) содержит триггеры 26 и 27 и элемент

И 28.

Устройство работает следующим образом.

Генератор 1 формирует прямоугольные импульсы с частотой f, которые поступают на вход делителя 2 частоты. Делитель 2 вырабатывает две последовательности. неперекрывающихся тактовых импульсов С1 и

С2. На выходах Q<... Q> делителя 2 формируется линейно возрастающий и-разрядный двоичный код, изменяющийся с периодом

T. Кодс выхода делителя 2 поступает в блок . 3 питания, который вырабатывает опорные сигналы переменного тока U> = Ummsin cut и Uz =. Umcos со т, используемые для питания статорных обмоток фазовращателя 4, С выхода роторной обмотки фазовращателя 4 снимается сигнал переменного тока Оз = Usln(cot+ pа), сдвинутый относительно опорного сигнала на угол р Q (где р — коэффициент электрической редукции фазовращателя). Аналого-цифровой преобразователь 5 преобразует аналоговый сигнал с выхода фазовращателя 4 в цифровой r-разрядный код, который через равные промежутки времени тпереписывается стробирующим импульсом С1 в регистр 7, На выходах регистра 7 формируется последовательность кодов A1... Am, где т = 2", т,е. за период Т осуществляется 2" преобразований напряжения выходного сигнала фазовращателя 4, В блоке 9 оперативной памяти (микросхема 155 РУ 5) производится запись импульсом С 2 кода текущего i-го измерения с выходов регистра 7 по адресу, соответствующему коду i разрядов делителя

2 частоты, поступающему на адресные входы блока 9. При отсутствии импульса С2 блок 9 находится в режиме воспроизведе ния и на информационные входы регистра 8

55 чания сигнала "Сброс" устройство выходит на режим работы. В этом интервале выходной код сумматора 11 может принимать любые значения, которые определяются моментом окончания сигнала "Сброс", кодом делителя 2 и величиной угла а поворота фазовращателя 4, В дальнейшем фаза изменения кода в сумматоре 11 определяется только величиной угла и независимо от мо- мента окончания сигнала "-Сброс", Формирование в выходном коде дополнительных г младших разрядов повышает разрешающую способность, а формирование момента съема информации с делителя

2 по смене полярности ступенчатого фазового сигнала, образованного путем последовательного суммирования разноствй текущего и предыдущего измерений, повышает помехоустойчивость преобразователя, поступает выходная информация блока 9, записанная в него на К = 2 тактов ранее по тому же адресу. Импульсом С1 выходная информация блока 9 фиксируется в регистре

5 8 перед тем, как записать в блок.9 импульсом С2 код текущего 1-ro измерения. В вычитателе 10 формируется разность кода текущего 1-гоизмерения с выхода регистра 7 и предыдущего (i-K)-го измерения с выхода

10 регистра 8, В сумматоре 11 производится суммирование выходных кодов вычитателя

10, в результате чего формируется ступенчатый фазовый сигнал, изменяющийся по синусоидальному закону. Фазовый сдвиг

15 этого сигнала пропорционален углу поворота вала фазовращателя 4 и смещен по фазе на постоянную величину по отношению к коду на выходах регистра 7;

Старший разряд выходного кода накап20 ливающего сумматора 11 поступает на информационный вход формирователя 12 (фиг. 5), который в момент изменения старшего разряда (знакового) с 1 на 0 формирует одиночный импульс положительной поляр25 ности, равный по длительности периоду генератора 1. Передним фронтом этого импульса в старшие и разрядов регистра 6 заносится выходной код делителя 2, а 8 младшие r разрядов регистра 6 заносится

30 обратный код из младших r разрядов накапливающего сумматора 11, который является точным отсчетом..

Перед началом работы .сигналом .

"Сброс" устройство устанавливается в ис35 ходное состояние. Длительность сигнала

"Сброс" должна быть не менее К= 2 тактов.

При этом регистры 6 и 7, накапливающий сумматор 11 и блок 9 оперативной памяти обнуляются. В первые К тактов после окон1647901

Формула изобретения

1. Способ преобразования угла поворота вала в код, основанный на формировании линейно изменяющегося во времени опорного кода, формировании из опорного кода синусоидального электрического сигнала, модулировании синусоидального электрического сигнала по фазе в функции угла поворота вала, формировании кода угла путем определения значения опорного кода при определенном значении напряжения модулированного синусоидального сигнала, о тл и ч а ю шийся тем, что, с целью повышения точности преобразования, измеряют напряжение модулированного синусоидального сигнала через равные временные интервалы m раэ за период. формируют для каждых измеренных значений разность значений текущего i-го измерения и предыдущего (I — K)-го измерения, формируют напряжение ступенчатого фазового сигнала путем последовательного суммирования разностей, в момент смены полярности напряжения ступенчатого фазового сигнала формируют его текущее напряжение в виде кода и определяют значение опорного кода, которое является старшими разрядами выходного кода, а младшие разряды выходного кода формируют в виде обратной величины кода текущего напряжения ступенчатого фазового сигнала в момент смены его полярности.

2. Устройство для преобразования угла поворота вала в код, содержащее генератор импульсов, выход которого соединен с входом делителя частоты, выходы старших разрядов делителя частоты соединены с входами блока питания, выходы которого соединены с входами фазовращателя, первый регистр, информационные входы старших разрядов которого подключены к выходам старших разрядов делителя частоты, а выходы являются выходами устройства, от л и ч а ю щ ее с я тем. что, с целью повышения точности преобразователя, в него введены аналого-цифровой преобра5 зователь, второй и третий регистры, блок оперативной памяти, вычитатель, накапливающий сумматор, формирователь импульсов и шина сброса, выход фазовращателя соединен с входом аналого-цифрового пре10 обраэователя, выходы которого соединены с информационными входами второго регистра, выходы второго регистра соединены с прямыми входами вычитателя и и нформационными входами блока опера15 тивной памяти, адресные входы которого подключены к выходам старших разрядов делителя частоты, а выходы соединены с информационными входами третьего регистра, выходы третьего регистра соединены

20 с инверсными входами вычитателя, выходы которого соединены с информационными входами накапливающего сумматора, инверсные выходы младших разрядов накапливающего сумматора соединены с

25 информационными входами младших разрядов первого регистра, а выход старшего разряда накапливающего сумматора соединен с информационным входом формирователя импульсов, один выход младшего

30 разряда делителя частоты соединен с тактовыми входами второго и третьего регистров и первым тактовым входом формирователя импульсов, другой выход младшего разряда делителя частоты соединен с тактовым вхо35 дом накапливающего сумматора, вторым тактовым входом формирователя импульсов и управляющим входом блока оперативной памяти, выход формирователя импульсов соединен с тактовым входом первого реги40 стра, а шина сброса соединена с установочными входами первого и второго регистров и накапливающего сумматора.

1647901

1647901

Составитель А,Смирнов

Редактор H.Ëàýàðåíêo Техред M.Ìoðãåíòàë Корректор В.Гирняк

Заказ 1414 Тираж Л3 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

-113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101