Устройство для обнаружения ошибок

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике, а именно к устройствам контроля информации , и может быть использовано в цифровых системах передачи с применением пятиуровневого кода БК-45. Изобретение позволяет повысить быстродействие и упростить устройство. Устройство для обнаружения ошибок содержит блок 1 компараторов, два элемента НЕТ 2 и 3, триггер 4, два дешифратора 5 и 6 и элемент ИЛИ 7. Блок 1 компараторов содержит фазоинвертор, эмиттерные повторители и четыре компаратора . 1 з.п.ф-лы, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)л Н 03 M 13/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО.ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

9»

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4394272/24 (22) 17.03.88 (46) 07.05.91. Бюл. М 17 (72) Г.В. Чижов (53) 681.398.623 (088.8) (56) Заявка Японии М 57-22253, «л. Н 04 Е 1/10, 1982.

Авторское свидетельство СССР

ЬЬ 1432785, кл. Н 03 Ы 13/00, 1986., (54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ

ОШИБОК (57) Изобретение относится к автоматике, а

„„Я „„1647913 А1

2 именно к устройствам контроля информации, и может быть использовано в цифровых системах передачи с применением пятиуровневого кода БК-45. Изобретение позволяет повысить быстродействие и упростить устройство. Устройство для обнаружения ошибок содержит блок 1 компараторов, два элемента НЕТ 2 и 3, триггер 4, два дешифpampa 5 и 6 и элемент ИЛИ 7. Блок 1 компараторов содержит фаэоинвертор, эмиттерные повторители и четыре компаратора. 1 з.п.ф-лы, 2 ил.

1647913

30

50 5

Изобретение относится к автоматике, а именно к устройствам контроля информации, и может быть использовано в цифровых системах передачи с применением пятиуровневого кода БК-45.

Цель изобретения — повышение быстродействия и упрощение устройства.

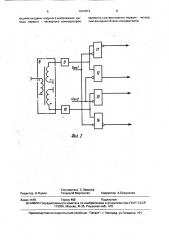

Н а фиг.1 и редста еле на структурная схема устройства для обнаружения ошибок; на фиг,2 — структурная схема блока компараторов.

В предлагаемом устройстве появляется возможность подавать импульс ошибки с выхода одного иэ дешифраторов сразу на установочные входы триггера, вызывая его переключение и тем самым из общего времени задержки с момента появления импульса ошибки на выходе дешифратора до переключения триггера исключается время распространения сигнала по цепочке из двух элементов ИЛИ, что и позволяет повы" сить быстродействие устройства при более простом его исполнении.

Устройство содержит блок 1 компараторов, первый и второй элементы HET 2 и 3, триггер 4, первый и второй дешифраторы 5 и 6 и элемент ИЛИ 7. Блок 1 компараторов содержи фазоинвертор 8, эмиттерные повторители 9 и 10 и первый, второй, третий и четвертый компараторы 11 — 14.

Устройство для обнаружения ошибок работает следующим образом, На вход блока 1 компараторов поступает пятиуровневый линейный сигнал в виде ко. да БК-45.

На соответствующих выходах блока 1 компараторов формируются двоичные импульсы. Импульсы со второго и третьего выходов блока 1 компараторов, соответствующие посылкам "+2" и "-2" во входном сигнале, запрещают прохождение импульсов, соответствующих двоичным по сылкам "+2" и "-2" с первого и второго выходов блока 1 компараторов на выходы первого и второго элементов НЕТ 2 и 3 соответственно. Импульсы с объединенных инверсных выходов элементов HET 2 и 3 поступают на тактовый вход триггера 4 и вызывают его переключение. Сигналы с выходов триггера 4 поступают на вторые входы дешифраторов 5 и 6. При отсутствии ошибок во входном сигнале соответствующего выхода триггера 4 на второй вход соответствующего дешифратора 5 или 6 поступает сигнал, запрещающий прохождение третьего импульса положительной или отрицательной триады на выход соответствующего дешифратора 5 или 6 и на выход устройства. При наличии ошибки во входном сигнале нарушается четность текущей цифровой суммы и с соответствующего триггера 4 и на второй вход соответствующего дешифратора 5 или 6 поступает сиг5 нал, разрешающий прохождение третьего импульса триады на выход соответствующего дешифратора 5 или6. Этот импульс (импульс ошибки) поступает на соответствующий установочный вход триггера 4 и вызывает его дополнительное переключение. В результате с того же выхода триггера 4 на второй вход того же дешифратора 5 или 6 снова поступает сигнал запрета, а на выходе дешифратора 5 или 6 формируется импульс ошибки, который через элемент ИЛИ 7 поступает на выход устройства.

Комбинация символов "-1-1-1" ("+1+1+1 " ): в пятиуровневом сигнале с кодом БК-45 всегда следует за символом счетным (нечетным) номером значения текущей цифровой суммы, Формула изобретения

1. Устройство для обнаружения ошибок, содержащее триггер, элемент ИЛИ, выход которого является выходом устройства, блок компараторов, первый и второй выходы которого соединены соответственно с первым и вторым входами первого элемента

НЕТ, третий и четвертый выходы — соответственно с первым и вторым входами второго элемент НЕТ, прямые выходы первого и второго элементов HET соединены соответственно с первыми входами первого и второго дешифраторов, вход блока компараторов является входом устройства, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия и упрощения устройства, инверсные выходы первого и второго элементов HET объединены и соединены с Свходом триггера. прямой и инверсный выходы которого соединены соответственно с вторыми входами первого и второго дешифраторов, выход первого дешифратора соединен с первым. входом элемента

ИЛИ и S-входом триггера, выход второго дешифратора соединен с вторым входом элемента ИЛИ и R-входом триггера.

2. Устройство по п.1, о т л и ч а ю щ е ес я тем, что блок компараторов содержит фазоинвертор, вход которого является с входом блока компараторов, выходы соединены через эмиттерные повторители с первыми входами соответственно первого, второго, третьего и четвертого компараторов, вторые входы первого, четвертого и второго, третьего компараторов объединены соответственно и являются соответству1647913

Составитель С.Левичев

Техред M.Ìîðãåíòàë Корректор А.Осауленко

Редактор М.Яцола

Заказ 1415 Тираж 4)6 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва. Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 ющими входами опорного напряжения, выходы первого — четвертого компараторов являются соответственно первым — четвертым.выходами блока компараторов.