Устройство преобразования частоты в код

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике и может быть использовано для создания быстродействующих частотомеров, детекторов частотно-манипулированных сигналов , а также в системах сбора данных с цифровой обработкой аналоговых сигналов. Изобретение позволяет упростить устройство за счет того, что в преобразователь, содержащий формирователь входных сигналов, опорный генератор, формирователь кода и регистр, введены счетчик, счетчик адреса, ПЗУ, делитель частоты, блок сравнения кодов, два коммутатора. Изобретение позволяет расширит ь также динамический диапазон за счет дополнительного введения в устройство двух делителей частоты с переменным коэффициентом деления и приоритетного шифратора. 1 з.п.ф-лы, 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 03 M 1/60

ГОСУДАРСТВРННЫИ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ. (21) 4400776/24 (22) 30,03.88 (46) 07.05.91. Бюл. М 17 (71) Специальное конструкторское бюро прикладной геофизики СО АН СССР (72) Ю.В. Тефанов и В.В. Масленников (53) 681.325 (088.8) (56) Авторское свидетельство СССР

N- 1093988, кл, G 01 R 23/20,1986.

Кирианаки Н.В. и др. Цифровые измерения частотно-временных параметров сигналов. — Львов; Высшая школа, 1978, с.

77-78. (54) УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ЧАСТОТЫ.В КОД (57) Изобретение относится к измерительИзобретение относится к измерительной технике и может быть использовано для создания быстродействующих частотомеров, детекторов частотно-манипулированных сигналов, а также в системах сбора данных с цифровой обработкой аналоговых сигналов.

Цель изобретения — уп рощение устройства и расширение динамического диапазона.

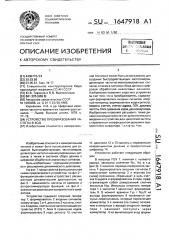

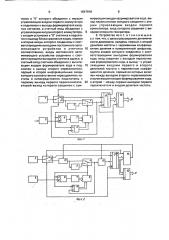

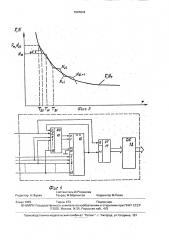

На фиг,1 представлена функциональная схема предлагаемого устройства; на фиг.2— функциональная схема устройства с расширенным динамическим диапазоном; на фиг.3 — зависимость частоты от времени и аппроксимирующая функция; на фиг.4— возможная реализация приоритетного шифратора.

Устройство содержит опорный генератор 1, формирователь 2 входных сигналов, коммутаторы 3 и 4; делитель 5 частоты, счетчик 6 адреса, постоянное запоминающее устройство (ПЗУ) 7, блок 8 сравнения кодов, формирователь 9 кода, регистр 10; счетчик

„„5LI„„1647918 А1 ной технике и может быть использовано для создания быстродействующих частотомеров, детекторов частотно-манипулированных сигналов, а также в системах сбора данных с цифровой обработкой аналоговых сигналов.

Изобретение позволяет упростить устройство за счет того, что в преобразователь. содержащий формирователь входных сигналов, опорный генератор, формирователь кода и регистр. введены счетчик, счетчик адреса, ПЗУ, делитель частоты, блок сравнения кодов, два коммутатора.

Изобретение позволяет расширить также динамический диапазон за счет дополнительного введения в устройство двух делителей частоты с переменным коэффициентом деления и приоритетного шифратора. 1 з.п.ф-лы, 4 ил, 11, делители 12 и 13 частоты с переменным коэффициентом деления и приоритетный шифратор 14.

Устройство работает следующим образом.

В матрице ПЗУ 7, начиная с нулевого адреса, записаны Значения Мц, Nz; и т.д. (фиг.3). С началом периода измеряемой частоты F формирователь входных сигналов 2 переключает коммутатор 3 в верхнее (по схеме) положение, сбрасывает в нуль счетчик 6 адреса и формирователь 9 кода, пред. ставляющий собой реверсивный счетчик емкостью Nzo. Импульсы опорного генератора 1 с частотой f заполняют формирователь 9. В момент времени Tzo = Nzo/f на выходе формирователя 9 появляется импульс переполнения, который переключает коммутатор 3 в нижнее {по схеме) положение и импульсы с выхода опорного генератора 1 начинают поступать через коммутатор 4 на вычитающий вход форми1647918

10

Т20 Т - Т20 k при значении кода

N2Q» N» N2Q V k

1 .Д N20 N N20, 1 д Рм F = Гм, рователя 9. При уменьшении кода на выходе формирователя 9 до величины 1ч 11 на выходе блока 8 сравнения кодов появляется импульс, который увеличивает на единицу . значение счетчика 6 адреса и переключает коммутатор 4 в нижнее (no схеме) положение, При этом на вычитающий вход формирователя 9 начинают поступать импульсы частотой f/k с выхода делителя 5 частоты, В матрице ПЗУ 7 по адресу, полученному с выхода счетчика 6, записано значение кода

N21 и при достижении этой величины на выходе формирователя 9, блок сравнения 8 выработает второй импульс, переводит коммутатора 4 в верхнее (по схеме) положение. увеличивает на единицу код счетчика 6 адреса и т.д, Формирование кода заканчивается в момент окончания периода измеряемой частоты, значение кода с выхода формирователя 9 переписывается в регистр 10, и процесс формирования кода начинается сначала, Таким образом, на выходе регистр" 10 находится код, соответствующий частоте предыдущего измеренного периода с погрешностью не хуже % N, и время при данном способе преобразования равно периоду измеряемого сигнала.

Если в матрице ПЗУ 7, начиная с нулевогс адреса, записаны значения;

N0 = N2Q N1Q; 1 = "1О ч21

N2 = N21 — N11 (1) чз = ч11 ч22

Мi = N2(Й1!+1, то в счетчике 11 на каждом интервале аппроксимации формируется разность между йр и М11, которая и сравнивается со значениями, записанными в ПЗУ для каждого инторвала аппроксимации, Таким образом, разрядность ПЗУ и схемы сравнения должна соответствовать максимальной разнице кодов на аппроксимируемом отрезке. которая значи тельно меньше разрядности полного формиРуемого кода, чем достигается упрощение схемы, Недостатком устройства является то, что диапазон измеряемых частот и, соответственно, формируемого кода лежит в преде, лах

Расширение диапазона возможно увеличением коэффициента К, но при этом за счет ограничения увеличивается значение допустимой погрешности Л N. Для расширения динамического диапазона без увеличения погрешности в устройство введены первый и второй делители 12 и 13 частоты с переменным коэффициентом деления и приоритетный шифратор 14.

Устройство (фиг.2) работает следующим образом.

Делители 12 и 13 делят частоту входного сигнала на величину, равную (Ч k), где е— значение кода на выходе приоритетного шифратора.

В интервал времени на выходе приоритетного шифратора 14 значение е = 0 и оба делителя не оказывают влияния на работу схемы, так как их коэффициент деления равен единице. При достижеЙго нии значения кода N = на выходе

k приоритетного шифратора появляется код, равный 1, который устанавливает коэффициент деления делителей 12 и 13, равным

V k, Нетрудно показать, что подстановка новых значений f, N20 Тго и формирование разницы кодов из системы уравнений (1) счетчиком 11. сохраняет значения N, записанные в матрице ПЗУ, для любого значения е на выходе приоритетного шифратора. Поэтому массив данных в ПЗУ сохраняется для каждого поддиапазона и необходимо при изменении кода на выходе приоритетного шифратора 14 счетчик адреса 6. возвращать в исходное состояние, что достигается соответствующим выбором емкости счетчика адреса 6.

Формула изобретения

1.. Устройство преобразования частоты в код, содержащее опорный генератор, формирователь кода, регистр, формирователь входных сигналов. выход которого подклю-. чен к тактирующему входу регистра и установочному входу формирователя кода, выходы которого соединены с соответствующими информационными входами регистра, выходы которого являются выходной шиной, о т л и ч а ю щ е е с я тем, что, с целью упрощения, в устройство введены два коммутатора, счетчик, делитель частоты, постоянное запоминающее устройство, блок сравнения кодов, счетчик адреса, вход уста1647918 новак в "0" которого объединен с первым управляющим входом первого коммутатора и подключен к выходу формирователя входных сигналов, а счетный вход объединен с управляющим входом второго коммутатора. 5 с входом установки в "О" счетчика и подключен к выходу блока сравнения кодов, первые и вторые входы которого соединены с соответствующими выходами постоянного запоминающего устройства и счетчика 10 соответственно, входы постоянного запоминающего устройства соединены с соответствующими выходами счетчика адреса, а счетный вход счетчика объединен с вычитающим входом формирователя кода и под- 15 ключен к выходу второго переключателя, первый и второй информационные входы которого соответственно через делитель частоты и непосредственно подключены к первому выходу первого переключателя, 20 второй выход которого соединен с суммирующим входом формирователя кода, выход переполнения которого соединен с вторым управляющим входом первого коммутатора, вход которого соединен с выходом опорного генератора.

2. Устройство по п.1, о т л и ч а ю щ е ес я тем. что, с целью расширения динамического диапазона, введены первый и второй делители частоты с переменным коэффициентом деления и приоритетный шифратор, группа входов которого соединена с соответствующими выходами формирователя кода, вход соединен с выходом переполнения формирователя кода, а выход — с управляющими входами первого и второго делителей частоты с переменным коэффициентом деления, первый из которых включен между выходом второго переключателя и вычитающим входом формирователя кода, а второй — между первым выходом первого переключателя и входом делителя частоты, 1647918

Составитель И,Романова

Техред М.Моргентал Корректор M.Ïoæî

Редактор Н.Яцола

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Заказ 1415 Тираж 473 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва. Ж-35, Раушская наб,. 4/5