Устройство для умножения матриц

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах для умножения матриц. Целью изобретения является повышение быстродействия при одновременном сокращении аппаратурных затрат. Цель достигается тем, что в квадратной матрице рхр вычисли тельных модулей (р - размерность перемножаемых матриц) сдвиг и вычисление частичных сумм происходят асинхронно в течение каждого такта. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) 5 G 06 F 15 347,, б х!," Х х

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И АВТОРСКОМУ/ СВИДЕТЕЛЬСТВУ в Х, б.бх1

К «-б с;,;=с;;+а; вь, l,/,1=1,р, бб авых = авх

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

flO ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГННТ СССР (21) 4691138/24 (22) 16.05.89 (46) 15.05.91. Бюл. № 18 (71) Научно-исследовательский институт многопроцессорных вычислительных систем при Таганрогском радиотехническом институте им. В. Д. Калмыкова (72) В. Ю. Лозбенев, А. К., Шилов, С. П. Горбунов и Е. Г. Ушаков (53) 681.3 (088.8) (56) ТИИЭР. т. 72, 1984, J¹ 7, с. 140.

Авторское свидетельство СССР № 1363247, кл. G 06 F 15/347, 1986.

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах для умножения квадратных рхр матриц.

Цель изобретения — повышение быстродействия при одновременном сокращении аппаратурных затрат.

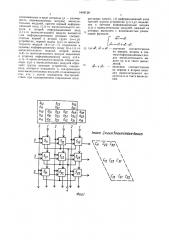

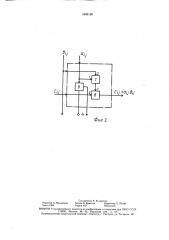

На фиг. 1 приведена структурная схема устройства для р=3; на фиг. 2 — пример выполнения вычислительного модуля.

Устройство (фиг. !) содержит первую 1, третью 2 и вторую 3 группы информационных входов, микровход 4, группу выходов, матрицу рхр вычислительных модулей 5.

Каждый вычислительный модуль содержит регистр 6, умножитель 7 и сумматор 8.

В основу работы устройства положен способ вычисления матрицы — результата с по реккуррентному соотношению: где а; и в ; — элементы перемножаемых матриц, Каждый вычислительный модуль выполняет следующую функцию:

„„SU„„1649126 А 1 (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

МАТРИЦ (57) Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах для умножения матриц. Целью изобретения является повышение быстродействия при одновременном сокращении аппаратурных затрат. Цель достигается тем, что в квадратной матрице рхр вычисли тельных модулей (р — размерность перемножаемых матриц) сдвиг и вычисление частичных сумм происходят асинхронно в течение каждого такта. 2 ил. б б б б

Свых = Свх +Qex ° Ввх, I б б в б где а-, свх и в « — значения на первом, втором и третьем соответственно информационны входах вычислительного модуля на -м такте вычислений; а . и сьых — значения на первом и втором соответственно Bb(xoдах вычислительного модуля на i-м такте вычислений.

Последовательность подачи элементов перемножаемых матриц и считывания матрицы-результата показана на фиг. 1. На информационные входы 3 второй группы подаются нулевые значения, на информационные входы первой и третьей групп — элементы матриц А и В.

Особенностью функционирования устройства является суммирование частных произведений а;; ° в;; без сдвига накапливаемых сумм с,"; на очередном такте.

Формула изобретения

Устройство для умножения матриц, содержащее р вычислительных модулей, ор1649126

@Ч

Йвых =Двх

2 1 Я з ганизованных в виде матрицы (р — размерность перемножаемых матриц) вычислительных модулей, причем первый информационный вход (1, )-го вычислительного модуля и второй информационный вход (i, I ) -ro вычислительного модуля являются -ми информационными входами соответственно первой и второй групп (i= i,ð) устройства, первый выход (к))-го вычислительного модуля (k=1,р — ) подключен к первому информационному входу (k+1,i) -го вычислительного модуля, второй выход (i,k) -го вычислительного модуля подключен к второму информационному входу (i,k+

+ 1)-го вычислительного модуля, вторые выходы (i,р)-х вычислительных модулей образуют группу выходов устройства, синхровход которого подключен к синхровходам всех вычислительных модулей, отличающееся тем, что, с целью повышения быстродействия при одновременном сокращении аппаратурных затрат, /-й информационный вход третьей группы устройства (1=1,р) подключен к третьим информационным входам (Ц)-х вычислительных модулей, каждый из которых выполнен с возможностью реализации функции

d. (Свых = &x +Двх ° х, k ы ы 0 где а", о. и в- — значения соответственно на первом, втором и третьем информационных входах вычислительного модуля на а-м такте вычислений;

15 d. а(а . и cI . — значения соответственно на первом и втором выходах вычислительного модуля на я-м такте вычисления.

Ыакт Хтакв Звакв4такабщакр

7с«с» с„

K cd czar cd i

1 å н л

1649126

Составитель К. Кухаренко

Редактор А.Маковская Техред А. Кравчук Корректор Л. Патай

Заказ 1506 Тираж 419 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

I 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-издательский комбинат «Патент», r Ужгород, ул. Гагарина, 101