Устройство для ввода информации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении систем сбора и обработки аналоговых данных. С целью сокращения избыточности выходных данных в устройство, содержащее компараторы 1, первый и второй счетчики 2 и 6, блок управления 8, цифроаналоговый преобразователь 9, мультиплексор 3, первый блок памяти 4, ключ 10, введены второй блок памяти 5, блок сравнения 7, формирователь признака кода 11, третий счетчик 12, первый и второй коммутаторы 13 и 14, элемент И 15. За счет формирования устройством признаков кодов поля Галуа, которые обеспечивают плотную упаковку неповторяющихся двоичных кодов, а также за счет формирования признаков информативности отсчетов достигается сжатие выходной информации. 2 з.п.ф-лы, 5 ил. (Л

СОЮЗ СООЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (!9} (!!} (5!} С 06 Р 3/05

ОПИСАНИЕ HSOEPETEHHR

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ акое 1.ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОЧНРЫТИЯМ

ПРИ П(НТ СССР (21) 4715916/24 (22) 03.05.89 (46) 15.05.91. Бюл. Р 18 (71) Институт кибернетики им. В.М. Глункова (72) Б.М. 0!евчук, Я.!!.Николайчук и Л.Б. Петришин (53) 681, 327 (088. 8) .(56) Авторское свидетельство СССР

}} 1151946 ° кл. Г 06 Р 3/05, 1983.

Авторское свидетельство СССР по заявке к- 4286869/24, кл. С 06 F 3/05, 1987. (54) устРойство лля вводА иньоРмАции (57) Изобретение относится к вычислительной технике и может быть использовано при построении .систем сбора

2 и обработки аналоговых данных. С целью сокращения. избыточности выходных данных в устройство, содержанее компараторы 1, первый и второй счетчики 2 и 6, блок управления 8, цифроаналоговый преобразователь 9, мультиплексор 3, первый блок памяти 4, ключ 10 введены второй блок памяти 5, блок сравнения 7, формирователь признака кода 11, третий счетчик 12, первый и второй коммутаторы 13 и 14, элемент И 15. За счет формирования устройством признаков кодов поля Галуа, которые обеспечивают плотную упаковку неповторяющнхся двоичных кодов, а также за счет формирования признаков информативносС ти отсчетов достигается сжатие выход- 9 ной информации. 2 з.п.ф-лы, 5 ил.

1649529

Изобретение относится к. вычислительной технике и может быть использовано как совместно с ЭВ?1 при построении высокопроизводительных систем сбора и обработки аналоговых данных, . так и отдельно при построении многоканальных информационно-измерительных систем.

Цель изобретения — сокращение избы-10 .точности выводимой информации.

В устройстве сокращение избыточности выходных данных обеспечивается уменьшением служебных данных о временной привязке существенных отсчетов и устранением кодов канальной привязки существенных отсчетов. При этом на выхоДе устройства формируется бит.ориентированный код в виде следующей последовательности: G-",Ò, $Х;), где

С - бит текущего признака кода Галуа, который принимает значение 0 или

1 в зависимости от кодового ключа генератора кодов поля Галуа; Т; — бит признака существенности отсчета, причем при Т = 1 отсчет является существенным, а при Т = 0 — несущественным;

j Х - k-битовый двоичный код существенного отсчета (k — количество битов последовательного кодф Если текущий отсчет входного сигнала является существенным, а последующий отсчет является несущественным, то устройство .формирует следующую последовательность: G 1P С + OG . . Восстанов 35 ление сжатых сйгналов осуществляется по меткам С, с учетом текуших значений признака Т, .

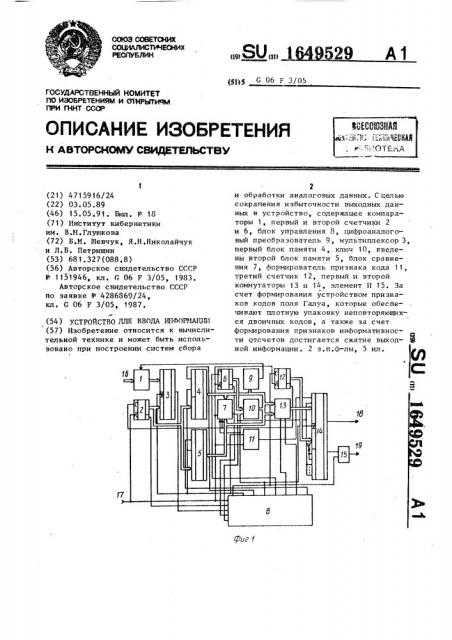

На фиг. 1 приведена структурная .схема устройства1на фиг. 2 — струк40

:турная схема блока управления; на фиг. 3 — структурная схема блока сравнения кодов; на фиг, 4 — струк" турная схема формирователя признака кода на йиг. 5 - временные диаграммы ф °

45 работы устройства.

Устройство содержит компараторы 1, первый счетчик 2, мультиплексор 3, . первый 4 и второй 5 блоки памяти, второй счетчик 6, блок 7 сравнения, блок 8 управления, цифроаналоговый 50 преобразователь (ПДП) 9, ключи 10, формирователь 11 признака кода, тре. тий счетчик 12, первый 13 и второй 14 коммутаторы и элемент И 15 и имеет входы и выходы 16-19 устройства. 55

Блок 8 управления состоит из пер- вого элемента ИЛИ 20, генератора 21 импульсов, триггера 22, первого элемента И 23, делителя частоты 24, второго элемента ИЛИ 25, элемента 26 задержки, формирователя 27 импульса, второго 28, третьего 29 и четвертого 30 элементов И, третьего 31 и четвертого 32 элементов ИЛИ, пятого 33 и mecтого 34 элементов И.

Блок 7 сравнения содержит элемент

35 сравнения, первый триггер 36, элемент ИЛИ 37, элемент И 38, элемент

39 задержки и второй триггер 40.

Формирователь 11 признака кода образуют элемент ИЛИ 4 1, одновибратор 42, регистр 43 и элементы 44 обратной связи.

Устройство для ввода информации работает следующим образом.

Входные аналоговые сигналы поступают на входы устройства 16. На входы компараторов 1 подается выходной сигнал ЦАП 9. Для приведения устройства в исходное состояние подается сигнал на управляющий вход 17. При этом счетчики 2, 6 и 12, триггер 22, делитель 24 блока 8 управления, и триггер 36 блока 7 сравнения сбрасываются в нулевое состояние, триггер 40 блока 7 сравнения устанавливается в единичное состояние, обеспечивается установка в начальное состояние формирователя 11 (формирователь 11 может быть реализован на регистре сдвига с линейной цепью обратной связи), упрощенная структурная схема которого приведена на фиг ° 4 . Перепадом 1-0 с выхода одновибратора 42 обеспечивается запись в регистр сдвига 43 начального кода 111...1, а также выдача формирователем 11 текущего признака

С = 1 кода поля Галуа (перепадом

1,0). В этом состоянии сигналом с первого выхода триггера 22 блока 8 управления (фиг. 5.2) разрешается работа мультиплексора 3, блоки 4 и 5 памяти по входу записи — считывания переводятся в режим записи, сигналом с второго выхода триггера 22 (четвертого выхода блока 8 управления) разрешается работа ключей 10 и запрещается работа второго коммутатора 14.

Таким образом, в исходном состоянии с выхода формирователя 11 на первый вход второго коммутатора 14 поступает признак С 1 кода поля Галуа, t на второй вход коммутатора 14 поступает бит признака Т существенности цифрового отсчета входного сигнала (Т = 1), а на остальные q-e входы

9529

5 164 коммутатора 14 поступает текущий двоичный код входного сигнала соответствующего канала (где q - количество битов параллельного двоичного кода).

После снятия сигнала с управляющего ,.входа 17 устройства оно продолжает работу под действием генератора 21 импульсов блока 8 управления, В каждом кадре дальнейшая работа устройства осуществляется на протяжении двух циклов; цикл аналого-циАрового преобразования длительность которого со- .

Ф ставляет Т < = (k + 2) ° 2, где Д вЂ” длительность периода следования им пульсов генератора 21; цикл считывания и сжатия, длительность которого составляет Т = (k + 2)ht. В первом цикле первого кадра при нулевом коде на выходах второго счетчика б и последовательном наращивании двоичного кода первого счетчика 2 происходит синхронное изменение адресов блоков

4 и 5 памяти и каналов коммутации мультиплексора 3. В каждом канале, в котором иву с ПВых,мда, фор ируется сигнал с выхода мультиплексора 3, который поступает на третий вход блока 8 управления. При этом формирователь 27 импульса блока 0 обеспечивает формирование импульсного сигнала, который с блока 0 управления поступает на входы управления блоков

4 и 5 памяти.

Таким образом, в процессе наращивания двоичного кода во втором счетчике 6 происходит последовательная запись кодов измеренных значений в соответствующие адреса блоков 4 и 5 памяти. Второй цикл работы устройства наступает .в момент переполнения второго счетчика б, на выходе переноса которого формируется импульс (фиг. 5а), который перебрасывает триггер 22 блока 8 управления s единичное состояние. При этом сигналы с первого и второго. выходов триггера.

22 соответственно запрещают работу мультиплексора 3, по входу записисчитывания переключают блоки 4 и 5 намяти в режим считывания, запрещают работу ключей 10 и разрешают работу второго коммутатора 14. Поскольку на протяжении длительности первого кадра отсчеты входных сигналов по всем каналам должны быть существенными, сигналом с второго выхода триггера

22 (четвертый выход блока 8 управления) обеспечивается подтверждение первоначального единичного состояния триггера 40 блока 7 сравнения кодов, т.е. Т = 1 (фиг.5в), а сигналом с

5 шестого выхода блока 8 управления (Аиг. 5к) обеспечивается доступ выходных данных с первого блока 4 памятй на последние q выходов первой информационной шины второго коммутатора 14. С третьего выхода блока 8 управления на управляющий вход первого блока 4 памяти поступает импульсный сигнал (на фиг. 5e — разрешающий уровень), обеспечивающий считывание

15 данных. Таким образом на (q + 2) входах первой информационной шины второго коммутатора 14 присутствуют биты текущего признака кода поля Галуа

С .= 1, бит признака существенности

20 отсчета Т = 1, а также двоичный

q-битовый код i ro канала, На первый и второй входы второй информационной шины второго коммутатора 14 подано напряжение "1", а на остальные q

25 входов — логический уровень, соответствующий текущему признаку Т, существенности отсчета. Работа. коммутатора

14 разрешается на время длительности интервала считывания и сжатия Т

30 Под действием тактовых импульсов третий счетчик 12 осуществляет опрос информационных шин второго коммутатора 14. При этом на выходе 18 устрой ства поступает бит — ориентированный код, а на управляющий выход 19 устрой35 ства — импульсный сигнал, сигнализирующий о наличии бита информационной посылки. За счет того, что на первых двух входах второй информационпой

40 шины второго коммутатора 14 присутствует уровень "1", биты признаков

Г. и Т всегда воспринимаются внеш1 4 ними устройствами, а биты двоичного кода входных сигналов воспринимаются

45: только в случае наличия уровня "1"

:на выходе блока 7 сравнения, т.е. когда признак Т; = 1. Поэтому, в частности, внешние устройства воспринимают бит — ориентированный код а,1(Х Д.

С выхода переполнения первого счетчика 2 сигнал переполнения через второй элемент ИЛИ 20 блока 8 управления поступает на второй вход триггера 22. и переводит его.в нулевое состояние.

Поэтому устройство опять переходит в режим аналого-циАрового преобразования и записи информации в тот блок памяти, в котором не зафиксирован

1649529

7 текущий существенный отсчет. Для определения момента записи информации в соответствующий блок памяти s блоке 8 управления из сигнала снимаемо5

ro с выхода блока 7 сравнения (Фиг.5в), а также из сигналов, снимаемых с выходов делителя 24 частоты (Фиг. 5г,д), происходит формирование сигналов, раз,решающих прохождение импульсных сигна-. лов с выхода Формирователя 27 на управляющие входы блоков 4 и 5 памяти (на Фиг. 5е — разрешающий сигнал для первого блока 4 памяти, на Фиг. 5ж— для второго блока 5 памяти). При Формировании устройством кода

G 1ф1110вОС41 Х „ 410е! f «jG10ûâ1(;4) фиг. Я запись ияаормапии в первый рпоя 4 памяти осрпествпявтся в первом и четвертом кадрах, а запись ин20 формации во второй блок 5 памяти— во втором, третьем, пятом и шестом кадрах. Формирование текущих битов

С« признаков кода поля Галуа (последующих после С ) осуществляется по спаду импульсов, снимаемых с первого выхода триггера 22 (Фиг. 5б).

Во втором -кадре в начале цикла аналого-цифрового преобразования под действием импульсов, снимаемых с вьг хода переноса первого счетчика 2, второй счетчик 6 последовательно изме няет свое состояние начиная с нулевого, которое сохранялось с момента наступления цикла считывания и сжатия предыдущего кадра. Сохранение необходимого нулевого состояния вто; рого счетчика 6 достигается за счет ,.блокировки поступления импульсов переноса первого счетчика 2 сигналом, соответствующим. уровню "О" р снима- 40 емого с второго выхода триггера 22, Элемент 26 задержки. необходим для уверенной блокировки импульса переноса первого счетчика 2 в конце цикла считывания и сжатия, В начале последующих циклов измерения начиная со второго сигналом, снимаемым с второго выхода триггера 22 (четвертый выход блока 8 управления), триггер 36 блока 7 сравнения перево- 50 дится в единичное состояние. В результате разрешается прохождение импульсов переноса третьего счетчика 12 на второй вход триггера 40. Поэтому в начале последующих циклов считывания 55 и сжатия триггер 40 находится в нуле- 1 вом состоянии. Для определенного состояния первого счетчика 2 в процессе сравнения двоичнык кодов элементом 35 сравнения кодов на ее выходе появится сигнал, соответствующий те кущему признаку Т,„ существенности отсчета. Поэтому единичный уровень выходного сигнала элемента 35 переводит триггер 40 в единичное состояние. При переходе первого счетчика

2 в последующее состояние триггер

40 импульсом переноса третьего счетчика 12 переводится в нулевое состояние. Элемент 39 задержки необходим для незначительной задержки выходного сигнала элемента 35 сравнения кодов.

Второй существенный отсчет (фиг. 5) считывается с второго блока 5 памяти к первой группе входов второго коммутатора 14 в блоке 8 еуправления из сигналов, снимаемых с выхода блока 7 ср"внения. С первого выходного сигнала елителя 24 Формируется раэрешающ1 сигнал (Фиг. 5.9), поступающий на второй управляющий вход коммутатора 13.

Таким образом, за счет Формирования устройством признаков кодов поля

Галуа, которые характеризуются глубокой рекурсивностью и обеспечивают плотную упаковку неповторяющихся двоичных кодов, а также за счет формирования признаков информативности отсчетов сигналов осуществляется сжатие многоканальной информации. При ! этом решается проблема временной при:вязки существенных отсчетов и сокра,щается служебная информация до двух битов.

Формула и з обр ет ения

1, Устройство для ввода инФормации, содержащее компараторы, первый и второй счетчйки, блок управления, цифроаналоговый преобразователь, мультиплексор, первый блок памяти, ключи, выход цифроаналогового преобразователя соединен с управляющими входами компараторов, входы которых являются информационными входами устройства, выходы компараторов соединены с информационными входами мультиплексора, адресные входы которого соединены с информационными выходами первого счетчика и адресными входами первого блока памяти, информационные входывыходы которого соединены с входами цифроаналогового преобразователя и выходами ключей, вход начальной ус"

9 1649529 1О тановки блока управления и входы сброса первого и второго счетчиков являются управляющим входом устройства, второй выход блока управления соединен с управляющим входом мульти5 плексора и входом записи-считывания первого блока памяти, третий выход блока управления соединен с управляющим входом первого блока памяти, четвертый выход блока управления соединен с управляющими входами ключей, выход переполнения первого счетчика соединен с первым входом выбора режима блока управления Выход мультиплексора соединен с информационным входом блока управления, выход переполнения и информационные выходы второго счетчика соединены с вторым входом выбора режима блока управления и.информационными входами ключей соответственно, о т л и ч а ю щ е е с я тем, что, с целью сокращения избыточности выводимой информации, в него введены второй блок памяти, блок сравнения, формиро- 25 ватель признака кода, третий счетчик, первый и второй коммутаторы, элемент

И, выход которого является управляющим выходом устройства, первый выход блока управления соединен со счетным вхо- 0 дом третьего счетчика и первым входом элемента И, входы сброса третьего счетчика, формирователя признака кода и блока сравнения соединены с входом сброса первого счетчика, вход переполнения третьего счетчика соединен со счетным входом первого счетчика и первым управляющим входом блока сравнения, информационные выходы первого счетчика соединены с адресными входа40 ми второго блока памяти, информационные входы-выходы первого блока памяти соединены с информационными входами первой группы блока сравнения и первого коммутатора, информационные входы-выходы второго блока памяти соединены с информационными входами второй группы блока сравнения и первого коммутатора и выходами ключей,пятый выход блока управления соединен со счетным, входом второго счетчика, шестой выход - с первым управляющим входом первого коммутатора, восьмой выход— с управляющим входом второго блока памяти, вход записи-считывания которого соединен с вторым выходом блока Я управления и управляющим входом формирователя признака кода, выход которого соединен с первым информационным входом второго коммутатора, четвертый выход блока управления соединен с управляющим входом второго коммутатора и вторым управляющим входом блока сравнения, выход которого соединен с управляющим входом блока управления, вторым информационным входом и информационными входами первой группы второго коммутатора, информационные входы второй группы которого соединены с выходами перво"о коммутатора, адресные входы которого соединены с информационными выходами третьего счетчика, первый выход второго коммутатора является информационным выходом устройства, второй выход коммутатора соединен с вторым выходом

;элемента И, информационные входы ! третьей группы второго коммутатора ,подключены к шине логической единицы, 2. Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок сравнения содержит элемент сравнения, первый и второй триггеры, элемент ИЛИ, элемент И, элемент задержки,„ первый вход элемента ИЛИ и вход сброса первого триггера являются входом сброса блока, выход элемента ИЛИ через элемент задержки соединен с входом установки в "1" второго триггера, выход которого является выходом блока, входы первой и второй групп элемента сравнения являются информационными входами первой и второй групп блока,выход элемента сравнения. соединен со вторым входом элемента. ИЛИ, вход установки в "1" первого триггера является вторым управляющим входом блока, выход первого триггера соединен с первым входом элемента И. второй вход которого является первым управ1дяющим входом блока, выход элемента И соединен с входом сброса второго триггера.

3. Устройство по л. 1, о т л ич а ю щ е е с я тем, что блок управления содержит генератор импульсов, триггер, элемент задержки, формирователь импульса, четыре элемента ИЛИ, шесть элементов И и делитель частоты, выход генератора импульсов соединен с первым входом первого элемента И -и является первым выходом блока, первый вход первого элемента ИЛИ и вход сброса делителя частоты являются входом начальной установки блока, второй вход первого элемента ИЛИ и первый вход второго элемента И являются

i649529 первым входом выбора режима блока, выход первого элемента ИЛИ соединен с входом сброса триггера, прямой вход которого соединен с вторым входом первого элемента И и является вторым выходом блока, выход первого элемен та И соединен с первым входом второго элемента ИЛИ, второй вход которого являетС информационным входом блока, выход второго элемента ИЛИ соединен с входом формирователя импульса, выход которого соединен с первыми входаьа пятого и шестого элементов И,,выходы которых являются третьим и восьмым выходами блока соответственно, инверснкй выход триггера соединен с входом элемента задержки и является четвертым выходом блока, выход элемента задержки соединен с вторым входом второго элемента И, вы10 ход которого является пятым выходом блока, вход установки в "1" триггера является вторым входом выбора режима, информационный вход делителя частоты, первые входы третьего и четвертого элементов И и третьего и четвертого элементов ИЛИ являются управляющим входом блока, прямой выход делителя частоты соединен с вторыми входами четвертого элемента И и третьего элемента ИЛИ, инверсный выход делителя частоты соединен с вторыми входами третьего элемента И и четвертого элемента ИЛИ, выходы третьего и четвертого элементов И являются шестым и седьмым выходами блока соответственно, третий и четвертый выходы элементов ИЛИ соединены с вторыми входами пятого и шестого элементов И соответственно.

1649529

Составитель И. Карнова

Текред Л. Олийнык Корректор А. Обручар

Редактор Л. Пчолинская

Заказ 1522 Topaz 415 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент" ° г. Ужгород, ул. Гагарина, 101