Устройство поиска числа

Иллюстрации

Показать всеРеферат

Изобретение относится к элементам дискретной автоматизации и вычислительной техники и может быть использовано при реализации технических средств цифровых систем контроля и управления. Цель изобретения - повышение быстродействия. Устройство поиска числа содержит схему сравнения 1, реверсивный счетчик 2, формирователи адреса 3,4, триггеры 5,6, элемент ИЛИ 7, первый элемент ИЛИ-ИЕ 8, элементы И 9, 10, 11, элемент задержки 12, мультиплексор 13. Каждый формирователь адреса 3, 4 содержит счетчик, группу сумматоров по модулю два, элемент ИЛИ-НЕ, элемент задержки, элемент И, элемент ИЛИ. С приходом положительного перепада тактового импульса адрес числа, хранящегося в массиве информации, выдает первый формирователь адреса 3, а с приходом отрицательного перепада второй формирователь адреса 4. Мультиплексор 13 по сигналам с тактового входа 19 устройства попеременно подключает к выходным шинам то выходы первого формирователя 3 адреса, то выходы второго формирователя 4 адреса. При этом за один тактовый импульс происходит формирование двух чисел, хранящихся в массиве ( информации, считывание этих чисел и последовательное их сравнение с задан- 3 ным числом. 1 з.п.ф-лы, 3 ил. о to 2 CD s

QQ03 Q09ETCHHX

ЬЗЗ

RECT%ËÈÍ,.SUm (gg)g G 06 F 7/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ASTOPGHOMY СВИДЕТЕЛЬСТВУ

1б и

15 и

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО И306РЕТЕНИЯМ И ОТКРЫТИЯМ

flPH ГКНТ СССР

1 (21) 4666356/24 (22) 27.03.89 (46) 15.05.91. Бюл. Р 18 (72) С,Н.Лобков, И.Т.Мирзоев, В П.Ткачев, Г.И.Климкович, С.А.Гагкуев и С.В.Орлов . (53) 681. 325.5(088 ° 8) (56) Авторское свидетельство СССР

В 830373, кл.- G 06 F7/02,,1978.

Авторское свидетельство СССР

Р 1117630, кл. 6 06 F 7/02 ° 1983 ° Ф (54) УСТРОЙСТВО ПОИСКА ЧИСЛА (57) Изобретение относится к элементам дискретной автоматизации и вычис,лительной техники и может быть использовано при реализации технических средств цифровых систем контроля и управления. Цель изобретения — повышение быстродействия. Устройство поиска числа содержит схему сравнения 1, реверсивный счетчик 2, формирователи адреса 3,4, триггеры 5,6, элемент

2

ИЛИ 7, первый элемент ИЛИ-llF. 8, элементы И 9, 10, 11, элемент задержки

12, мультиплексор 13. Каждый формирователь адреса 3, 4 содержит счетчик, группу сумматоров по модулю два, эле- мент ИЛИ-HF., элемент задержки, элемент И, элемент ИЛИ. С приходом положительного перепада тактового импульса адрес числа, хранящегося в массиве информации, выдает первый формирователь адреса 3, а с приходом отрицательного перепада второй формирователь адреса 4. Мультиплексор 13 по сигналам с тактового входа 19 устройства попеременно подключает к выходным шинам то выходы первого формирователя

3 адреса, то выходы второго формирователя 4 адреса. При этом за один тактовый импульс происходит формирование двух чисел, хранящихся в массиве информации, считывание этих, чисел н последовательное их сравнение с задан- 2 ным числом. 1 з.п.A-лы, 3 ил.

1649531

Изобретение относится к элементам фюскретной автоматизации и вычисли тельной техники и может быть использовано при реализации технических средств цифровых систем контроля и управления.

Цель изобретения - повышение быстродействия устройства.

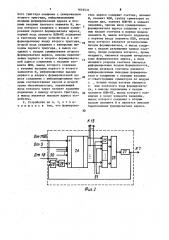

На фиг. 1 изображена структурная схема устройства поиска числа; на фиг. 2 - функциональная схема кажцого формирователя адреса; на фиг, 3 — временная диаграмма работы устройства.

I ! .

Устройство содержит схему 1 сравнения, реверсивный счетчик 2, формирователи 3 и 4 адреса, триггеры 5 и 6, элемент ИЛИ 7, элемент ИЛИ-НЕ 8, элементы И 9-1 1, элемент. 12 задержки, мультиплексор 13, входы 14-20 и Bbtxo ды 21-23.

Каждый формирователь адреса состо1 ит. из счетчика 24, группы сумматоров .

25 по модулю два, элемента ИЛИ-НЕ 26, .элемента 27 задержки, элемента И 28, 25 элемента ИЛИ 29, входов 30 установки начального кода и входов 31 установ.— ки конечного кода.

Устройство работает следующим образом.

Устройство поиска числа предназначено для работы в одном из двух режимов: поиска ближайшего большего или ближайшего меньшего числа по отношению к заданному.

Например, для поиска ближайшего большего числа по отношению к заданному, которое поступает на входы 15, подается сигнал на вход 16 для подготовки элемента И 9 и соответствен40 но реверсивного счетчика 2 к работе в режиме сложения. Затем .подается

:.сигнал на вход 18, в результате чего заданное число переписывается в реверсивный счетчик 2, триггер 5 устанавливается в нулевое состояние, фор45 мирователи 3 и 4 адреса устанавливаются в исходное состояние. Исходное

- состояние формирователей 3 и 4 адреса должно быть таким, чтобы с приходом тактовых импульсов на их входы суммирования формирователь 3 адреса начинал выцавать адреса чисел, хра, нящихся в массиве информации, начиная с 1 и до n/2, а формирователь 4 адреса — с и/2 + 1 и до и (где п - 55 количество чисел в массиве информации). В случае нечетного количества чисел, хранящихся в массиве информапоследний адрес,. выдаваемый фор-. мирователем 3, и первый адрес, выдаваемый формирователем 4, совпадают, т.е. формирователь 3 выдает адреса и+1 с 1 и до —, формирователь 4— и+1 с

В каждом конкретном случае, в зависимости от количества чисел в массиве информации, можно изменять количество адресов, выдаваемых формирователями 3 и 4 адреса, с помощью входов

30 установки начального кода и входов 31 установки конечного кода. При этом необходимо учитывать, что при подаче сигнала на установочные входы формирователей 3 и 4 адреса происходит запись в них чисел, характеризующих исходные состояния. Эти числа обусловлены сигналом "0" с прямого выхода триггера 5, поступающего на младший разряд декрементирующего счетчика 24, и двоичным кодом, поступающим на остальные разряды с входов

30 установки начального кода.

Двоичный код, подаваемый на входы

31 установки конечного кода, обусловливает последний адрес, выдаваемый формирователями 3 и 4. С выдачей последнего адреса формирователями 3 и 4 на выходе элемента ИЛИ-НЕ 26 возникает сигнал "1", который через эле-! 3 мент 27 задержки за время — Т(Та Т (где Т вЂ” период тактового импульса) поступает на второй вход элемента

И 28. С приходом очередного тактового импульса с входа 18 счетчик 24 выдает опять первый адрес, минуя исходное состояние. Это происходит потому, что при записи числа в счетчик 24 на вход младшего разряда подается сигнал "1" с прямого выхода триггера 5, который переходит в единичное состояние с началом работы устройства, Команда на поиск числа поступает на вход 20 запуска, в результате которой триггер 5 переводится в единичное состояние и разрешает прохождение тактовых импульсов с входа 19 через триггер 6, элемент И 11 и элемент

ИЛИ-HF. 8. Сигнал "1" поступает также с прямого выхода триггера 5 на информационные входы формирователей 3 и 4 адреса. В качестве триггера 5 исполь зуется стандартный D-rpeprep с входами

5 164953 установки в "1" и "0", а вкачестве триггера 6 — D-триггер типа защелки.

С приходом положительного rteperraда первого тактового импульса формирователь 3 адреса. переходит в очеред5 ное состояние и выдает свой первый адрес числа. Этот адрес, за счет того, что в данный момент с выхода триггера 6 приходит сигнал "1" на управля!

О ющий вход мультиплексора 13, поступает на выходы 23 устройства; происходит считывание числа из массива информации. Считанное число поступает на входы 14 устройства и сравнивается с заданным числом в схеме 1 сравнения. Если сравнения не произошло, то с приходом отрицательного перепада первого импульса формирователь 4 адреса переходит в очередное состояние 20 и выдает свой первый адрес числа.

Этот адрес за счет того, что в данный момент с выхода-триггера 6 приходит сигнал "0" на управляющий вход мультиплексора 13, поступает на 25 выходы 23 устройства; происходит считывание очередного числа из массива информации. Это число также сравнивается с заданным. Таким образом, с приходом каждого тактового импульса происходит формирование двух адресов, считывание по ним чисел и последовательное сравнение их с заданным числом. Поочередное подключение информационных выходов формирователей 3 и 4 адреса к выходам 23 устройства происходит за счет прихода сигналов на управляющий вход мультиплексора 13, а эти сигналы меняются в зависимости от прихода положительного или отрицательного потенциала очередного тактового импульса.

Если после сравнения всех чисел, хранящихся в массиве информации, нет решения, то с выхода переполнения

45 формирователя 3 или 4 адреса (зависит от того, какой формирователь стал раньше выдавать адреса) прихо дит сигнал в виде положительного перепада импульса переполнения на ! один из входов элемента ИЛИ 7 и происходит увеличение заданного числа

I на единицу, а затем процесс повторяется.

При сравнении чисел с выхода схемы !

1 сравнения поступает сигнал на вход

55 синхронизации триггера 5 и он переводится в нулевое состояние. В результате этого запрещается прохождение

6 тактовых импульсов на формирователи

3 и 4 адреса и мультиплексор 13, на выходе 21 конца работы появляется сигнал, что число найдено, на выходах 22 — значение числа в двоичном коде, на выходах 23 — адрес, в котором хранилось число в массиве информации.

Для поиска ближайшего меньшего числа по отношению к заданному сигнал подается на вход 17, в результате чего реверсивный счетчик 2 переводится в режим вычитания и на его выходе формируется убывающая последовательность чисел в двоичном коде начиная от заданного числа, Формула изобретения

1. Устройство поиска числа, содержащее схему сравнения, реверсив- ный счетчик, первый триггер, три элемента И, причем входы анализируемого числа устройства соединены с входами первой группы схемы сравнения, выход которой является выходом конца работы устройства, входы вто1 рой группы которой соединены с выходами разрядов реверсивного счетчика и являются выходами числа устройства, информационные входы реверсивного счетчика являются входами заданного числа устройства, а входы сложения и вычитания подключены к выходам соответственно первого и второго элементов И, первые входы которых являются входами задания выборки соответственно ближайшего большего и ближайшего меньшего чисел устройства, вход записи которого соединен с входом записи реверсивного счетчика, тактовый вход устройства подключен к первому входу третьего элемента И, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены второй триггер, элемент ИЛИ, элемент ИЛИ-НЕ, элемент задержки, два формирователя адреса и мультиплексор, причем вход запуска устройства подключен к входу установки в единичное состояние первого триггера, информационный вход которого соединен с входом логического нуля устройства, синхровход соединен с выходом схемы сравнения, вход установки в нулевое состояние подключен к входу записи устройства и установочным входам формирователей адреса, а прямой выход пер0m

Фиг.2

7 16495 ного триггера соединен с синхровходом второго триггера, информационными входами формирователей .адреса и вторыми входами третьего элемента И, вь ход которого соединен с входом сумми« рования первого формирователя адреса, первый вход элемента ZUIH-HH подключен к тактовому входу устройства и к ин» формационному входу второго триггера, второй вход соединен с инверсным выходом первого триггера, а выход соецинен с входом суммирования второго формирователя адреса, выходы переполнения первого и второго формирователей адреса соединены с входами элемента ИЛИ, выход которого соединен с вторыми входами первого и второго элементов И, информационные выходи первого и второго формирователей адреса соединены с информационными входами соответственно первой и второй групп мультиплексора, управляющий вход которого через элемент задержки подкпючен к выходу второго триггера, . а выход является выходом адреса устройства.

2. Устройство по п. 1, о т л ич а ю щ е е с я Фем, что формирователь адреса содержит счетчик, элемент

И, элемент ИЛИ, группу сумматоров по модулю два, элемент ИЛИ-НЕ и элемент задержки, причем вход суммирования формирователя адреса соединен с счетным входом счетчика и первым входом элемента И, выход которого подключен к первому входу элемента ИЛИ, второй вход которого является установочным входом формирователя, а выход соединен с входом разрешения записи счетчика, входы разрядов которого, кроме младшего, являются входами начального кода формирователя адреса, а вход младшего разряда счетчика является информационным входом Аормироват ч, выходы разрядов счетчика являются информационными выходами формирователя и соединены с первыми входами с .лтветствуюших сумматоров Ilo модулю д, вторые входы которых являются в: ами конечного кода формирователя, а выходы подключены к входам элемента ИЛИ-HE выход которого подключен к входу элемента задержки, выход которого соединен с вторым входом элемента И и является выходом переполнения формирователя адреса.

1649531 ива .вакх

Эмк,ВВИДЕ

Редактор Л. Пчопинская

Корректор Н. Король

; Заказ 1522

Производствейно-издательский комбинат "Патеит", г. Улсгород, ул. Гагарина, 101

Ьъй. ßÐúï.

3 нне.ввп.

ВНИИПИ Государственного

113035, Составитель Е. Иванова

Техред Л. Олийнык

Тирал 406 Поцписное комитета по изобретениям и открытиям при ГКНТ СССР

Москва Ж-35, Раушская наб., д. 4/5