Устройство микропрограммного управления

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве контроллера АСУ технологическими процессами. Целью изобретения является повышение достоверности функционирования устройства за счет контроля правильности последовательности логических условий. Предлагаемое устройство обеспечивает микропрограммное управление вычислительными системами. При этом обеспечивается достоверный контроль исходного состояния устройства управления и использование результатов контроля в дальнейшей работе устройства, повышается оперативность управления и уменьшается объем памяти устройства управления . Устройство содержит блок постоянной памяти, регистры адреса, микроопераций, триггер пуска, коммутатор, первый мультиплексор, генератор тактовых импульсов, элемент ИЛИ, демультиплексор, регистр логических условий, второй мультиплексор , блок сумматоров по модулю два, элемент И,первый и второй триггеры управления , триггер ошибки. 2 ил. (Л С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)з 6 06 F 9/22, 11/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4437232/24 (22) 06.06.88 (46) 15.05.91. Бюл. N 18 (72) В.С.Харченко, Г.Н.Тимонькин, С,Н.Ткаченко и С.В.Терещенков (53) 621.325 (088,8) . (56) Авторское свидетельство СССР

¹ 1007106, кл. G 06 F 9/22, 1981.

Майоров С.А, и Новиков Г,И. Структура электронных вычислительных машин.

Л,:Машиностроение, 1979, с,312-314.

Авторское свидетельство СССР

¹ 1252759, кл, G 05 В 19/18, 1987..

Авторское свидетельство СССР

N. 1140121. кл. G 06 F 11/00, 1986. (54) УСТРОЙСТВО МИКРОПРОГPAMMHOГО УПРАВЛЕНИЯ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве контроллера АСУ технологическими процессами, Целью изоИзобретение относится к автоматике и вычислительной технике и может быть использовано в качестве контроллера АСУ технологическими процессами.

Целью изобретения является повышение достоверности функционирования устройства за счет контроля правильности последовательности логических условий.

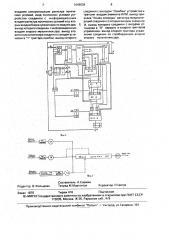

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 — представлен пример алгоритма работы.

Устройство содержит блок 1 постоянной памяти, регистры адреса 2 и 3 микроопераций, триггер 4 пуска, коммутатор 5, первый

„„Я3„„1б49539 Al бретения является повышение достоверности функционирования устройства за счет контроля правильности последовательности логических условий. Предлагаемое устройство обеспечивает микропрограммное управление вычислительными системами.

При этом обеспечивается достоверный контроль исходного состояния устройства управления и использование результатов контроля в дальнейшей работе устройства, повышается оперативность управления и уменьшается объем памяти устройства управления. Устройство содержит блок постоянной памяти, регистры адреса, микроопераций, триггер пуска, коммутатор, первый мультиплексор, генератор тактовых импульсов, элемент ИЛИ, демультиплексор. регистр логических условий, второй мультиплексор, блок сумматоров по модулю два, элемент И,первый и второй триггеры управления, триггер ошибки. 2 ил. мультиплексор 6, генератор 7 тактовых импульсов, элемент ИЛИ 8, демультиплексор

9, регистр 10 логических условий, второй мультиплексор 11, блок 12 сумматоров по модулю два, элемент И 13, первый 14 и второй 15 триггеры управления, триггер 16 ошибки, вход 17 кода операций, выход 18 микроопераций, вход 19 внешнего останова, вход 20 пуска устройства, выход 21 ошибки.

Устройство может работать в трех режимах; "Обучение", "Контроль" и "Управление".

Режим "Обучение" предназначен для записи в соответствии с микропрограммой

1649539

30

40

55 информации в память (регистр логических условий) об исходном состоянии устройства с тем, чтобы в дальнейшем иметь воэможность использовать эту информацию в коде выполнения последующих микропрограмм.

Режим "Контроль", предназначен для проверки соответствия записанной информации в регистр логических условий логическим условиям на входе устройства.

Микропрограмма режима "Контроль" может либо повторять микропрограмму "Обучение" (вместо признака а1 используется признак а2, см. фиг.1), либо отличаться от нее. Под этим понимается то, что порядок выполнения микрокоманд в микропрограмме "Контроль" может не совпадать с порядком в микропрограмме "Обучение", а также может контролироваться правильность записи не всех логических условий, а лишь некоторых из них. Однако, обращенный к логическим условиям, не используемым в микропрограмме "Обучение", быть не должно, так как это может привести к ошибочному отключению устройства и выдаче сигнала "Ошибка".,Режим "Контроль" должен следовать за режимом "Обучение", тэк как в течение времени значения логических условий меняются и большой временной разрыв между этими режимами может также привести к ошибочному отключению устройства и выдаче сигнала "Ошибка", или в режиме "Контроль" должны использоваться логические условия, изменения которых происходят значительно медленнее, чем время работы устройства. Режим "Контроль" также позволяет получить косвенную информацию о правильности функционирования устройства управления в целом, . Режим "Управление" — основной режим работы устройства предназначен для управления объектом с помощью микроопераций, посылаемых в соответствии с записанными в памяти устройства микропрограммами.

В режиме работы "Управление" в микрокомандах ветвления может использоваться признак а (контроля), если контролируемое логическое условие использовалось в режиме "Обучение" и его значение в сравнении со временем функционирования устройства изменяется медленно. Это повышает достоверность работы устройства и не влияет на время его работы.

В исходном состоянии все элементы памяти установлены в "0". В единичном состоянии находится только один триггер регистра 3, которому соответствует выход микрооперации "Конца команды", (Цепи установки исходного и сходного состояний условно не показаны).

Работа устройства начинается после поступления на вход 20 сигнала "Пуск", по которому устанавливается в единичное состояние триггер 4 пуска, По первому тактовому импульсу с выхода 7.1 генератора 7 в регистр 2 заносится код с входа.-17. Этот код записывается в регистр 2 через коммутатор 5, на управляющий вход которого подается единичный сигнал с выхода регистра 3 микрооперэций.

В блоке 1 памяти формируется микрокоманда, соответствующая пришедшему адресу, в поле 1.2 которой формируется признак а1 режима "Обучение", триггер 14 устанавливается в единичное состояние и регистр 10 готов к приему информации, Затем по тактовому импульсу с выхода

7.2 генератора 7 в регистр 3 заносится код микрооперации. По заднему фронту этого импульса исчезает единичный сигнал на выходе "Конец команды" регистра 3 и в коммутаторе 5 закрывается первый и открывается второй информационный вход. По следующему тактовому импульсу адрес следующей микрокоманды, считываемый с выхода 1.5 блока 1 (немодифицируемэя часть адреса), и с выхода 1.4 через мультиплексор

6 (модифицируемая часть) записывается в регистр 2 адреса.

По второму тактовому импульсу коды микроопераций заносятся в регистр 3 и далее работа устройства продолжается аналогично описан ному.

В микрокомандах ветвления код логических условий поступает с поля 1.3 блока 1 в мультиплексор 6 и производит модификацию младшего адресного разряда в соответствии со значением логического условия.

Также код логического условия поступает на адресный вход демультиплексора 9, который пропускает синхроимпульс 7,1 на те выходы демультиплексора, номер которого указан в коде логических условий. Так как выходы демультиплексора 9 соединены с синхровходами регистра 10, то в регистр 10 будут записаны все значения логических условий, используемых данной микропрограммой. Данные, поступающие на второй информационный вход мультиплексора 6, информирует об исходном состоянии устройства управления. В последней микрокоманде микропрограммы имеется признак конца команды, который устанавливает в единичное состояние соответствующий триггер регистра 3 микроопераций, единичный сигнал поступает на управляющий

1649539

10

20

55 вход коммутатора 5 и готовит его к приему нового кода операций.

Таким образом, в этом режиме фиксируется (идентифицируется) исходное состояние объекта до начала выполнения всех операций. В этом режиме "Контроль" на выходе 1.2 блока 1 памяти формирует признак а2. Этим признаком триггер 15 управления устанавливается в единичное состояние и разрешает прохождение информации через мультиплексор 11. 8 микрокомандах ветвления код логических условий с поля 1.3 блока 1, поступая на адресный вход мультиплексора 11, формирует значение с выхода того сумматора по модулю два, номеру которого соответствует поступивший код. Поэтому в процессе выполнения микропрограммы будут опрошены все и ,только те сумматоры по модулю два, номерам которых соответствуют адреса логических условий, используемых в данной микропрограмме. Если. на выходе мультиплексора 11 появится единица, что соответствует ошибке, то триггер 16 ошибки устанавливается в единичное состояние и нэ выходе 21 появляется сигнал "Ошибка", тогда единичным сигналом, прошедшим через элемент ИЛИ 8. триггер 4 пуска устанавливается в "0", генератор 7 тактовых импульсов прекращает работу, Если в процессе повторения микропрограммы

"Управления" значения логических условий совпадут, то признаком конца команды коммутатор 5 устанавливается в готовность к приему следующего кода операции.

Режим работы "Управление" является основным режимом работы устройства. В этом режиме признаки а и э не вырабатываются и следовательно запись логических условий в регистр 10 и их прохождение через мультиплексор 11 не происходит.

В остальном алгоритм работы устройства аналогичен описанному в режиме "Обучение".

По приходу последней микрокоманды последней микропрограммы. на выходе триггера конца работы в регистре 3 формируется единица, которая пройдя через элемент ИЛИ 8, поступает на нулевой вход триггера 4, и работа устройства прекращается.

Формула изобретения

Устройство микропрограммного управления, содержащее блок постоянной памяти, регистры адреса и микроопераций, коммутатор, первый мультиплексор, триггер пуска,. триггер ошибки, генератор тактовых импульсов, элемент ИЛИ, причем вход запуска устройства соединен с входом установки в "1" триггера пуска, выход которого е соединен со входом запуска генератора тактовых импульсов, первый и второй выходы которого соединены соответственно с входами синхронизации регистра адреса и регистра микроопераций, вход кода операции устройства и выход признака "Конец команды" регистра микроопераций соответственно соединены с первым информационным управляющим входами коммутатора, выход которого соединен с информационным входом регистра адреса, выход которого соединен с адресным входом блока постоянной памяти, выходы полей микроопераций, кода логического условия, модифицируемого разряда адреса и немодифицируемых разрядов адреса соответственно соединены с информационным входом регистра микроопераций. управляющим и первым информационным входом первого мультиплексора, старшими разрядами второго информационного входа коммутатора, выход первого мультиплексора соединен с младшим разрядом второго информационного входа коммутатора, выход регистра микроопераций является выходом микроопераций устройства, выход признака "Конец работы" регистра микроопераций и вход остэнова устройства соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с входом установки в "0" триггера пуска, вход логических условий устройства соединен со вторым информационным входом первого мультиплексора, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности функционирования за счет контроля правильности последовательности логических условий, устройство дополнительно содержит демультиплексор, регистр логических условий, блок сумматоров по модулю два, второй мультиплексор, первый и вторОй триггеры управления, элемент И, причем выход поля кода логических условий блока постоянной памяти соединен с управляющими входами демультиплексора и второго мультиплексора, первый и второй выходы признаков режима работы блока постоянной памяти соединены с входами установки в "1 первого и второго триггеров управления, выход первого триггера управления соединен с входом разрешения записи регистра логических условий, выход которого соединен с первым входом блока сумматоров по модулю два и третьим информационным входом первого мульти. плексора, первый выход генератора тактовых импульсов соединен с первым входом элемента И и информационным входом демультиплексора, выходы старших разрядов демультиплексора соединены поразрядно с

1 фиг,l

Составитель А.Сошкин

Редактор В.Фельдман Техред M.Mîðãåíòàë

Корректор О.Ципле

Заказ 1870 Тираж 416 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. ужгород, ул.Гагарина, 101 входами синхронизации регистра логических условий, вход логических условий устройства соединен с информационным входом регистра логических условий и со вторым входом блока сумматоров по модулю два, выход которого соединен с информационным входом второго мультиплексора, выход вто; рого мультиплексора соединен с входом уста новки в "1" триггера ошибки, выход которого соединен с выходом "Ошибки" устройства и третьим входом элемента ИЛИ, выход признака "Конец команды" регистра микроопераций соединен со вторым входом элемента

5 И, выход которого соединен с входами установки в "0" первого и второго триггеров управления, выход второго триггера управления соединен со стробирующим входом второго мультиплексора.