Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах электронных вычислительных машин.Целью изобретения является повышение надежности устройства . Устройство содержит блок памяти 1cm накопителями 2, регистр адреса 3, входной 4 и выходной 5 регистры числа, три регистра 6, 7, 8, два блока контроля 9, 10, блок кодирования 11, блок декодирования 12, блок коррекции 13 и мультиплексор 14. Надежность работы устройства повышается за счет обеспечения контроля адреса и входного числа по модулю 3, исправления одиночной ошибки и фиксации многократных ошибок для каждого из накопителей блока памяти, а также за счет возможности проверки блоков устройства. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 G 11 С 29/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4465454/24 (22) 26.07.88 (46) 15.05,91, Бюл. ¹ 18 (72) В.И.Косов, А.Д.Жучков, О.Г.Кирпаль, Б.Б,Кугутов, О.В.Росницкий, А.И.Савельев и В.Н,Степанян (53) 681.327 (088.8) (56) Авторское свидетельство СССР

¹ 11444466665566, кл. G 11 С 29/00, 1987, Авторское свидетельство СССР

¹ 1471225, кл. G 11 С 29/00, 1987, (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ (57) Изобретение относится к вычислительной технике и может быть использовано в

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах электронных вычислительных машин.

Целью изобретения является повышение надежности устройства.

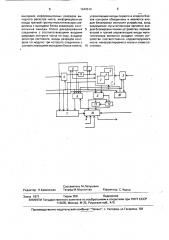

На чертеже показана функциональная схема устройства.

Запоминающее устройство с самоконтролем содержит блок памяти 1 с m накопителями 2, регистр адреса 3, входной регистр числа 4, выходной регистр числа 5, регистр состояния, включающий первый регистр 6, второй регистр 7, третий регистр 8, первый блок контроля 9, второй блок контроля 10, блок кодирования 11, блок декодирования

12, блок коррекции 13 и мультиплексор 14.

Блок памяти 1 содержит m накопителей 2. .Число разрядов каждого накопителя опре„„Я „„1649614 А1 запоминающих устройствах электронных вычислительных машин. Целью изобретения является повышение надежности устройства, Устройство содержит блок памяти 1 с m накопителями 2, регистр адреса 3, входной

4 и выходной 5 регистры числа, три регистра

6, 7, 8, два блока контроля 9, 10, блок кодирования 11, блок декодирования 12, блок коррекции 13 и мультиплексор 14. Надежность работы устройства повышается за счет обеспечения контроля адреса и входного числа по модулю "3", исправления одиночной ошибки и фиксации многократных ошибок для каждого из накопителей блока памяти, а также за счет возможности проверки блоков устройства. 1 ил. деляется требуемым количеством разрядов применяемого кода Хэмминга.

Устройство .работает в трех режимах: записи, считывания информации и контроля работоспособности блоков устройства. Перед началом каждого режима все блоки и узлы запоминающего устройства с самоконтролем устанавливаются в исходное состояние сигналом "Установка".

В режиме записи информации на регистр адреса 3 поступает код адреса, который передается на второй блок контроля 10, где производится контроль по модулю "3", если нет сигнала "Блокировка контроля".

Контроль производится сравнением приходящих вместе с кодом адреса контрольных разрядов с кодом, вырабатываемым вторым блоком контроля 10. В случае не совпадения этих кодов в первый регистр 6 выдается сигнал ошибки адреса, Код числа с входного

1649614 регистра числа 4 контролируется первым блоком контроля 9. Информация о наличии неисправности передается в другой разряд первого регистра 6. Одновременно код числа подается на блок кодирования 11, где формируются контрольные разряды кода

Хэмминга, и в накопитель осуществляется запись поступившего кода числа вместе с сформированными разрядами кода Хэмминга и контрольными разрядами по модулю "3". Контрольные разряды кода Хэмминга при этом фиксируются в третьем регистре

8, откуда они переписываются во второй регистр 7 в ту часть, которая отведена для разрядов данного накопителя 2 блока памяти 1. Информация из первого регистра 6 также передается во второй регистр 7. По сигналу "Чтение слова состояния информация о состоянии запоминающего устройства из второго регистра передается через мультиплексор 14 на информационные выходы устройства для контроля процессором или вычислительным устройством.

В режиме считывания код адреса контролируется по модулю как и в режиме записи. Считываемое число из блока памяти 1 поступает в выходной регистр 5 и осуществляется декодирование разрядов кода Хэмминга с помощью блока декодирования 12.

В случае возникновения одиночной ошибки в блоке коррекции 13 производится ее корректировка, В блоке декодирования, кроме того, формируются сигналы "Корректируе мая ошибка" или "Некорректируемая ошибка" для каждого из накопителей 2 блока памяти 1, которые передаются в соответствующие разряды первого регистра 6.

После этого, откорректированное число через мультиплексор 14 по сигналу "Чтение корректируемого числа" передается на информационные выходы устройства. Код числа непосредственно с выходного регистра 5 по сигналу "Чтение некорректируемого числа" поступает через мультиплексор 14 на информационные выходы устройства. В режиме контроля блоков и узлов запоминающего устройства контролируется работа блоков контроля 9 и 10, блока кодирования 11, блока декодирования 12 и блока коррекции 13. Контроль работы блоков контроля производится по правильности сформированных сигналов неисправности, записываемых в первый регистр 6. Контроль работы блока кодирования осуществляется передачей в слове состояния с третьего регистра 8 через второй регистр 7 контрольных разрядов кода Хэмминга. Контроль блока декодирования 12 и блока коррекции 13 осуществляется передачей корректируемого и некорректируемого чисел

10

35 ми устройства, адресные входы блока па40

55 через мультиплексор 14 непосредственно с выходного регистра 5 и блока коррекции 13.

При контроле работоспособности накопителей 2 блока памяти возможна фиксация ошибок в каждом из m накопителей 2, так как контрольные разряды для каждого накопителя 2 записываются отдельно Во второй регистр 7 и информация о корректируемых и некорректируемых ошибках выдается в первый регистр 6 неисправности также отдельно для каждого накопителя 2. I

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее блок памяти, регистр адреса, входной и выходной регистры числа, блок кодирования, блок декодирования и блок коррекции, входы первой группы которого соединены с выходами блока декодирования, входы которого соединены с вы-. ходами информационных и контрольных разрядов выходного регистра числа, входы второй группы блока коррекции соединены с выходами информационных разрядов выходного регистра числа, входы информационных и контрольных разрядов которого соединены с соответствующими выходами блока памяти, входы информационных и контрольных разрядов которого соединены соответственно с выходами входного регистра числа и с выходами блока кодирования, входы которого соединены с выходами входного регистра числа, входы которого являются информационными входамяти соединены с информационными выходами регистра адреса, входы которого являются адресными входами устройства, о тл и ч а ю щ е е с я тем, что. с целью повышения надежности устройства. в него введены первый и второй блоки контроля, регистр состояния, мультиплексор, выходы которого являются информационными выходами устройства, выходы информационных и контрольных разрядов входного регистра числа соединены с соответствующими входами первого блока контроля, выход которого соединен с входом разряда контроля регистра состояния, входы контрольных разрядов кода которого соединены с выходами блока кодирования, выходы информационных и контрольных разрядов регистра адреса соединены с соответствующими входами второго блока контроля, выход которого соединен с входом разряда контроля адреса регистра состояния, выходы которого соединены с информационными входами первой группы мультиплексора, информационные входы второй группы которого соединены с

1649614

Составитель М.Лапушкин

Редактор Н,Каменская Техред М,Моргентал Корректор С.Черни

Заказ 1871 Тираж 358 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва. Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул,Гагарина, 101 выходами информационных разрядов выходного регистра числа, информацИонные входы третьей группы мультиплексора соединены с выходами блока коррекции. контрольные выходы блока декодирования соединены с соответствующими входами разрядов контроля числа по коду, входами регистра состояния. входы разрядов контроля по модулю три которого соединены с соответствующими выходами блока памяти, управляющие входы первого и второго блоков контроля объединены и являются входом блокировки контроля устройства, вход разрешения мультиплексора является вхо5 дом блокировки чтения устройства, первый, второй и третий управляющие входы мультиплексора являются входами чтения устройства соответственно корректируемого числа, некорректируемого числа и слова со10 стояния.