Устройство для контроля серий импульсов

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике. Целью изобретения является повышение достоверности контроля прохождения серий импульсов, достигаемое обеспечением возможности обнаружения ложных импульсов внутри контролируемых серий при одновременном расширении частотного диапазона. Устройство содержит многовходовой элемент ИЛИ 1, многовходовой элемент И 2, входную шину 3 устройства, блок формирователей 4 переднего фронта импульсов, блок формирователей 5 заднего фронта импульсов, первый элемент И 6. триггера 7, 8, второй элемент И 9, выходную шину 11, введение элемента ИЛИ 10 и новых связей внутри устройства позволяет осуществить контроль импульсных последовательностей на входе устройства. 2 ил. сл С

СОЮЗ СОПЕ1СКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

1649643 А1 (! У) (I I ) 90твйР9гЩ . ф» Пt. + Г (:, q (sI)s Н 03 К 5/19

ГОСУДАРСТ8Е ННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4498424/21 (22) 24.10.88 (46) 15.05.91. БюлМ18 (72) М.В.Камышенцев и С.А.Ефремов (53) 621,374.3 (088.8) (56) Авторское свидетельство СССР.

М 1064445, кл. Н 03 К 5/19, 1982.

Авторское. свидетельство СССР

N 1322446, кл. Н 03 К 5/19, 1985.

Авторское свидетельство СССР

1Ф 1338035, кл. Н 03 К 5/19. 1986, Букреев Н.Н. и др. Микроэлектронные схемы цифровых устройств, M.: Советское радио, 1973.

Авторское свидетельство СССР

М 1262709, кл. Н 03 К 5/19, 1985, (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СЕРИЙ

ИМПУЛЬСОВ

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля импульсных Ilo" следовательностей.

Целью изобретения является повышение достоверности контроля прохождения серий импульсов, которая достигается благодаря обеспечению возможности обнаружения ложных импульсов внутри контролируемых серий, причем контролируемые серии импульсов на входе устройства могут быть сдвинуты во времени друг относительно друга, иметь разную длительность, но при этом должно выполняться условие: импульсы должны взаимно перекрываться во времени.

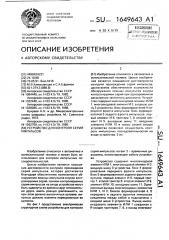

На фиг.1 представлена электрическая структурная схема устройства для контроля (57) Изобретение относится к автоматике и вычислительной технике. Целью изобретения является повышение достоверности контроля прохождения серий импульсов, достигаемое обеспечением возможности обнаружения ложных импульсов внутри контролируемых серий при одновременном расширении частотного диапазона. Устройство содержит многовходовой элемент ИЛИ

1, многовходовой элемент И 2, входную шину 3 устройства, блок формирователей 4 переднего фронта импульсов, блок формирователей 5 заднего фронта импульсов, первый элемент Й 6, триггера 7, 8, второй элемент И 9, выходную шину 11, введение элемента ИЛИ 10 и новых связей внутри устройства позволяет осуществить контроль импульсных последовательностей на входе устройства. 2 ил, серий импульсов; на фиг.2 — временные ди- д аграммы, иллюстирующие работу устройства.

Устройство содержит многовходовой элемент ИЛИ 1, многовходовой элемент И 2, йО входную шину 3 устройства, блок 4 форми- . 0 рователей переднего фронта импульсов,, фь блок 5 формирователей заднего фронта им- (Д пульсов, первый элемент И 6, первый триггер 7. второй триггер 8, второй элемент И 9. ф» элемент ИЛИ 10, выходную шину 11. Одно° веФ именные выходы многовходовых элементов

ИЛИ 1, И 2, блоков формирователей 4, 5 переднего и заднего фронтов импульсов соединены между собой и подключены к входной шине 3 устройства; Выход многовходового элемента ИЛИ 1 соединен с

R-входом триггеров 7, 8, а выход многовходонага элемента И 2 с С-входами триггеров

7, 8. Первый вход первого элемента И б соединен с выходом блока формирователей

5 заднего фронта импульсов, 3 вчорой вход соединен о инверсным выходом г1ервого 5 триггера 7. Первый вход второго элемента

И 9 соединен с прямым выходам второго триггера 8, а второй вход соединен с выходом блока формирователей 4 переднего фронта импульсов, ГГервый вход элеменrB 10

ИЛИ 10 соединен с выходом первого элемента И б, а выход второго элемента И 9 соединен с вторым входом элемента ИЛИ

10, выход которого подключен к выходной шине 11 устройства. 15

На фиг,2 приведены временные диаграммы: а,б,в — сигналов на входной шине 3;

f — сигflB 108 на Bf:fxo@8 Bfloмента ИЛИ 1; р,— .игналов IIB выходе блока формирователей

5; е — сигналов на выходе элемента И 2; ж — 20 си1 -1алов HB выходе блока фармиравателеи

4; з — сигналов на инверсном выходе триггера 7; и — сигналов на прямом выходе триггера 8; к — сигналов на выходе элемента И 6;

r — сигналов на выходе элемента И 9; м — 25 сигналов на входной шине 11. устройства работает следующим образом.

Контролируемые серии импульсов, поступающие на входные шины 3, могут быть 30 сдвинуты во времени друг относительно друга име еf f разную длител ьнаст на при э1.ом должно выполняться следуюгцее условие; импульсы должны взаимно перекрываться во в åìåíè. При этом 35 рассма- ривается ряд возможных ситуаций, при контроле серий импульсов: — нормальная последовательность импульсов в серии, т,е. Наличие импульсов на всех входных шинах 3 устройства и совпадения их в течение 40 времени, достаточного для надежной работы элементов; — отсутствие импульсов на одной или нескольких входных шинах 3 устрайстВз; — возникновение лажного импульса 45 внутри контролируемой серии до момента наличия импульсов на всех входных шинах

3; возникновение ложного импульса внутри контролируемой серии после момен- 50 та наличия импульсов на всех входных шинах 3, но до окончания серии; — возникновение на одной или нескольких- входных шинах 3 сигнала постоянного единичного ураВня. 55

Вариант возникновения одиночного ложного импульса нз ОднОЙ из Входных шин

3 ие рассматривается, так как данная ситуация является частным случаем пропадания импульсов.

Перед началом работы триггеры 7 и 8 устанавливаются в исходное состояние путем подачи сигнала на К-входы триггеров (не показано). При этом на инверсном выходе триггера 7 присутствует сигнал единичного уровня, 1в на прямом выходе триггера 8 — сигнал нулевого уровня.

Рассматривается вариант нормальной последовательности импульсов в серии (интервал времени tG- tl), Па переднему фронту первого импульса, поступившего на входные шины 3 (фиг.2б), на выходе элемента

ИЛИ 1 появляется сигнал единичного уровня (фиг,2г), передним фронтом которого подтверждается состояние триггера 7 перед началом контроля.

По переднему фронту каждого поступающего на входные шины 3 импульса (фиг.2а,б,в) с выхода блока формирователей

4 переднего фронта импульсов короткий импульс поступает на вход элемента И 9 (фиг.2ж ). В виду того, что на втором входе элемента И 9 присутствует сигнал нулевого уровня, снимаемый с выхода триггера 8 (фиг.2и), HB выходе элемента И 9 находится сигнал нулевого уровня (фиг.2л). При наличии импульсов на всех входных шинах 3 на выходе элемента И 2 формируется сигнал единичного уровня (фиг.2е), по переднему фронту которого запускается триггер 7 и на сго инверсном выходе появляется сигнал нулевого уровня (фиг,2з).

Этот сигнал поступает на вход элемента

И 6 и запрещает прохождение через элемент И 6 сигналов единичного уровня, По

oKoH÷Bíèè совг1аде 1ия Всех сигналов, присутствующих на входных шинах 3, нз выходе элемента И 2 появляется сигнал нулевого уровня (фиг.2е}., па которому взводится триггер 8, На выходе триггера 8 появляется сигнал единичного уровня (фиг.2и), который поступает на вход элемента И 9, разрешая прохождение чсрез элемент И 9 сигналов единичного уровня, По каждому заданному фронту импульсов, поступающих на входные шины 3 (фиг.2 а,б,в), с выхода блока формирователей 5 заднего фронта импульсов .снимается короткий импульс (фиг.2д), поступающий на вход элемента И б, но за счет присутствия сигнала нулевого уровня на втором входе элемента И 6, на его выходе присутствует сигнал нулевого уровня, По концу серии импульсов на выходе элемента

ИЛИ 1 появляется сигнал нулевого уровня (фиг,2г), по заднему фронту I..оторого сбрасывается триггер 8 в исходное состояние (фиг.2м), и устройство готово к контролю очередной серии импульсов.

Если в очередной серии импульсов отсутствует хотя бы один импульс на входных

1649643

20 шинах 3 (интервал времени t< — t2) (фиг.2б), то по переднему фронту импульса с выходы элемента ИЛИ 1 (фиг,2г) триггер 7 устанавливается в исходное состояние и на его инверсном выходе присутствует сигнал единичного уровня (фиг.2з). На выходе элемента И 2 все время присутствует сигнал нулевого уровня (фиг.2е) и триггер 7 останется в исходном состоянии, т.е. на его инверсном выходе присутствует сигнал единичного уровня (фиг,2з). По заднему фронту каждого импульса из контролируемой серии с выхода блока формирователей

5 заднего фронта импульсов формируется короткий единичный импульс (фиг.2д), который через элемент И 6 (фиг,2к) и ИЛИ 10 поступает на выходную шину 11 устройства (фиг.2м) сигнализируя о сбойной ситуации.

В случае возникновения ложного импульса внутри контролируемой серии импульсов до момента наличия импульсов на всех входных шинах 3 (интервал времени

t2 — 1з) (фиг.2в) работа устройства происходит аналогично рассмотренной выше ситуации попадания импульса, на выходе элемента И 2 присутствует сигнал нулевого уровня (фиг,2е).

С выхода триггера 7 на вход элемента И

6 поступает сигнал единичного уровня (фиг,2з), который разрешает прохождение через элемент И б сигналов единичного уровня. По заднему фронту ложного импульса (фиг.2в) на выходе блока формирователей

5 заднего фронта импульсов образуется единичный импульс (фиг.2д), который через элементы И 6, ИЛИ 10 поступает на выходную шину 11 (фиг.2м) устройства, сигнализируя о сбойной ситуации, В случае возникновения ложного импульса внутри контролируемой серии импульсов после момента наличия импульсов на всех входных шинах 3, но до окончания серии импульсов (интервал времени тз — t4), работа устройства происходит следующим образом. По заднему фронту сигнала, снимаемого с выхода элемента И 2 (фиг.2е), взводится триггер 8, с выхода которого сигнал единичного уровня (фиг.2и) поступает на вход элемента И 9. С выхода блока формирователей 4 переднего фрон. а импульсов, по переднему фронту ложного импульса (фиг.2б) формируется короткий единичный импульс (фиг.2ж), который через элементы И 9 (фиг.2л), ИЛИ 10 поступает на выходную шину 11 устройства (фиг.2м), сигнализируя о сбойной ситуации.

В случае возникновения на одной или нескольких входных шинах 3 сигнала постоянного единичного уровня (интервал време25

55 ни t4 — t5) (фиг.2б) работа устройства проис-ходит следующим образом. После контроля очередной серии импульсов, в связи с тем, что на одной из входных шин 3 присутствует сигнал единично о уровня (фиг.2б), на выходе элемента ИЛИ 1 также присутствует сигнал единичного уровня (фиг.2г), поэтому триггер 8 не возвратится в исходное состояние и на его прямом выходе присутствует сигнал единичного уровня (фиг.2и). который поступает на вход элемента И 9. По переднему фронту первого же импульса из последующей контролируемой серии импульсов(фиг,2а), на выходе блока формирователей 4 переднего фронта импульсов формируется короткий единичный импульс (фиг.2ж), который через элементы И 9, ИЛИ

10 поступает на выходную шину устройства (фиг.2м), сигнализируя о сбойной ситуации.

Формула изобретения

Устройство для контроля серий импульсов, содержащее многовходовый элемент

ИЛИ, многовходовый элемент И, одноименные входы которых подключены к соответствующей входной шине устройства, блок формирователей переднего фронта импульсов, блок формирователеи заднего фронта импульсов выход которато подключен к первому входу первого двухвходового эпел1ента

И. первый триггер, в арой три. гер, прямой выход которого подключен к первому входу втОрого двухвходового элемента И, о т л ич а ю щ е е с я тем, что, с цепью расширечия функциональных возл1ожностей устройства за счет повышения достоверности контроля прохождения серий импульсов при одновременном расширении час1отного диапазона контролируел1ых серий ил1пупьсов в него введен элемент ИЛИ, причем одноименные входы блока формирователей переднего фронта импульсов и олока формирова1елей - заднегo франта импульсов псдключены к соответствующей входной шине устройства, выход многовходового элемента ИЛИ соединен с Й-входом первого и второго триггеров, С-входы которых соединены с выходом многовходoBofo элемента И, причем инверсный выход первого триггера соединен со вторым входом первого двухвходового элемента И, выход которого соединен с первым входом двухвходового элемента ИЛИ, а выход блока формирователей переднего фронта импульсов соединен со вторым входом второго двухвходового элемента И, выход которого соединен со вторым входом двухвходового элемента ИЛИ, выход которого подключен к выходной шине устройства.

1649643

6mf

Ри.7

1р

Составитель А.Кочеткова

Редактор B,Трубченко Техред М.Моргентал Корректор М.Пожо

Производственно-издательский комбинат "Патент". г. Ужгород, ул.Гагарина, 101

Заказ 1872 Тираж 478 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж 35, Раушская наб., 4/5