Делитель частоты с программируемым коэффициентом деления

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматического управления и синтеза частот. Цель изобретения - повышение быстродействия и надежное и работы. Делитель частоты содержит блок 1 управления , блок 2 опознавания, счетчик 3 старших разрядов, первый и второй блоки 4 и 5 записи кода, выходную шину 6, счетчик 7 младших разрядов, входную шину 8, кодовые шины 9, 10 и 11 старших разрядов, преобразователь 12двоичного кода в код Грея, кодовые шины 13и 14 младших разрядов. 2 ил.

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5т)5 Н 03 К 23/00

ГОСУДАРСТВЕ ННЫ Й КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4348595/21 (22) 22.12.87 (46) 15.05.91. Бюл. М 18 (72) В.Н,Паулаускас и А,Р,Гутаускас (53) 621.374.4 (088.8) (56) Авторское свидетельство СССР

М 1182669, кл. Н 03 К 23/00, 1984.

Авторское свидетельство СССР

hh 666688009944, кл. Н 03 К 23/66, 1976. (54) ДЕЛИТЕЛЬ ЧАСТОТЫ С ПРОГРАММИРУЕМЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматического управления и синтеза частот.

Цель изобретения — повышение быстродействия и надежности работы.

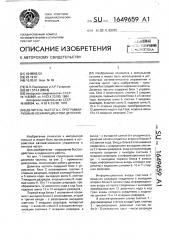

На фиг. 1 показана структурная схема делителя частоты; на фиг. 2 — временные диаграммы, поясняющие работу делителя, Делитель частоты содержит блок 1 управления, блок 2 опознавания, счетчик 3 старших разрядов, первый и второй блоки 4 и 5 записи кода, выходную шину 6, счетчик

7 младших разрядов, входную шину 8, кодовые шины 9, 10 и 11 старших разрядов, преобразователь 12 двоичного кода в код Грея, кодовые шины 13 и 14 младших разрядов, Первый вход блока 1 управления соединен с выходом блока 2 опознавания, второй и третий входы — с разрядными выходами счетчика 7 младших разрядов, четвертый вход — с входной шиной 8 и входом еинхрониэации счетчика 7 младших разрядов, а

5U» 1649659 А1 (57) Изобретение относится к импульсной технике и может быть использовано в устройствах автоматического управления и синтеза частот. Цель изобретения —.повышение быстродействия и надежности работы.

Делитель частоты содержит блок 1 управления, блок 2 опознавания, счетчик 3 старших разрядов, первый и второй блоки 4 и 5 записи кода, выходную шину б, счетчик 7 младших разрядов, входную шину д, кодовые шины 9, 10 и 11 старших разрядов, преобразователь

12 двоичного кода в код Грея, кодовые шины

13 и 14 младших разрядов. 2 ил, выход — с-выходной шиной б и входами разрешения записи первого и второго блоков 4 и 5 записи кода. Входы блока 2 опознавания соединены с разрядными выходами счетчика 3 старших разрядов, вход синхронизации которого соединен с выходом счетчика 7 младших разрядов, а информационные входы — с выходами первого блока 4 записи кода, информационные входы которого соединены с кодовыми шинами 9, 10 и 11 старших разрядов, Информационные входы счетчика 7 младших разрядов соединены с выходами второго блока 5 записи кода, информационные входы которого соединены с выходами йреобразователя 12 двоичного кода s код

Грея, входы которого соединены с кодовыми шинами 13 и 14 младших разрядов, В рассматриваемом случае счетчик 7— двухразрядный счетчик в коде Грея, счетчик

3 — трехразрядный двоичный счетчик, либо (n - 2)-разрядный. где n — число разрядов

1649659 делителя. Счетчики 3 и 7 работают в режиме вычитания.

Делитель частоты работает следующим образом.

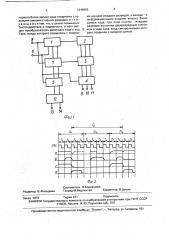

На фиг. 2 приведены временные диаграммы входной последовательности CKl (Твх), выходных сигналов а и Ь разрядов счетчика 7 младших разрядов, выходного сигнала с блока 2 опознавания (схема И на (и - 2)-входов), выходного сигнала d блока 1 управления, причем для коэффициента деления, равного семи, достаточно рассмотреть три четырехтактовых цикла Тс1, Тс2, Тсз работы делителя. При Кдел = 7 в счетчик 7 вводится число три, а в счетчик 3 — число один.

Период деления Тр состоит из семи тактов. В первом цикле каждого периода деления два такта T>, Tz относятся к предыдущему периоду деления, а в последпоследовательностях а и Ь содержится лог

"1") и поэтому на диаграмме появляется незаполненная графа. Счетчик 7 работает в цикле 10 11 01 00 10 11... Если коэффициент деления был бы шесть, то цикл T z начинался с такта Тз и две первые графы были бы не заполнены при принятой форме графического построения диаграммы.

Триггеры счетчиков 3 и 7.имеют преимущество по входам установки 0 и 1 относительно входа синхронизации. Запись коэффициента деления, т,е. начальные со.стояния триггеров счетчиков 3 и 7 задаются однозначно ко входам установки 0 и 1, Коэффициент деления вводится в счетчики 3 и

7 в прямом двоичном коде. Наименьший коэффициент деления равен 3, а наибольший (2" — 1).

Быстродействие делителя обеспечивается тем, что импульсы логических состояний вырабатываются с задержкой, равной одному переходу логического элемента из одного состояния в другое. Импульсы, воздействующие на блок 1 управления, вырабатываются в одном полутакте, а во втором полутакте вырабатывается импульс управления. который в первом полутакте следующего такта уже выполняет логическую операцию. Счетчик, работающий в коде . Грея, за один такт изменяет состояние только одного триггера, Поэтому задержка импульса в двух разрядах счетчика в коде Грея для всех четырех состояний одинакова. Другим важным фактором является надежность работы делителя, которая обеспечивается селективностью работы узлов счетчика младших разрядов делителя и блока управления в течение периода деления. Это достигается текстированием и разбиением входной последовательности на циклы.

Формула изобретения

Делитель частоты с программируемым коэффициентом деления, содержащий блок управления, первый вход которого соединен с выходом блока опознавания, входы которого соединены с разрядными выходами счетчика старших разрядов, информационные входы которого соединены с выходами первого блока записи кода, вход управления которого соединен с выходом блока управления, входом разрешения записи второго блока записи кода и выходной шиной, счетчик младших разрядов, информационные входы которого соединены с выходами второго блока записи, выход — со входом синхронизации счетчика старших разрядов, а разрядные выходы — со вторым и третьим входами блока управления, четвертый вход которого соединен с входной шиной, причем информационные входы

20 нем цикле периода деления два последних такта f3, Та относятся к следующему периоду деления. Два такта Тз и Т4 первого цикла

Тд предназначены для установки нового коэффициента деления. Количество тактов второго цикла Тд равно остатку от деления коэффициента деления делителя на четыре, При остатке, равном нулю, второй Тд начинается с первого такта Т1, при остатке деления, равном трем, цикл T

30 второго такта Tz, при остатке деления, равном двум — с третьего такта Тз, при остатке деления, равном единице — с четвертого такта Т4.. Такой режим обеспечивается реверсивной работой счетчика в коде Грея.

Продолжительность каждого следующего цикла, кроме последнего, равна четырем тактам.

Счетчик 7 работает в коде Грея в режиме вычитания. Такт Т1 соответствует состо35

40 янию счетчика три, такт Tz — состоянию два, такт Тз — состоянию один, такт Т4 — состоянию нуль. Во втором такте Tz последнего цикла периода деления Т> импульсы всех ют значения лог "1". В этом такте срабатывает блок 1 управления и, начиная со следующего такта Тз, выдает на выходе блока 1 импульс длительностью полтора такта (и оследо вател ь ность б). Посл едовател ьность d управляет записью нового коэффициента деления в счетчики 3, 7, В течение этого времени в счетчиках устанавливается новый коэффициент деления. В нашем случае в счетчике 7 устанавливается код три, 7mod4 = 3 (на диаграмме процесс установления коэффициента показан пунктирными

55 линиями). Так как следующее состояние счетчика 7 является два (11 в коде Грея), то второй цикл Та начинается с такта Т2 (в трех последовательностей а, Ь, с принима- 45

1б49б59

15 14 сРИ2. 7

Prrz. Е

Составитель О.Бодряшова

Редактор В,Фельдман Техред М.Моргентал - Корректор О.Ципле

Заказ 1873 . Тираж 471 ПодписнОе

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент". г. Ужгород, ул.Гагарина, 101 первого блока записи кода соединены с кодовыми шинами старших разрядов, о т л ич а ю шийся тем, что, с целью повышения быстродействия и надежности, в него введен преобразователь двоичного кода в код

Грея, входы которого соединены с кодовыми шинами младших разрядов, а выходы — с информацйонными входами второго блока записи кода, при этом счетчик младших разрядов выполнен двухраэрядным счетчи5 ком в коде Грея, вход синхронизации которого соединен с входной шиной.