Устройство для контроля умножения двоичных чисел по модулю три

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в арифметических узлах. Цель изобретения сокращение аппаратурных затрат устройства . Устройство содержит три узла 1. 3, 4 свертки по модулю три, блок 2 свертки по модулю три. узел 5 сложения по модулю три. блок 6 сравнения, узел 7 умножения по модулю три, группу 8 элементов И, сумматор 9, группу 20 узлов умножения по модулю три. Узлы 4, 10 и сумматор 9 формируют контрольный код отбрасываемых разрядов результата . Узел 5 формирует код 21 разрядного результата умножения, который сравнивается блоком 6 сравнения с контрольным кодом, сформированным узлом 3 из результатаумножения, поступающею на вход 13 результата устройства. Выход блока 6 подключен к выходу 14 неисправности устройства . 7 ил.

COIO3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 ч

Ф

7 ф

s и»

С

»

»» (21) 4433718/24 (22) 30.05.88 (46) 23.05.91. Бюл. М19 (71) Одесский политехнический институт (72) А.В.Дрозд, Е.Л.Полин, А.С.Попов, О.-Н.Паулин и Ю.В.Дрозд (53) 681.3 (088.8) (56) Авторское свидетельство СССР

N. 595737, кл. G 06 F 11/08, 1975.

Авторское свидетельство СССР

М 1177814, кл. G 06 F 11/08, 1985, (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УМНОЖЕНИЯ ДВОИЧНЫХ ЧИСЕЛ ПО МОДУЛЮ

ТРИ (57) Изобретение относится к вычислительной технике и может быть использовано в арифметических узлах. Цель иэобретения—

„„ Ж„„1651288 Al сокращение аппаратурных затрат устройства. Устройство содержит три узла 1. 3, 4 свертки по модулю три, блок 2 свертки по модулю три, узел 5 сложения по модулю три, блок б сравнения, узел 7 умножения по модулю три, группу 8 элементов И, сумматор 9, группу 20 узлов умножения по модулю три.

Узлы 4, 10 и сумматор 9 формируют контрольный код отбрасываемых разрядов результата. Узел 5 формирует код 21 разрядного результата умножения, который сравнивается блоком б сравнения с контрольным кодом, сформированным узлом 3 из результатаумножения, поступающе о на вход 13 результата устройства. Выход блока б подключен к выходу 14 неисправности устройства. 7 ил. В

1651288

Изобретение относится к вычислительной технике и может быть использовано в арифметических узлах.

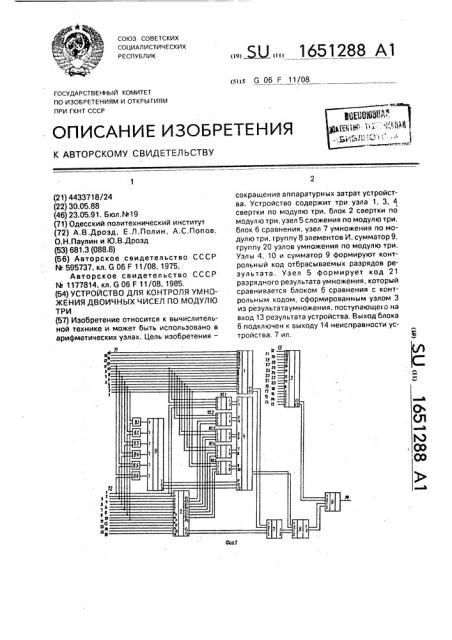

Цель изобретения — сокращение аппаратурных затрат устройства, На фиг.1 приведена функциональная схема устройства; на фиг,2 — функциональная схема блока свертки по модулю два на шестнадцать разрядов; на фиг.3 — матрица коньюнкций К=11 младших ряэрядов полного произведения; на фиг.4 и 5 — функциональные схемы узлов умножения группы и узла сложения по модулю три; на фиг.6 и 7 — функциональные схемы сумматора и блока сравнения.

В матрице коньюнкций, приведенной на фиг,З, номера столбцов и строк матрицы являются номерами разрядов множимого и множителя соответственно, а на пересечении этих столбцов и строк символом Х обозначены соответствующие коньюнкции.

Коньюнкции выделены в ряд фрагментов матрицы шириной в два элемента соответственно а,b,c,d и е. Контрольные коды фрагментов а,d ñ,d å формируются соответствующими узлами умножения по модул ю три груп и ы.

Устройство (фиг,1) содер>кит первый узел 1 свертки по модулю три, блок 2 свертки по модулю три, второй 3 и третий 4 узлы свертки по модулю три, узел 5 сложения по модулю три, блок 6 сравнения, узел 7 умножения по модулю три, группу 8 элементов И, сумматор 9, группу 10 узлов умножения по модулю три, вход 11 мно>кимого устройства, вход 12 множителя устройства, вход 13 результата устройства и выход 14 неисправности устройства.

Устройство работает следующим образом.

Контрольные коды фрагментов а,b,с,d,е с выходов узлов умножения по модулю три группы 10 и код фрагмента f (коньюнкции, не входящие в фрагменты а,Ь,с,d,е) с выхода сумматора 9 поступает на вход третьего узла 4 свертки по модулю три, который формирует контрольный код кон ьюнкций треугольной матрицы. На эту величинуотличается контрольный код полного произведенияя от контрольного кода 21-разрядного результата умножения. С выхода узла 5 сложения по модулю три снимается контрольный код 21-разрядного результата умножения, Зтот код сравнивается на блоке

6 сравнения с кодом, сформированным третьим узлом 3 свертки по модулю три из кода. поступающего на вход 13 результата устройства (множимое и множитель поступают на входы 11 и 12 устройства соответственно), С выхода блока 6 сравнения сигнал несравнения поступает на вход 14 неисправности устройства.

Формула изобретения

Устройство для контроля умножения двоичных чисел по модулю три, содержащее

10 три узла свертки по модулю три, узел сложения по модулю три, узел умножения по модулю три, блок сравнения и блок свертки по модулю три, причем вход множимого устройства соединен с входом первого узла свертки по модулю три, выход которого соединен с входом первого операнда узла умножения по модулю три, вход множителя устройства соединен с входом блока свертки по модулю три, выход результата свертки всех разрядов которого соединен с входом второго операнда узла умножения по модулю три, выход которого соединен с первым информационным входом узла сложения по модул ю три, выход которого соединен с пе рвым информационным входом блока сравнения, вход результата устройства соединен с входом второго узла свертки по модулю три, выход которого соединен с вторым информационным входом блока сравнения, выход которого является выходом неисправности устройства, о т л и ч а ю щ ее с я тем, что, с целью сокращения аппаратурных затрат устройства, оно содержит . К+1 группу из

2 элементов И (К вЂ” количество отбрасываемых разрядов результата, неК вЂ” 1 четное), сумматор, группу иэ 2 узлов умножения по модулю три, причем первый вход 1-го элемента И группы соединен с (2i - 1)-разрядом входа множимого устройстК+1 ва(1< i <

), второй вход i-го элемента И группы соединен с (К вЂ” 2i + 2)-м разрядом входа множителя устройства, выходы элементов И группы соединены с соответствующими информационными входами сумматора, выход результата которого соединен с соответствующим входом третьего узла свертки по модулю три, первый и второй разряды входа первого операнда j-го узла умножения по модулю три группы сое15

50 динены с (К - 2))-м и (К -2) + 1)-м разрядами входа множимого устройства соответствен55 К вЂ” 1 но {1 — j 2 ), первый и BTOpGA разряды входа второго операнда первого узла умножения по модулю три группы подключены к первому и второму разрядам входа множителя устройства соответственно, вы1651288 ходы результата свертки 2m младших разрядов блока свертки по модулю три соединены с входами второго операнда гп-х узлов умноже н и я по модул ю т р и

К вЂ” 1 группы (2 а гп < ).

Af

AZ

61

BZ

cf

С2

Э1

1651288

Фиг. 7

Составитель B. Гречнев

Техред M.Ìopråíòàë Корректор И. Муска, Редактор B. Данко

Производственно-издательский комбинат "Патент", г, Ужгород, ул,Гагарина, 101

Заказ 1607 Тираж 422 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/6