Устройство для вычитания

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах распознавания , образов поиска информации и в системах принятия решений в нечетких условиях. Целью изобретения является расширение функциональных возможностей устройства за счет осуществления операций конъюнкции, дизъюнкции, штрих Чеффера, стрелки Пирса и вычисления разности нечетких переменных . Цель достигается введением в устройство, содержащее первый и второй регистры сдвига, группу элементов И, группу элементов ИЛИ и элемент И, второго элемента И, двух элементов ЗАПРЕТ, двух элементов ИЛИ, двух коммутаторов и новых связей . Это дает возможность реализовать на устройстве кроме операций вычисления модуля разности, степени нечетного равенства и отрицания,также вышеуказанные операции в нечеткой логике над операндами, представленными в унитарном коде. 2 ил. (/

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 G 06 F 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

М АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4704583/24 (22) 14.06.89 (46) 07.06.91. Бна. У 21 (71) Таг.анрогский радиотехнический институт им. В.Д. Калмыкова (72) А.Н. Мелихов, В.П. Карелин и В.Н. Решетняк (53) 681.325. 5 (088.8) (56) Авторское свидетельство СССР

8 1376079, кл. G 06 F 7/50, 1987.

Авторское свидетельство СССР

È1487028 ° кл G F 7/50> 1987 ° (54) УСТРОЙСТВО ДЛЯ ВЫЧИТАНИЯ (57) Изобретение относится к вычисли тельной технике и может быть использовано в устройствах распознавания, образов, поиска информации и в системах принятия решений в нечетких условиях. Целью изобретения является

Изобретение относится к вычислительной технике и может быть использовано в устройствах распознавания образцов, поиска информации и в системах принятия решений в нечетких условиях.

Цель изобретения — расширение функциональных возможностей устройства за счет осуществления операций коньюнкции, дизъюнкции, штрих Шеффера, стрелки Пирса и вычисления разности нечетких переменных.

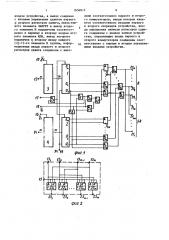

На фиг.1 приведена функциональная схема устройства для вычитания; на фиг.2 — функциональная схема коммутатора.

Устройство для вычитания содержит регистры 1 и 2 сдвига, коммутаторы

ÄÄSUÄÄ 1654813 Д 1 расширение функциональных возможностей устройства за счет осуществления операций конъюнкции, дизъюнкции, штрих Шеффера, стрелки Пирса и вычисления разности нечетких переменных. Цель достигается введением в устройство, содержащее первый и второй регистры сдвига, группу элементов И, группу элементов ИЛИ и элемент И, второго элемента И, двух элементов ЗАПРЕТ, двух элементов

ИЛИ, двух коммутаторов и новых связей. Это дает возможность реализовать на устройстве кроме операций вычисления модуля разности, степени нечетного равенства и отрицания, также вышеуказанные операции в нечеткой логике над операндами, представленными в унитарном коде. 2 ил.

3 и 4, группу 5 элементов И, группу

6 элементов ИЛИ, элемент ЗАПРЕТ 7, элемент И 8, элемент ИЛИ 9 ° элемент

ЗАПРЕТ 10, элемент И 11, элемент

ИЛИ 12, входы 13 и 14 операндов, управляющие входы 15 и 16, тактовый вход 17, вход 18 управления режимом работы устройства, вход 19 записи, первую 20 и вторую 21 группы выходов.

Каждый коммутатор 3 и 4 содержит элементы И-ИЛИ 22 с выходами 23.

Устройство предназначено для вычисления модуля разности R, где R =

= (А — В(, степени С нечетного равенства (эквивалентности) двух чисел

А и В, где G = 1-R = 1 — А — В, а также вычисления результата операций: разностьу конъюнкция, штрих Шеффера, 1654813 стрелка Пирса, дизъюнкция, отрицание в нечеткой логике с ограниченными операциями, где разность N нечетких переменных А и В вычисляется по фор муле N = max(0, А-В), результат К вычисляется по формуле К = max (О, А" (1-В)), штрих Шеффера Б вычисляется по формуле S = 1-К, результат

Р операции стрелка Пирса вычисляется по Формуле Р max (О, (1-А)-В), результат D дизъюнкции — по Формуле

D = 1 — Р, отрицание А = 1-А.

Устройство работает следующим образом. 15

Значения переменных А и В в уни-. тарном коде поступают на информационные входы 13 и 14 соответственно первого и второго коммутаторов, а затем по сигналу записи передаются из коммутаторов в регистры сдвига либо без изменения, либо в виде отрицания (в зависимости от вида операции) .;После этого осуществляется одновременный сдвиг содержимого обоих регистров в сторону младших разрядов. Сигналом окончания сдвига в регистрах и формирования результата операции на выходах устройства является появление единицы в младшем разряде любого из регистров. При этом

30 в режиме выполнения операции К =

= j А — В результат операции подается на выходы устройства либо из первого регистра, либо из второго, а в режиме получения ограниченной разнос- 35 ти N = max {О, А — В) результат операции подается на выходы устройства тсатько из первого регистра. Признаком управления режимом работы устройства является сигнал У1, а сигна- 40 лы У, У> управляют выдачей информации соответственно через первый и второй коммутаторы либо без изменения, либо в инверсном виде (в виде отрицания), Так,при вычислении результатов операций R = j A — В1и С = 1 — R управляющие сигналы следующие: Y =1, Y2 = 1; У = 1. По сигналу с входа 19 устройства значения А и В с выходов ком-50 мутаторов 3 и 4 записываются соответственно в регистры 1 и 2. После этого на тактовый вход 1 7 устройства поступают ,:тактовые импульсы, которые через откры тый элемент ЗАПРЕТ 7 проходят на входы управления сдвигом регистров 1 и 2.

Содержимое регистров синхронно сдвигаетея в сторону младших разрядов до тех пор, пока в младшем разряде любого из регистров не появится единица. Если А >В, то при сдвиге в регистрах унитарных кодов этих чисел единица раньше появится в младшем разряде второго регистра, а в регист ре 1 формируется унитарный код чис.ла А-В . При этом элемент ЗАПРЕТ 7 запирается единичным сигналом с выхода элемента ИЛИ 9. Элемент И 8 за перт нулевым сигналом с выхода младmего разряда регистра 1. Единичный сигнал с выхода младшего разряда регистра 2 проходит через открытый сигналом Y.1 = 1 элемент И 11 и, проходя через элемент ИЛИ 12, открывает (2j1) -е элементы И 5, где j = 1,...,ш, и далее через элементы ИЛИ 6 на выходе 20 устройства. На этих выходах образуется унитарный код модуля разности R =(А-Bl . Поскольку А,ВС(0,1, то на симметрично расположенных выходах 21 — 21,„ образуется унитарный код величины С = 1-R т.е. код степени нечетного равенства.

Если A(В, то при сдвиге в регистрах 1 и 2 единица появляется раньше в младшем разряде регистра 1.

Сдвиг в регистрах прекращается, так как на выходе элемента ИЛИ 9 появляется единичный сигнал, который закрывает элемент ЗАПРЕТ 7. Единичный сигнал с выхода младшего разряда регистра 1 проходит через открытый сигналом Y = 1 элемент И 8 и, поступив на входы 21-х элементов И 5, открывает их для прохождения содержимого регистра 2, где сформирован унитарный код числа R = В-А 1А-В, через элементы ИЛИ б на выходы 20 и 21 уст,,ройства, обусловив формирование на . этих выходах унитарных кодов соответственно чисел R = 1А-В I и С = 1-R.

Если А=В, то при сдвиге в регистрах 1 и 2 единица появляется одновременно в младших разрядах обоих регистров. При этом единичный сигнал с выхода элемента И 8 открывает все элементы И 5, а единичный сигнал с выхода элемента И 11, проходя через элемент ИЛИ 12, открывает все элемен" ты И 5(°, В результате содержимое

21-() обоих регистров, т. е. разряды унитарных кодов числа О, поступают на вхо-! ды соответсвующнх элементов ИЛИ 5. и затем на выходы 20 и 21 .устройства, обусловив на этих выходах Формирование унитарных кодов соответственно

1654813 чисел К= А-В =О иС=1 — R= — 1.

Для вычисления отрицания А = 1-А в регистр 1 следует загрузить вели5 чину A а в регистр 2 — величину

В = 0 (т.е. установить в единицу младший разряд регистра 2). Работа устройства при этом аналогична описанному случаю формирования значений

R = А-B) и С = 1-2, когда. А ) В.

Унитарный код значения А = 1-А формируется на выходах за один такт.

В режиме вычисления результата операции "Ограниченная разность"

И max (О, А-B) управляющие сигналы следующие: 7 = 0; Y = 1; 73

Сигнал 71 = 0 закрывает элементы

И 8 и 11 и открывает элемент ЗАПРЕТ

10. По сигналу записи с входа 19 уни- 20 тарные коды чисел А и В с выходов коммутаторов 3 и 4 записываются соответственно в регистры 1 и 2. Тактовые импульсы, проходя через открытый элемент ЗАПРЕТ 7 с входа 17 уст- 25 ройства на входы сдвига регистров 1 и 2, обуславливают синхронный сдвиг содержимого этих регистров. Признаком окончания сдвига и формирования в регистре 1 унитарного кода числа 30

N появляется единица в младшем разряде любого из регистров. При этом единичный сигнал с выхода элемента ИЛИ

9 закрывает элемент ЗАПРЕТ 7 и,поступая через открытый сигналом Yg = О элемент

ЗАПРЕТ 10 и через элемент ИЛИ 11 на

35 входы всех элементов И 5(,, открывает их для прохождения содержимого разрядов регистра 1 через элементы ИЛИ 8 на выходы 20 устройства.

Вычисление. результата операции стрелка Пирса Р =- max (О, А-В) осуществляется в устройстве аналогично вычислению операции ограниченная разность N. Различие состоит лишь в 45 том, что в регистр 1 подается унитарный код не числа А> как при вычислении N, а код числа А = 1 — А, который формируется на выходе коммутатора

3 под действием управляющего сигнала

Y = О. Таким образом, набор управляющих сигналов при вьгшслении результа.тов операции P и операции D = i-Р:

Y = О; Y = О; Y > -- 1. Унитарный код числа P формируется на выходах

20, а числа D = 1 — Р— на выходах

21 устройства.

При вычислении результатов операций конъюнкции К = max (О, А-В) и штрих Иеффера S = 1-К набор управляющих сигналов следующий: У О;

Y. = 1; Y„= О. В этом случае в ре2. гистр 1 записывается унитарный код числа А, а в регистр 2 — код числа

В = 1-В. Устройство работает как при вычислении операции N, Результат операции конъюнкции K формируется на выходах 20 а операции штрих Шеффера $ = 1-К вЂ” на выходах i устройства.

Фор мула и з обр ет ения

Устройство для вычитания, содержащее первый и второй регистры сдвига, группу из 2m элементов И, где

m — разрядность операндов, группу из

m элементов ИЛИ, первый элемент И, причем выходы j-ro разряда первого и второго регистров сдвига„где

1,...,m соединены с первыми входами соответственно (23-1)-го и

2j-ro элементов И группы, выходы которых соединены соответс-венно с первым и вторым входами j-го элемента

ИЛИ -.ðóïïû, выход которого является

j-м выходом первой группы выходов устройства и (m-j+1)-м выходом второй группы выходов устройства, о тл и ч а ю .щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет осуществления операций конъюнкции, дизъюнкцни, штрих Шеффера, стрелки

Пирса и вычисления разности нечетких переменных„ оно дополнительно содержит второй элемент И, два элемента

ЗАПРЕТ, два элемента ИЛИ и два коммутатора, причем выход первого элемента И подключен к второму входу каждого 2j-ãî элемента И группы, первый вход первого элемента И соединен с выходом младшего разряда первого регистра сдвига и с первым входом первого элемента ИЛИ, второй вход первого элемента И соединен с входом управления режимом работы устройства, с первым входом второго элемента И и ичверсным . входом первого элемента

ЗАПРЕТ, выход младшего разряда второго регистра сдвига подключен к вторым входам второго элемента И и перво"o элемента ИЛИ, выход первого элемента ИЛИ подключен к прямому входу первого и к инверсному входу второго элементов ЗАПРЕТ, прямой вход второго элемента ЗАПРЕТ является тактовым

1654813

10 входом устройства, а выход соединен с входами управления сдвигом первого и второго регистров сдвига, выход nepsdro элемента ЗАПРЕТ и выход второго элемента И подключены соответст- венно к первому и второму входам второго элемента ИЛИ, выход которого подключен к второму входу каждого (2j-1)-ro элемента И группы, инфор мационные входы первого и второго регистров сдвига соединены с выходами соответственно первого и второго коммутаторов, входы которых являются соответственно входами первого и второго операндов устройства, Вхо» ды управления записью регистров сдвига соединены с входом записи .устройства, управляющие входы первого и второго коммутаторов соединены соответственно с первым и вторым управляющими входами устройства.