Устройство управления памятью

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к устройствам арбитража и управления памятью, и предназначено для использования в микрокомпьютерах, имеющих совмещенную память программ и изображения. Целью изобретения является повышение быстродействия устройства. Устройство содержит контроллер 1 монитора, мультиплексор 2 управляющих сигналов, блок 3 синхронизации, триггер 4 обращения, первый 5 и второй 6 мультиплексоры адреса. Устройство позволяет повысить быстродействие микрокомпьютера за счет того, что во время обратного хода развертки монитора приоритет обращения и памяти передается центральному процессору в любом из тактов цикла . 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИ)(РЕСПУБЛИН (19) (11) А1 (У1)5 С 06 Р 12/04, 12j06

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕП=НИЯМ И ОТНРЬП ИЯМ

ПРИ П(НТ СССР (21) 4460940/24 (22) 10.05.88 (46) 07.06.91. Вюл. - 21 (72) В.А. Курапин, А.К. Тесленко и В.Л. Шкловский (53) 681.327.6(088.8) (56) Патент Gi3 ¹ 2152717A, кл. G 06 P 12/04, 1985, ТИИЭР, т. 72, № 3, l984, с. 106-108. (54) УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ (57) Изобретение относится к вычислительной технике, в частности к устройствам арбитража и управления памятью,, и предназначено для использования в микрокомпьютерам, имеющих совмещенную память программ и изображения. Целью изобретения является повышение быстродействия устройства. Устройство содержит контроллер 1 монитора, мультиплексор 2 управляющих сигналов, блок 3. синхронизации, триггер 4 обращения, первый 5 и второй 6 мультиплексоры адреса. Устройство позволяет повысить быстродействие микрокомпьютера за счет того, что во время обратного хода развертки монитора приоритет обращения и памяти передается центральному процессору в любом из тактов цикла. 1 ил, 16ý4829

Изобретение относится к вычислительной технике, в частности к устройствам ар4итража и управления па3( мятью, и предназначено для использова- > .Ф .ния в микрокампьютерах, имеющих сов- . мещенную йайять Программ и изображения.

Целью изобретения является повышение быстродействия устройства. 10

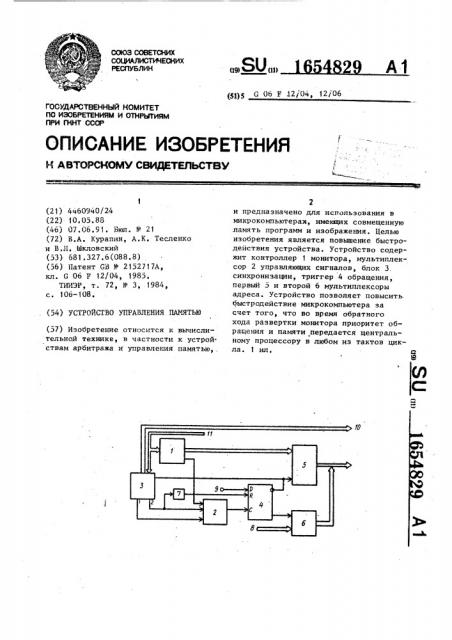

На чертеже представлена структур,ная схема устройства.

Устройство содержит контроллер 1 монитора, мультиплексор 2 управляющих сигналов, блок 3 синхронизации, триг- 15

1гер 4 обращения, первый э и второй

6 мультиплексоры адреса и формирователь 7 сигнала установки триггера обращения.

На чертеже обозначены адресные вхо- 0 ,ды 8 устройства, вход 9 запроса обра-! щения к памяти, управляющие выходы 10, устройства,:.входы 11 задания начальных условий.

Устройство работает следующим об- 25 разом.

Контроллер монитора 1 формирует сигнал гашения изображения, который

Поступает на управляющий вход мультип-: лексора 2. управляющих сигналов, на первый и второй информационные входы которого поступают импульсы с блока

3 синхронизации для опроса триггера

4 обращения. На информационный вход триггера 4 обращения подается сигнал запроса обращения процессора к памяти. Выходные сигналы триггера 4 об:ращения служат для переключения перво(,го 5 и второго 6 мультиплексоров ад-. реса,-на входы которых поступают адреса обращения к памяти от процессора

40 и контроллера монитора. Для управления памятью блок 3 синхронизации формирует сигналы управления, которые поступают на управляющие входы памя- 4 ти.

Принцип действия устройства основан на непрерывном формировании тактов обращения и памяти.

Работу устройства можно разделить на циклы, состоящие из трех тактов

Т1-ТЗ. В каждом такте блок 3 синхронизации формирует управляющие си налв для памяти по адресу, поступающему с мультиплексоров 5 и б адреса.

При разрешении изображения (сигнал на управляющем входе мультиплексора 2 управляющих сигналов равен лог.. "0") два..последних такта в цикле Т2 и ТЗ отводятся для регенераций изображения. Это означает, что такт

Т1 может быть использован процессором для обращения к памяти. Положительный фронт на тактовом входе триггера 4 обращения переключает его в единичное состояние, если на его информационный вход поступает сигнал запроса от процессора. Это приводит к тому, что обращение к памяти будет осуществляться по адресу, сформированному процессором через мультиплексор адреса.

Блок синхронизации формирует сигналы управления памятью.

В конце такта обращения процессора импульсами с выхода формирователя

7 триггер 4 обращения устанавливается в нулевое состояние.

Если процессор не обращается к памяти, то в цикле формируется холостой такт, что позволяет автоматически регенерировать память.

Время между поступлениями сигнала обращения процессора к памяти и началом выборки данных из памяти может колебаться от 0 до длительности цикла (Т,). Это время, когда процессор находится в состоянии ожидания

Т . Так как процессор обращается к памяти синхронно по отношению к тактам, формируемым блоком 3 синхронизации, то среднее время ожидания Т „ =

= Т !2.

Для уменьшения времени ожидания во .время гашения изображения к тактовому

:;входу триггера 4 обращения через мультиплексор 2 управляющих сигналов подключается дополнительный выход бло ка 3 синхронизации, формирующии сигнал утроенной частоты по отношению к основному выходному сигналу. Таким образом, во время гашения изображения триггер 4 обращения опрашивается в каждом из трех тактов цикла. Среднее время ожидания при этом уменьшается до Т, /б.

Хотя во время гашения изображения процессор может занять любой из трех тактов цикла, регенерация памяти не нарушается, так как процессор в силу ограниченности быстродействия не может занять следующий такт, который используется для регенерации памяти.

Формула изобретения

Устройство управления памятью, содержащее блок синхронизации, контролСоставитель М. Лапушкин

Техред Л.Олийнык Корректор Н. Ревская

Редактор О. Головач

Заказ 1952 Тираж 408 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.ужгород, ул. Гагарина, 1О1

1654829 6 лер монитора, первый и второй муль- сор управляющих сигналов, первый и типлексоры адреса, информационные вы- второй информационные входы которого ходы которых объединены и являются соединены с первым и вторым выходами адресными выходами устройства, входы блока синхронизации соответственно, 5 блока .синхронизации и контроллера мо- выход контроллера монитора соединен с нитора объединены и являются входами управляющим входом мультиплексора упзадания начальных условий устройства, равлякицих сигналов, информационный выгруппа выходов блока синхронизации яв- ход которого соединен с входом синхроляется управляющими выходами устрой- 10 низации триггера обращения, вход усства, группа выходов контроллера монн- тановки которого соединен с выходом тора соединена с информационными вхо- .формирователя сигнала установки тригдами первого мультиплексора адреса,, гера обращения, вход которого соедиинформационные входы второго мультип- нен с вторым выходом блока синхронизалексора адреса являются адресными вхо- 5 ции, управляющие входы первого и втодами устройства, о т л и ч а ю щ е е- рого мультиплексоров адреса соединены с я тем, что, с целью повышения быст- соответственно с инверсным и прямым родействия, в него введены триггер об- выходами триггера обращения, информаращения, формирователь сигнала уста- ционный вход которого является входом новки триггера обращения, мультиплек- 20 обращения процессора и памяти.