Устройство для вычисления свертки

Иллюстрации

Показать всеРеферат

СООЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

-РЕСПУБЛИН (19) (И) (51)5 G 06 F 15 353

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНЯТИЯМ

IlPH ГННТ СССР (21) 4704846/24 (22) 14. 06. 89 (46) 07. 06. 91. Бюп. В 21 (72) С.Н. Хлевной, В.В. Фомин, К.М. Сагдеев, П.Т. Литвиненко и К.Г. Кувшинов (53) 681.32(088.8) (56) Авторское свидетельство СССР

Ф 1246344„ кл. Н 03 Н 17/00, 1986.

Авторское свидетельство СССР

Ф 1290350, кл. С 06 F 15/332, 1987. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СВЕРТКИ (57) Изобретение относится к цифровой

2 обраьотке сигналов и может быть использовано при реализации алгоритмов спектрального анализа, цифровой фильтрации, устройств с заданными временными характеристиками на специализированных вычислительных устройствах.

Цель. изобретения — повышение производительности устройства. Цель достигается за счет того, что в устройство входят блок 1 постоянной памяти выче-! тов, п (n — целое число) арифметических блоков 2.1-2.п, мультиплексор

3, ьлок 4 постоянной памяти результа« тов, ьлок 5 постоянной памяти коэффициентов ° 1 з.п. ф-лы, 3 ил.

165483

}в !

Изобретение относится к цифровой ооработке сигналов и может быть использовано при реализации алгоритмов спектрального анализа, цифровой фильт5 рации, устройств с заданными временными характеристиками на специализированных вычислительных устройствах.

Целью изобретения является повышение производительности устройства.

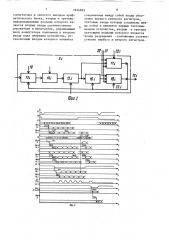

На фиг. 1 приведена функциональная схема устройства для вычисления свертки; на фиг, 2 — арифметический блок; на фиг, 3 - временные диаграммы работы устройства. 15

Устройство для вычисления свертки содержит (фиг, 1) блок 1 постоянной памяти вычетов, и арифметических блоков 2.1-2.п, мультиплексор 3, блок 4 постоянной памяти результатов, блок 5 2р постоянной памяти коэффициентов, информационныи вход 6, адресный вход 7, информационный выход 8, вход 9 задания логического нуля и вход 10 кода операции мультиплексора 3, адресный вход 11 блока 4 и выходы 12.1-12.,п соответствующих арифметических блоков 2,1-2.п.

Арифметический блок (фиг. 2) содержит коммутатор 13.i, вычитатель

14.i умножитель 15.i сумматор 16.i, регистры 17.i и 18.i вход 19 кода операции, тактовый вход 20, вход 21 ,обнуления регистров, входы 22.i u

23.i разрешения считывания соответст,вующих регистров 17.i и 18.i.

Устройство работает следующим образом.

В исходном состоянии регистры

17вi и 18вi (i=1,n) обнулены, общий сброс всех регистров происходит потенциалом логического нуля, поданного на вход 21. На управляющие входы коммутаторов 13.i (i=1 n) подан потенциал логического нуля, под действием 45 ! которого происходят коммутации первых входов коммутаторов 13. i (i=1 и) на соответствующие выходы данных блоков, Под действием кода первого нходного отсчета Х1 через время выборки адреса 4 на п выходах блока 1 поЬ.а являются коды вычетов входного отсчета Х< по соответствующим модулям

Р (i=1,n)/X>/ Р,.

Пример. Рассматривают устрой55 ство, содержащее три канала (n=3); количество отсчетов для определения одного значения свертки N = 5; осно5

А вания равны Р = 5, P = 3 и P> = 2 (таким образом Pn. = .П Р; = 30). кОМ

Через время задержки t, затрачиваемое кодами /Х,/ P на прохожде ние через соответствующие коммутаторы

13,i (i=T n) данные коды поступают на входы соответствующих вычитателей

14.i (i=1,n), K этому моменту на вторые входы вычитателей 14.i поступает код нуля с входа 9 мультиплексора 3.

Это достигается заблаговременной подачей на время выбора канала t I адреса (п-1)-го входного канала на вход t0 мультиплексора 3. В этот же момент на вход 7 подается адрес первого коэсрфициента В у.

Таким образом, через время t b на выходах вычитателей 14. i (i=1,n) появляется результат вычитания 1 Х,-О/ Р; по соответствующим модулям Р; (д=Г,п).

На и выходах 5 появляется первый кокоэффициент ) В,t Р, по соответствующим модулям Р,(i=1,n), Через время

t gа на выходах умножителей 15.i (i=

=1pn) появляется результат умножения

С =/X, В,I Р, по соответствующим модулям Р (i=1,п), К этому же моменту на выходах регистров 18.i (i=1 n) появляется код нуля. Это достигается заблаговременной, на время задержки разрешения считывания, подачей потенциа в." ла логического нуля на соответствующие входы 23.i (i=1 и}, в результате чего через время tg,a на выходах сумматоpoq 16.i (i=1,п) появляется код суммы

/С +0) P по модулям Р, (i=1,n) и в это же время на вход 20 подается короткий импульс ТИ1 записи, который ,"защелкивает" результат суммирования по модулям Р; (=1,п) в соответствующие регистры 18.i (i-=1,n).

Устройство работает в конвейерном режиме, что демонстрируется на временных диаграммах (фиг. 3), т.е. в момент поступления кода входного отсчете (Х,(+ P не входы соответствующих вычитателей 14.i (i=1,п), код второго отсчета Х подается на вход 6 и далее весь процесс выполняется аналогично изложенному (по входу 7 подается адрес коэффициента В, в сумматоре происходит сложение

/С р с С j р H теде) ° IIpo» цесс выполнения свертки реализуется до тех пор, пока И-м тактовым импульсам ТИ1 не запишется результат вычисления свертки /Уз р. -/ у С. / "Р;

2. Устройство по п. 1, о т л и ч а,ю щ е е с я тем, что арифметический блок содержит два регистра, сумматор, - умножитель, вычитатель и коммутатор, 50 выход которогo подключен K первому входу вычитателя, выход которого подключен к первому входу умножителя, выход которого подключен к информационному входу первого регистра и первоI

55 му входу сумматора, выход которого

l подключен к информационному входу второго регистра, выход которого соедиен с выходом первого регистра и под- сщ,н к второму информационному входу

5 165483 по модулям Р;(i=1,n) в соответствующие регистры 18.i (1=Т,11).

Этап округления начинается по завершению последней И-й операции вычитания Хц -О (p по модулям

Ф 5

Р1 (i 1,п) в соответствующих вычи-. та елях 14.i (i=1pn} - на управляющие входы коммутаторов 13.i (i=1,п) нодается потенциал логической единицы, под10 действием которого происходит коммутация общих выходов пар регистров

17.1 и 18.i на соответствующие выходы коммутаторов 13.i (i- 1,n), а также подачей соответствующего адреса 15 на вход 10 мультиплексора 3, реализующей через время t > подключение

1-го входа мультиплексора 3 и его выходу. После записи результата вычисление свертки по модулям Р; (i=1,n) 20 в cooTBeTcTBól0ùèå регистры 18.1 (на управляющие входы данных регистров продолжает действовать потенциал логического нуля) через время t коком ды (Y<(Р (i=1 n) поступают на . 25 первые входы соответствующих вычитателей 14.i (i=1 n) а на вторые входы миЛ ЬГ данных блоков через время t поступает код )7 / Р; (k = n). В это

Я же время на вход 7 подается адрес множителя 1/Pg (k = n) . Через время на выходах вычитателей 14.1 (i=1 и) появляется результат вычитания /Р/ /(Y5 (p.,(7 (/ (к = n) по модулям Р; (i = Г,n), а на и выходах блока 5 появляется множитель 1 1 / Рк (p (k — и) по со ответствующим модулям Р/ (i=i,n).

Через время t1.z па выходах умножителей 15.i (i=1,и) появляется резуль-40 тат умножения 1IÄ> = (/Р/, / 1/Р,(р. (ф (k = п) по соответствующим модулям

Рi (i = 1,n).

В этот же момент времени подается тактовый импульс ТИ1 на вход 20, который "защедкнет" результат первого цикла округления П; по модулям !

Рq (i 1,n) в соответствующих регист, рах 17. i (i=1 и) .

Первый цикл округления завершен, аналогично выполняются и остальные

n — 3 цикла (индекс k изменяется от и до 3).

После выполнения всей процедуры округления в регистрах 17.1 и 17.2 остается результат выполнения всего алгоритма (Y /, (i=1,2) .

Дпя преобразования результата из .. .непозиционной в позиционную системы

5 6 счисления одновременно подаются на ! входы 22, 1, 22. 2 и 11 потенциалы ло,гического нуля. Через время t >> .+tg< на выходе 8 появляется искомоезначе-; ние вычисленной свертки Y

Формула изобретения

1. Устройство для вычисления свертки, содержащее блок постоянной памяти коэффициентов, блок постоянной памяти результатов, n (n — целое число) арифметических блоков и блок постоянной памяти вычетов, i""é (i=1 n) выход которого подключен к первому информационному входу i-го арифметического блока, второй информационный вход которого подключен к i-му выходу блока IlocToHHHoII памяти коэффициенТоВр Bblxo+ j l o (jPP1pt1p m + n) BPH@ метического блока подключен к j-му адресному входу блока постоянной памяти результатов, выход которого является информационным выходом устройства, информационным и адресным входами которого являются адресные входы сооТветственно блока постоянной памяти вычетов и блока постоянной памяти коэффициентов, о т л и ч а ю щ е е с я тем, что, с целью повышения производительности устройства, оно содержит коммутатор, выход которого подключен к третьему информационному входу i-ro арифметического блока, выход 1-го (1 = ш+1, n) арифметического блока подключен к (1-ш)-му информационному входу мультиплексора, (и-в+1) -й информационный вход которого является входом задания логического вЂ,нуля устройства, первым входом кода операции которого является управляющий вход мультиплексора.

1654835

Вых

1,i

Вых

1З. i

Вых

Вых

8,i

Вюх

5,/

Вых тл гз,i

Вмх

17. 1иР.

Вы

В коммутатора и является выходом арифметического блока, вторым и третьим информационными входами которого яв-: ляются вторые входы соответственно умножителя и вычитателя, управляющий

Вход коммутатора подключен к второму входу кода операции устройства, установочным входом которого являются йи

1а1

Вы

16,1

_#_ тИ1 гг,с соединенные между собой входы обнуления первого ивторого регистров, тактовые входы которых соединены между собой и являются первым тактовым входом устройства, вторым и третьим тактовыми входами которого являются г входы разрешения - считывания соответственно первого и второго регистров, !