Запоминающее устройство для микропроцессорной вычислительной системы

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных устройств с неизменяемой программой на основе микропроцессоров. Целью изобретения является повышение быстродействия запоминающего устройства. Запоминающее устройство содержит первый 1 и второй 2 блоки памяти, детектор 3 длины команды, вычитающий счетчик 4 с предустановкой, дешифратор 5 нулевого кода, первый формирователь 6 коротких импульсов, первый триггер 7, элемент ИЛИ 8, первый элемент И-НЕ 9, второй триггер 10, второй формирователь 11 коротких импульсов, второй 12 и третий 13 элементы И-НЕ. При чтении команды микропроцессор обращается к первому блоку памяти, а при исполнении команды (чтении или записи данных) - к второму блоку памяти. Так как переключение страниц памяти (блоков памяти) происходит в то рремя, как считанная команда выполняется микропроцессором, удвоение адресуемой микропроцессором памяти не приводит к потерям машинного времени. Это увеличивает быстродействие запоминающего устройства и всей микропроцессорной системы. 3 ил. с « (/

СОЮЗ СОВЕТСНИХ

РЕСПУБЛИК аю оо (51)5 С 11 С 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4720744/24 ,(22) 19. 07.89 (46) 07.06.91. Бюл. Р 21 (72) В.С.Погорелов и Я.И.Торошанко (53) 681.327.66 (088.8) (56) Авторское свидетельство СССР

Р 1361623, кл. С 11 С 11/00, 1987.

Балашов. E.Ï. и др. Микро- и миниЭВМ; — Л.: Энергоатомиздат, 1984, рис. 3 - 37 ° (54) ЗАПОМИНА7 )ЩЕЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ (57) Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных устройств с неизменяемой программой на основе микропроцессоров. Целью изобретения является повышение быстродействия запоминающего устройства.

Эапоминающее устройство содержит первый 1 и второй 2 блоки памяти, детектор 3 длины команды, вычитающий счетчик 4 с продустановкой, дешифратор 5 нулевого кода, первый формирователь

6 коротких импульсов, первый триггер7, элемент ИЛИ 8, первый элемент И-НЕ

9, второй триггер 70 второй формирователь 11 коротких импульсов, второй

12 и третий 13 элементы И-НЕ. При чтении команды микропроцессор обращается к первому блоку памяти, а при исполнении команды (чтении или записи данных) — к второму блоку памяти. Так как переключение страниц памяти (блоков памяти) происходит в то рремя, как считанная команда выполняется микропроцессором, удвоение адресуемой микропроцессором памяти не приводит к потерям машинного времени.

Это увеличивает быстродействие запоминающего устройства и всей микропроцессорной системы. 3 ил.

1654871

Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных устройств с неизменяемой программой на основе микропроцессоров.

Целью изобретения является повышеНие быстродействия запоминающего устройства.

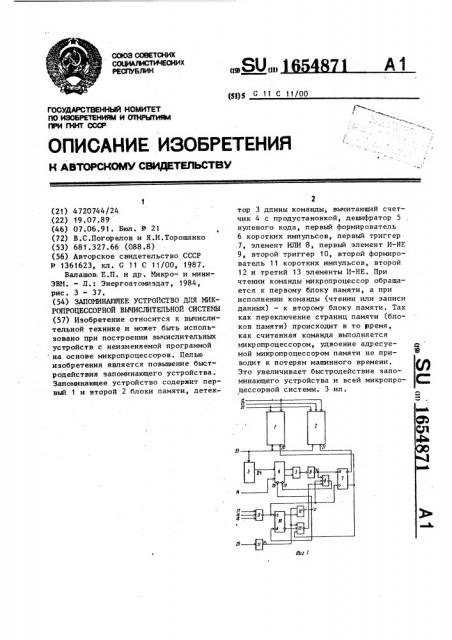

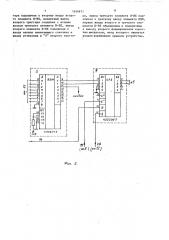

На фиг.1 представлена функциональ- 10 йая схема запоминающего устройства, йа фиг.2 — возможное построение детектора длины команды и вычитающего счетчика с предустановкой, на фиг.3—

Возможные реализации формирователей 15

Коротких импульсов.

Запоминающее устройство содержит первый 1 и второй 2 блоки (страницы) памяти, детектор 3 длины команды, вычитающий счетчик 4 с предустановкой, 20 дешифратор 5 нулевого кода, первый формирователь 6 коротких импульсов, первый триггер 7, элемент ИЛИ 8, первый элемент И-НЕ 9, второй триггер

10, второй формирователь 11 коротких 25 импульсов,. второй 12 и третий 13 элементы И-НЕ °

Запоминающее устройство работает следующим образом.

По сигналу "Сброс", поступающему из микропроцессора на вход 14 сброса. устройства, счетчик 4 устанавливается в нулевое состояние. После этого микропроцессор начинает цикл чтения команды. Микропроцессор подает на ад- «» ресный вход 15 устройства код адреса, а на вход 16. синхронизации устройства — сигнал синхронизации. Первым машинным циклом микропроцессора после сброса является цикл чтения кода 10 операции. Признаком этого является поступление сигнала чтения кода операции на вход 17 управления чтением кода операции устройства. Например, для микропроцессора К580ИК80 этим сигналом является сигнал признака цикла М1. В момент поступления на

: тактовый вход 18 устройства сигнала тактового. генератора на выходе элемента И-НЕ 9 формируется сигнал низкого уровня, который устанавливает в

"1" триггеры 7 и 10, а также проходит через элемент ИЛИ,8 на вычитающий вход 19 счетчика 4 и устанавливает в нем ненулевой код.

Разрешающий потенциал с прямого выхода первого триггера 7 поступает на вход 20 выборки первого блока 1 памяти и на третий вход элемента И-HE

13. На вход 21 выборки второго блока 2 памяти поступает запрещающий потенциал с инверсного выхода триггера

7. Си| налы с прямого и инверсного выходов триггера 10 соответственно разрешают работу элемента И-НЕ 12 н запрещают работу элемента И-НЕ 13. По сигналу "Чтение" на входе 22 управления чтением устройства из блока 1 памяти на информационный вход-выход 23 устройства считывается код операции, который поступает в микропроцессор.

Одновременно этот код поступает на вход детектора 3 длины команды, формируя на его выходе 24 двоичный код, соответствующий числу байт (слов), необходимьм для полного считывания команды, уменьшенному на единицу.

По сигналу приема на входе 25 управления приемом устройства на вьмоде формирователя 11 формируется короткий импульс положительной полярности. В результате на выходе элемента И-НЕ 12 формируется импульс отрицательной полярности, поступающий на вход 26 записи счетчика 4, который заносит код детектора длины команды в счетчик 4.

Кроме того, этот импульс устанавливает в "0" триггер 10, закрывая элемент И-НЕ 12 и открывая элемент И-НЕ

13.

Если в счетчике 4 оказывается нулевой код, то на выходе дешифратора

5 нулевого кода формируется положительный уровень напряжения (логическая "1"). Дпя двухразрядного кода в счетчике 4 детектор 5 нулевого кода может быть реализован на элементе

2ИЛИ-НЕ. Сигнал с выхода дешифратора

5 запускает формирователь 6 коротких импульсов, отрицательный импульс на выходе которого устанавливает триггер 7 в нулевое состояние, а также через элемент ИЛИ 8 проходит на вычитающий вход 19 счетчика 4, формируя в нем ненулевой код. При этом сигнал логической единицы с инверсного выхода триггера 7 поступает на вход 21 выборки второго блока 2 памяти, разрешая егo работу, а сигнал логического нуля с прямого выхода триггера 7 запрещает работу первого блока 1 памяти. В результате в последующих машинных циклах данной команды микропроцессор обращается к блоку 2 памяти, в котором хранятся данные.

Если одно из последующих обращений микропроцессора в память являет16548 71

45 ся записью данных, то код данных подается на информационный вход-выход устройства 23, а на вход 27 управления записью устройства пос-.упает сигнал записи.

Для команд микропроцессора, требующих чтения нескольких байт (слов) из блока 1 памяти, сигнал на выходе деыифратора 5 после первого цикла чтения (чтения кода операции) отсутствует, так как в счетчике 4 присутствует ненулевой код. При чтении следующих байт (слон) по сигналам приема на входе 25 устройства на выходе формирователя 11 появляется импульс, который через элементы И-НЕ 13 и ИЛИ

8 поступает на вычитающий вход 19 счетчика 4 и уменьшает на единицу записанньп» н нем код до тех пор, пока он не становится равным нулю.

Формирование ненулевого кода н счетчике 4 .после сброса микропроцессора (и обнуления счетчика 7), а также после окончания выполнения считывания каждой команды необходимо для того, чтобы на выходе дешифратора нулевого кода 5 обеспечить положительньп» перепад напряжения в том случае, если первая после сброса и любая следующая команда будут длиной один байт (одно слово) и в счетчик 4 с выхода детектора длины команды 3 будет заноситься нулевой код.

Схема возможной реализации на интегральных микросхемах детектора 3 длины команды и вычитающего счетчика 4 с предустановкой показана на фиг.2. В случае, если при чтении кода опера»»ии считан недопустимый код, 4О детектор формирует сигнал ошибки, которьп» может быть подан н микропроцессор для аварийной остановки. Возможная реализация формирователей коротких импульсов и временные диаграммы их работы показаны на фиг.3.

Таким образом, при чтении команды (кода операции и оперантон или адресов) микропроцессор обращается к блоку 1 памяти, а при исполнении коман- 5р ды (чтении из оперативной памяти или записи в нее) микропроцессору предоставляется блок 2 памяти, Следующая команда микропроцессора опять начинается с машинного цикла чтения кода операции и осуществляется аналогично.

Так как переключение страниц памяти (блоков памяти) происходит в то время, как считанная команда ныполняется микропроцессором,. удвоение адресуемой м»»кропроПессором памяти не приводит к потерям машинного времени.

Это увеличивает быстродействие запоминающего устройства и всей микропроцессорной системы.

Формула и з обр ет ения

Запоминающее устройство для микропроцессорной вычислительной системы, содержащее первый и второй блоки памяти, адресные входы которых объединены и являются адресным входом устройства, информационные входы-выходы объединены и являются информационным нходом-выходом устройства, входы управления чтением объединены и являются входом управления чтением устройства, а вход управления записью второго блока памяти является входом управления записью устройства, о т л и ч а ю щ е е с я тем, что, с целью поньш»ения быстродействия, в него введены детектор длины команды, нычитающий счетчик с предустановкой, первый и второй триггеры, дешифратор нулевого кода, первый и второй формирователи коротких импульсов, элемент

ИЛП, перньпt, второй и третий элементы

И-НГ, причем вход детектора длины команды с.оед»»не»» с информационным входом-выходом устройства, а его выход соединен с входом предустановки вычитающего счетчика, вход установки в нулевое состояние вычитающего счетчика является входом сброса устройства, выходы нычитающего счетчика подключе- ны к входам дешифратора нулевого кода, выход которого через первый формирователь коротких импульсов соединен с входом установки в "О" первого триггера и первым входом эЛемента 11»П ., выход элемента ИЛИ подключен к вычитающему входу нычитающего счетчика, прямой выход первого триггера соединен с входом выборки первого блока памяти и третьим входом третьего элемента И-НЕ, а инверсный выход первого триггера подключен к входу выборки второго блока памяти, первьн», второй и третий входы первого элемента И-НЕ являются соответственно входом управления чтением кода операции, входом синхронизации и тактовьм входом устройства, а его выход соединен с входом установки в "1" второго триггера, вторым входом элемента

ЮП1 и входом установки в "1" первого триггера, прямой выход второго триг7

16548 71 гера подключен к второму входу второt о элемента И-НЕ, инверсный выход

Второго триггера соединен с вторым

Входом третьего элемента И-НЕ, выход второго элемента И-НЕ подключен к

Входу записи вычитающего счетчика и Входу установки в "О" второго тригге-. ра, выход третьего элемента И-НЕ подключен к третьему входу элемента ИЛИ, первые входы второго и третьего элементов И-НЕ объединены и подключены к выходу второго формирователя коротких импульсов, вход которого является входом управления приемом устройстве.

1Ü54871 кРВ Рог. 3.

Составитель Г.Аникеев

Редактор И.щербак Техред Л.Олийнык Корректор Л.Патай

Заказ 1954 Тираж 350 Подписное

ВНИИПИ Государственного комитета но изобретениям и открытиям при ГЕНТ СССР !

13035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101