Преобразователь код - временной интервал

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах преобразования и кодирования информации. Целью изобретения является расширение области применения преобразователя за счет обеспечения циклического преобразования асинхронно изменяющегося во времени входного кода. Преобразователь содержит генератор импульсов, два регистра , шины входного кода, блок сравнения кодов, D-триггер, счетчик импульсов, два элемента И, / 5-триггер, шину записи, четыре элемента ИЛИ, шину сброса и выходную шину. Преобразователь формирует импульсную последовательность с интервалами, пропорциональными последовательности входных кодов, причем в схеме предусмотрена защита от возможных сбоев при совпадении импульса на шине записи с импульсом на выходной шине путем повторной записи информации в регистр. 2 ил.

СООЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 03 M 1 82

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

llO ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4710378/24 (22) 26.06.89 (46) 07.06.91. Бюл. № 21 (72) Е. В. Юланова и В. М. Низель (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 1187275, кл. Н 03 М 1/82, 1983.

Авторское свидетельство СССР № 1115225, кл. Н 03 М 1/82, 13.05.83. (54) ПРЕОБРАЗОВАТЕЛЬ КОД вЂ ВРЕМЕ Н НОЙ И HTE PB АЛ (57) Изобретение относится к вычислительной технике и может быть использовано в устройствах преобразования и кодирования информации. Целью изобретения является расширение области применения преобразоИзобретение относится к вычислительной технике и может быть использовано в устройствах преобразования и кодирования информации.

Целью изобретения является расширение области применения преобразователя за счет обеспечения циклического преобразования асинхронно изменяющегося во времени входного кода.

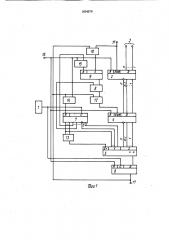

На фиг. 1 приведена структурная электрическая схема преобразователя; на фиг. 2 — временные диаграммы его работы.

Преобразователь содержит генератор 1 импульсов, регистр 2, шины 3 входного кода, регистр 4, блок 5 сравнения кодов, .0-триггер 6, счетчик 7 импульсов, элемент И 8, RS-триггер 9, элемент И 10, шину 11 записи, элементы ИЛИ 12 — 15, шину 16 сброса и выходную шину 17.

Преобразователь работает следующим образом.

Сигналом по шине 16 обнуляются регистры 2 и 4, триггеры 6 и 9 и счетчик 7 им„SU, 1654979 А 1 вателя за счет обеспечения циклического преобразования асинхронно изменяющегося во времени входного кода. Преобразователь содержит генератор импульсов, два регистра, шины входного кода, блок сравнения кодов, D-триггер, счетчик импульсов, два элемента И, RS-триггер, шину записи, четыре элемента ИЛИ, шину сброса и выходную шину. Преобразователь формирует импульсную последовательность с интервалами, пропорциональными последовательности входных кодов, причем в схеме предусмотрена защита от возможных сбоев при совпадении импульса на шине записи с импульсом на выходной шине путем повторной записи информации в регистр. 2 ил. пульсов, при этом в счетчик 7 записывается число «2», в оба регистра — «1», по крайней мере, в один из старших разрядов из диапазона рабочих кодов (например, в старши и р аз ряд) . Последнее реал изуется испол ьзованием инверсных выходов второго разряда счетчика 7 и старших разрядов регистров .2 и 4.

После снятия сигнала сброса счетчик 7 начинает подсчет тактовых импульсов.

При заполнении счетчика 7 кодом, совпадающим с кодом в регистре 4, на выходе блока 5 появляется высокий уровень, который вызывает срабатывание D-триггера 6.

Импульс с выхода D-триггера 6 поступает на выходную шину 17, а также через элемент ИЛИ 12 выдает разрешение на списывание информации из регистра 2 в регистр 4 и через элемент ИЛИ 14 сбрасывает счетчик 7 (с записью в него кода «2»), после чего счетчик начинает формировать новый интервал времени. Работа схемы повторяется с имеющимся в регистре 2 кодом до прихода сигнала записи по шине 11 в произволь1654979

Формула изобретения

3 ный момент времени. При этом информация с шин 3 записывается в регистр 2 и очередным импульсом с выхода D-триггера 6 переписывается в регистр 4.

Импульсы на выходе блока 5 и, соответственно, на выходной шине 17 формируются с периодом, определяемым кодом в регистре 4. Для исключения возможности ложного срабатывания D-триггера 6 из-за переходного процесса при изменении информации в регистре 4 осуществляется (через элемент 13 ИЛИ) разрешение сравнения текущего кода счетчика 7 и кода в регистре 4 только в диапазоне рабочих кодов, что обеспечивается подключением к входам элемента 13 ИЛИ старших разрядов кодов рабочего диапазона.

В схеме предусмотрено исключение возможных сбоев в работе преобразователя, при совпадении импульса с выходной шины ! 7 с импульсом на шине 11 записи (при таком совпадении в регистр 4 может быть записан еше не установившийся искаженный код с выходов регистра 2).

Совпадение указанных импульсов фиксируется элементом И 10, выходной импульс которого устанавливает RS-триггер 9 в единичное состояние, Высокий потенциал с выхода RS-триггера выдает разрешение на прохождение импульса с выхода i-го разряда счетчика импульсов через элемент И. 8 и элемент ИЛИ 12 на вход разрешения записи регистра 4, чем обеспечивается повторная запись уже правильной информации из регистра 2 в регистр 4 (при этом блок 5 сравнения кодов закрыт сигналом с выхода элемента ИЛИ 13). RS-триггер обнуляется сиг, налом с выхода старшего по отношению к, -му разряду счетчика через элемент ИЛИ 15.

Таким образом, в преобразователе обеспечивается возможность непрерывного преобразования асинхронно изменяющегося входного кода во временные интервалы, соответствующие текущему значению входного кода.

Преобразователь код — временной интервал, содержащий RS-триггер, первый и второй элементы И, счетчик импульсов, первый

4 регистр, информационные входы которого являются соответствующими шинами входного кода, а вход разрешения записи является шиной записи, блок сравнения кодов, первые информационные входы которого соединены с соответствующими выходами счетчика импульсов, D-триггер, D-вход которого соединен с выходом блока сравнения кодов, а С-вход — с выходом генератора импульсов, отличающийся тем, что, с целью расширения области применения преобразователя путем обеспечения циклического преобразования асинхронно изменяющегося во времени входного кода, в него введены первый, второй, третий и четвертый элементы ИЛИ и второй регистр, информационные входы которого соединены с соответствующими выходами первого регистра, выходы соединены с соответствующими вторыми информационными входами блока сравнения кодов, вход сброса объединен с входом сброса первого регистра, R-входом D-триггера, первыми входами третьего и четвертого элементов ИЛИ и является шиной сброса, а вход разрешения записи соединен с выходом. первого элемента ИЛИ, первый вход которого объединен с вторым входом третьего элемента ИЛИ и первым входом второго элемента И, подключен к выходу Dтриггера и является выходной шиной, а второй вход первого элемента ИЛИ соединен с выходом первого элемента И, первый вход которого подключен к выходу младшего из группы средних разрядов счетчика импульсов, а второй вход — к выходу

RS-триггера, S-вход которого соединен с выходом второго элемента И, второй вход которого является шиной записи, R-вход

RS-триггера подключен к выходу четвертого элемента ИЛИ, второй вход которого соединен с выходом старшего из группы средних разрядов счетчика импульсов, вход сброса которого подключен к выходу третьего элемента ИЛИ, счетный вход — к выходу генератора импульсов, а выходы группы старших разрядов счетчика импульсов соответственно подключены к входам второго элемента ИЛИ, выход которого соединен с входом разрешения сравнения блока сравнения кодов.

1654979

l654979

ode

/ВРИ

Составитель В. Войтов

Редактор И. Дербак Техред А. Кравчук Корректор Л. Патай

Заказ 1959 Тираж 470 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-издательский комбинат «Патент», г. Ужгород, ул. Гагарина, 101