Многоканальная система регистрации аналоговых сигналов

Иллюстрации

Показать всеРеферат

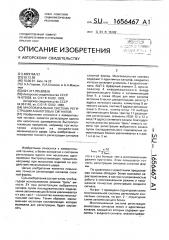

Изобретение относится к измерительной технике, касается регистрации одного или нескольких одновременно быстропротекающих процессов, например при испытании изделий на воздействие механического удара. Цель изобретения - повышение точности регистрации сигналов сложной формы. Мноюканальная система содержит п идентичных каналов, каждый из которых включает усилитель 1 входного сигнала , АЦП 2, буферный элемент 3, мультиплексор 4 информационного входа запоминающего блока и запоминающий блок 5, а также общие для всех каналов источник 6 частот дискретизации, регистр 7 адреса активного канала, коммутатор 8 активного канала, счетчик 9 адреса запоминающего блока, коммутатор 10 выбора запоминающего блока, триггер 11 разрешения регистрации, элементы ИЛИ 12 и 13 и вход 14 адреса активного канала. Благодаря использованию режима Цепь емкость памяти при регистрации выбранного канала путем последовательного подключения запоминающих блоков увеличивается в п раз. 1 з.п.ф-лы. 2 ил. (Л С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5П5 G 01 R 13/02

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ, ГКНТ СССР

ОПИСАНИЕ ИЗО6РЕТЕНИЯ К АВТОРСКОМУ СВИ4ЕТЕЛЬСТВУ (21) 4622164/21 (22) 20.12.88 (46) 15.06,91. Бюл. M 22 (72) А,А.Гашеев, И.А.Коченов и Б.А.Максимов (53) 621.317,755 (088.8) (56) Авторское свидетельство СССР

М 673928, кл. G 01 R 13/02, 1978.

Авторское свидетельство СССР

М 951146, кл. G 01 R 13/02, 1980. (54) МНОГОКАНАЛЬНАЯ СИСТЕМА РЕГИСТРАЦИИ АНАЛОГОВЫХ СИГНАЛОВ (57) Изобретение относится к измерительной технике, касается регистрации одного или нескольких одновременно быстропротекающих процессов, например при испытании изделий на воздействие механического удара. Цель изобретения— повышение точности регистрации сигналов

Изобретение относится к измерительной технике, а более конкретно к системам регистрации одного или нескольких одновременно быстропротекающих процессов, например при испытании иэделий на воздействие механического удара.

Целью изобретения является повышение точности регистрации сигналов сложной формы.

Суть изобретения состоит в том, что благодаря использованию режима "Цепь" емкость ЗУ при регистрации выбранного сигнала путем последовательного подключения запоминающих блоков увеличивается в п раз, где n — количество каналов многоканальной системы. Таким образом, максимальная частотная составляющая, которая возможна для регистрации, будет составлять Ы „1656467 Al сложной формы. Многоканальная система ,содержит и идентичных каналов, каждый иэ которых включает усилитель 1 входного сигнала, АЦП 2, буферный элемент 3, мультиплексор 4 информационного входа запоминающего блока и запоминающий блок 5, а также общие для всех каналов источник 6 частот дискретизации, регистр 7 адреса активного канала, коммутатор 8 активного канала, счетчик 9 адреса запоминающего блока, коммутатор 10 выбора запоминающего блока, триггер 11 разрешения регистрации, элементы ИЛИ 12 и 13 и вход 14 адреса активного канала, Благодаря использованию режима "Цепь" емкость памяти при регистрации выбранного канала путем последовательного подключения эапоминающих блоков увеличивается в и раэ.

1 э.п.ф-лы, 2 ил, и N

1макс л Тимп что в п раэ больше, чем в многоканальном режиме прототипа. Этим повышается точность регистрации сигналов сложной формы.

По сравнению с известными предлагаемая система обладает более высокими характеристиками, в частности воэможностью работы в многоканальном режиме и повышенной точностью регистрации входного сигнала.

На фиг. 1 приведена структурная схема многоканальной системы регистрации аналоговых сигналов; на фиг. 2 — структурная схема запоминающего блока.

Многоканальная система регистрации аналоговых сигналов имеет и идентичных каналов, каждый из которых содержит усилитель 1 входного сигнала, аналого- цифро1656467 вой преобразователь (АЦП) 2, буферный элемент 3, мультиплексор 4 информационного входа запоминающего блока и запоминающий блок 5, а также общие для всех каналов источник 6 частот дискретизации, регистр 7 адреса активного канала, ко гмутатор 8 активного канала, счетчик 9 адреса запоминающего блока, коммутатор 10 выбора запоминающего блока, триггер 11 разрешения регистрации, элементы ИЛИ 12 и

13, вход 14 задания адреса активного канала, При этом в каждом канале усилители 1 входного сигнала соединены с информационными входами АЦП 2, выходы которых подключены к информационным входам буферных элементов и первым информационным входам мультиплексоров 4 информационного входа запоминающего блока, выходы которых соединены с информационными входами запоминающих блоков 5, выходы буферных элементов 3 объединены и подключены к вторым входам мультиплексоров 4. Выходы переполнения запоминающих блоков 5 объединены и подключены к счетному входу счетчика 9 адреса ( запоминающего блока, выход которого подключен к информационному входу коммутатора 10 выбора запоминающего блока, первый управляющий вход которого соединен с выходом триггера 11 разрешения регистрации, вход сброса которого подключен к выходу переполнения счетчика 9 адреса, Вход сброса счетчика 9 адреса и вход установки триггера 11 подключены к входу 15 внешнего запуска. Управляющие входы мультиплексоров 4, управляющий вход коммутатора 8 и вход направления счета счетчика 9 адреса подключены к входу 16 задания режима "Цепь". Вход регистра 7 адреса является входом 14 задания адреса активного канала, а выход его соединен с информационным входом коммутатора 8 активного канала, выход которого соединен с входами разрешения передачи буферных элементов 3, Выход источника частот дискретизации соединен с входами запуска АЦП

2 каждого канала.

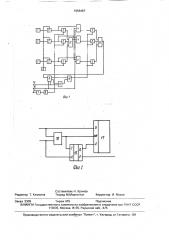

Запоминающий блок 5 (фиг, 2) содержит запоминающее устройство 17 с произвольной выборкой, элемент И 18 и счетчик 19 адреса ячейки запоминающего устройства, Запись в запоминающий блок 5 производится только при наличии сигнала "Разрешение записи", а после записи информации в последнюю ячейку памяти на выходе 38llo" минающего блока 5 формируется сигнал

"Заполнен".

Предлагаемая система может работать в обычном режиме и в режиме "Цепь".

В обычном режиме (на входе задания режима "Цепь" — логический "0") коммутатор 8 активного канала запрещает передачу информации через все буферные элементы

3, а реверсивный счетчик 9 адреса запоминающего блока работает нэ вычитание. Импульс на входе внешнего запуска обнуляет счетчик 9 адреса запоминающего блока и устанавливает триггер 11 разрешения регистрации. Работа коммутатора 10 выбора запоминающего блока разрешается по первому управляющему входу, логический

"0" на втором управляющем входе коммутатора 10 обеспечивает выдачу сигнала "Разрешение записи" на запоминающие блоки 5 всех каналов.

В каждом канале регистрируемый сигнал через входной усилитель 1 поступает на

АЦП 2, где с частотой дискретизации, поступающей с источника 6 частот дискретизации, преобразуется в цифровой код и через первый информационный вход мультиплексора 4 поступает на информационный вход запоминающего блока 5 данного канала.

После записи информации в последнюю ячейку на выходе запоминающих блоков 5 формируется сигнал "Заполнен", поступающий на счетный вход счетчика 9 адреса запоминающего блока. Так как счетчик обнулен и включен на вычитание, на выходе переполнения формируется сигнал, сбрасывающий триггер 11 разрешения регистрации. Работа коммутатора 10 выбора запоминающего блока запрещается по первому управляющему входу, Таким образом, производится запись и регистрируемых сигналов по и каналам, При работе в режиме "Цепь" (на входе задания режима "Цепь" — логическая "1") коммутатор 8 активного канала разрешает передачу информации через буферный элемент 3 канала, адрес которого предварительно записан в регистр 7 адреса активного канала через вход 14 задания адреса активного канала, а реверсивный счетчик 9 адреса запоминающего блока работает на сложение. Импульс на входе элемента ИЛИ 12 обнуляет счетчик 9 адреса запоминающего блока и устанавливает триггер 11 разрешения регистрации, Работа коммутатора 10 выбора запоминающего блока разрешается по первому управляющему входу, логическая "1" на втором управляющем входе коммутатора 10 обеспечивает выдачу сигнала "Разрешение записи" на запоминающий блок 5, адрес которого содержится в счетчике 9 адреса запоминающего блока.

Регистрируемый сигнал, поступающий на вход канала, адрес которого содержится

1656467 в регистре 7 адреса активного канала, через входной усилитель 1 поступает на АЦП 2, где с частотой дискретизации, поступающей с источника 6 частот дискретизации, преобразуется в цифровой код и через второй информационный вход мультиплексоров 4 поступает на информационный вход запоминающих блоков 5 всех каналов. Однако запись производится только в тот запоминающий блок 5, на который поступает сигнал "Разрешение записи" с коммутатора

10 выбора запоминающего блока. После записи информации в последнюю ячейку на выходе запоминающего блока 5 формируется сигнал "Заполнен", поступающий на счетный вход счетчика 9 адреса запоминающего блока и увеличивающий на единицу содержащийся в нем адрес. Коммутатор 10 переключает сигнал "Разрешение записи" на следующий запоминающий блок 5, После записи информации в последний запоминающий блок 5 на выходе переполнения счетчика адреса запоминающего блока 9 формируется сигнал, сбрасывающий триггер 11 разрешения регистрации, работа коммутатора 10 выбора запоминающего блока запрещается по первому управляющему входу. Таким образом происходит запись одного регистрируемого сигнала, поступающего на вход канала, адрес которого содержится в регистре 7 адреса активного канала, последовательно в запоминающие блоки 5 всех каналов.

Формула изобретения

1. Многоканальная система регистрации аналоговых сигналов, содержащая в каждом канале последовательно соединенные усилитель входного сигнала и аналогоцифровой преобразователь, а также запоминающий блок и общие для всех каналов источник частот дискретизации и вход внешнего запуска системы, о т л и ч а ю щ ая с я тем, что, с целью повышения точности регистрации сигналов сложной формы, в нее введены в каждый канал буферный элемент и мультиплексор информационного входа запоминающего блока, а также общий для всех каналов регистр адреса активного канала, коммутатор активного канала, счетчик адреса запоминающего блока, коммутатор выбора запоминающего блока и триггер разрешения регистрации, причем в каждом канале выходы аналого-цифровых преобразователей соединены с информационными входами буферных элементов и с первыми информационными входами мультиплексоров информационного входа запо-: минающего блока. выходы буферных элементов всех каналов через первый элемент

ИЛИ соединены с вторымй информацион5 ными входами мультиплексоров информационного входа запоминающего блока, выходы которых соединены с информационными входами запоминающих блоков, вход регистра адреса активного канала соединен

10 с внешним входом задания адреса активного канала, выход регистра адреса активного канала соединен с информационным входом коммутатора активного канала, выход которого подключен к управляющим входам

15 буферных элементов каждого канала, выходы переполнения запоминающих блоков всех каналов через второй элемент ИЛИ соединены со счетным входом счетчика адреса запоминающего блока, информационный

20 выход счетчика адреса запоминающего блока соединен с информационным входом комутатора выбора запоминающего блока, выход которого соединен с управляющими входами запоминающих блоков каждого ка25 нала, вход установки триггера разрешения регистрации и вход сброса счетчика адреса запоминающего блока соединены с входом внешнего запуска, вход сброса триггера разрешения регистрации соединен с выхо30 дом переполнения счетчика адреса запоминающего блока, выход триггера разрешения регистрации соединен с первым управляющим входом коммутатора выбора запоминающего блока, управляющий вход

35 коммутатора активного канала и вход направления счета счетчика адреса запоминающего блока соединены с входом задания режима "Цепь", выход источника частот дискретизации соединен с входами запуска

40 аналого-цифровых преобразователей каждого канала, 2. Система по и. 1, от л и ча ю ща я ся тем, что запоминающий блок содержит элемент И, счетчик адреса и запоминающий

45 блок, при этом выход элемента И соединен со счетным входом счетчика адреса и входом разрешения записи запоминающего блока, информационный выход счетчика соединен с адресным входом запоминающего

50 блока, а выход переполнения счетчика адреса соединен с выходом запоминающего блока, первый вход запоминающего блока соединен с входом данных запоминающего блока и первым входом элемента И, второй

55 вход запоминающего блока соединен с входом сброса счетчика адреса и вторым входом элемента И.

1656461 (Ддг 1

Составитель Н, Кринов

Техред М.Моргентал Корректор И, Муска

Редактор Т. Клюкина

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 2309 Тираж 415 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5