"устройство реализации операции "/х/-произведение @ -мерных кубов"

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для использования в качестве устройства операционного блока для специализированной ЦВМ, реализующей алгоритмы минимизации булевых функций синтеза и анализа логических схем Цель изобретения - повышение быстродействия реализации и сокращение аппаратных затрат Устройство содержит п вычислительных ячеек 1 и решающий узел 2, ч го позволяет произвести счемгую параллельную реализацию операции произвел ние n-мерных кубов. 3 ил

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5!)5 G 06 F 7/00

ГОСУДАPСТВЕННЫИ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Таблица 2 (21) 4711936/24 (22) 16.05.89 (46) 15,06.91. Бюл. ¹ 22 (72) А.Ш.Альбеков и Е.P.Ãåðàñèìoâ (53) 681.325(088.8) (56) Авторское свидетел ьство СССР

N 1001080, кл. G 06 F 7/00, 1981.

Авторское свидетельство СССР № 1196844, кл. G 06 F7/00,,1983. (54) УСТРОЙСТВО РЕАЛИЗАЦИИ ОПЕРАЦИИ "/Х/ — ПРОИЗВЕДЕНИЕ N-МЕРНЫХ

КУБОВ"

Изобретение относится к вычислительной технике и может быть использовано при создании специализированных ЦВМ с расширенными логическими возможностями, реализующих алгоритмй минимизации булевых функций, синтеза и анализа логических схем, Цель изобретения — повышение быстродействия и сокращение аппаратных затрат.

Цель изобретения достигается путем схемной параллельной реализации операции "х-произведение и-мерных кубов".

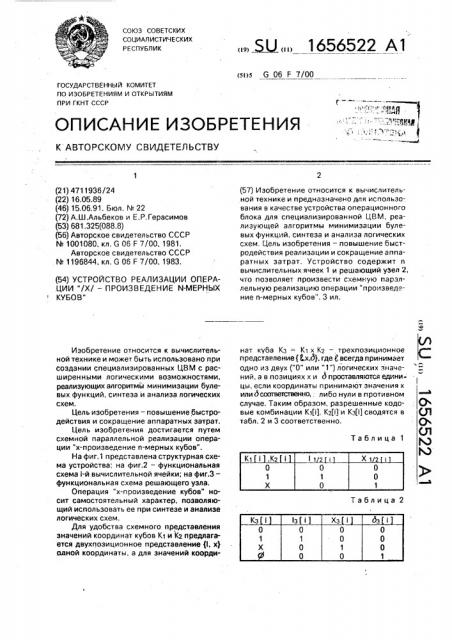

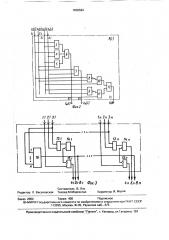

На фиг.1 представлена структурная схема устройства; на фиг.2 — функциональная схема i-й вычислительной ячейки; на фиг,3— функциональная схема решающего узла.

Операция "х-произведение кубов" носит самостоятельный характер, позволяющий использовать ее при синтезе и анализе логических схем.

Для удобства схемного представления значений координат кубов К1 и К2 предлагается двухпозиционное представление {I, x) аиной координаты, а для значений коорди„„5U„„1656522 Al (57) Изобретение относится к вычислительной технике и предназначено для использования в качестве устройства операционного блока для специализированной ЦВМ, реализующей алгоритмы минимизации булевых функций, синтеза и анализа логических схем. Цель изобретения — повышение быстродействия реализации и сокращение àïïàратных затрат. Устройство содержит и вычислительных ячеек 1 и решающий уЗел 2, что позволяет произвести схемную параллельную реализацию операции "произведение и-мерных кубов", 3 ил.

I» нат куба Кз = К1 х Kz — трехпозиционное представление { З,x3), где 3 всегда принимает одно из двух ("0" или "1") логических значений, а в позициях х и д проставляются единицы, если координаты принимают значения х ! или д соответственно,: либо нули в противном случае. Таким образом, разрешенные кодо- О вые комбинации Кф), К2(() и Кз(!) сводятся в (Л табл. 2 и 3 соответственно. о

Q1

Таблица 1 (Я

1656522

Кроме того, в соответствии стем, что (х)-произведение кубов осуществляется в два этапа, вводится трехпозиционное представление (4, хя, уя} предварительного значения координат результирующего куба Кз. 5

Таблица 3

Устройство, реализующее операцию 15

"/х/-произведение и-мерных кубов" К (1: n) и Кр (1: и), содержит и вычислительных ячеек, имеющих входы и выходы согласно табл.

1 и 3 и один решающий узел, имеющий входы и выходы согласно табл. 3 и 2 и форми- 20 рующий окончательный результат— значение координат куба Кз (1: и), Устройство (фиг,1) содержит и вычислительных ячеек 1,1...1.п и решающий узел 2, На первый и второй входы вычислительных 25 ячеек подается код куба К>, на третий и четвертый входы — код куба К2, Каждая 1-я (I =1, и) вычислительная ячейка (фиг.2) содержит элементы И 3, 4 и 5, элемент ИЛИ 6, элемент И 7, элементы 30

ИЛИ-Н Е 8 и 9, элементы И 10 и 11 и элемент

ИЛИ 12, Каждая l-я (i = 1, и) ячейка (фиг,2) реализует систему логических функций:

f(i) = Е1() Г2(Ц И1() х2(фЬ(1) х1(1), . 35 х (i)= xI(i)х i; (1) уя(4) = Ф1(4) (й2 IlvX2 4))УЬ(Ц Щ ГХЧI)

Решающий узел 2 содержит и элементов ИЛИ 13.1, 13,2...13.п, обе группы элементов Запрет 14.1...14.п, 15.1...15.п и 40 мажоритарный элемент 16.

Решающий узел 2 вырабатывает на своих выходах окончательное значение координат куба Кз = К1хКг и реализует систему логических функций: 45 где у„ z(y„(1) y„(0) — обобщающий сигнал по всем п шинам уя(1) вычислительных яче- 55 ек 1.i.

Устройство работает следующим образом.

На первый и второй входы каждой 1-й (i — 1. и) вычислительной ячейки подается ксд куба К>, а на третий и четвертый — код куба

К2 в соответствии с табл,1, на выходах вычислительных ячеек вырабатываются предварительные значения координат куба Кз в соответствии с табл.3. Эти значения поступают на первый, второй, третий входы каждой 1-й группы входов решающего узла

2, при этом, если на третьих входах всех и групп входов решающего узла 2 суммарное количество сигналов y (i) = 1 больше одного, на выходе мажоритарного элемента 16 и, следовательно, на третьем выходе каждой

1-й группы выходов устройства появляется сигнал д gi) = 1, I = (1, и), Это в соответствии с табл,2 говорит о том, что х-произведение кубов К> и К2 пусто (О). Если же на третьих входах всех и групп входов решающего узла

2 появляется не больше одного сигнала

ye(i) = 1 (i = 1, n), то на выходах устройства формируется значение куба Кз = К1хК2, кодированное в соответствии с табл. 2.

Формула изобретения

Устройство реализации операции "/х/произведение и-мерных кубов", содержащее и вычислительных ячеек, где n— размерность куба, причем каждая из вычислительных ячеек содержит шесть двухвходовых элементов И, трехвходовый элемент

ИЛИ и двухвходовый элемент ИЛИ, причем выходы с первого по третий двухвходовых элементов И соединены с соответствующими входами трехвходового элемента ИЛИ, первый вход i-й вычислительной ячейки (I = 1, и) соединен с первыми входами первого, второго и шестого двухвходовых элементов И, второй вход первого двухвходового элемента И, первые входы третьего и пятого двухвходовых элементов И соединены с третьим входом i-й вычислительной ячейки, второй вход которой соединен с вторым входом третьего двухвходового элемента И и первым входом четвертого двухвходового элемента И, четвертый вход i-й вычислительной ячейки соединен с вторыми входами второго и четвертого двухвходовых элементов И, выходы пятого и шестого двухвходовых элементов И соединены с соответствующими входами двухвходового элемента ИЛИ, отл и ча ю щеес ятем.что, с целью повышения быстродействия и сокращения аппаратных затрат, в него введены решающий узел, содержащий и-входовый мажоритарный элемент, и двухвходовых элементов ИЛИ и две группы из и элементов ЗАПРЕТ каждая, причем первый вход I-й группы входов решающего узла.соединен с прямым входом 1-го элемента 3АПРЕТ второй группы, выход которого является первым выходом i-й группы выхолв решающего узла, втооой вход i-й группы

1656522 входов решающего узла соединен с первым входом I-ro двухвходового элемента ИЛИ, третий вход i-й группы входов решающего узла соединен с i-м входом мажоритарного элемента и вторым входом I-годвухвходово- 5 го элемента ИЛИ, выход которого соединен с прямым входом I-ro элемента ЗАПРЕТ первой группы, выход которого является вторым выходом I-й группы выходов решающего узла, выход мажоритарного элемен- 10 та соединен с инверсными входами всех элементов ЗАПРЕТ первой и второй групп и с третьими выходами всех групп выходов решающего узла, а в каждую вычислительную ячейку введены два двухвходовых эле- 15 мента ИЛ И-Н Е, причем в каждой вычислительной ячейке первый вход первого двухвходового элемента ИЛИ-НЕ соединен с первым входом вычислительной ячейки, второй вход которой соединен с вто- 20 рым входом первого двухвходового элемента ИЛИ-НЕ, первый вход второго двухвходового элемента ИЛИ-НЕ соединен с третьим входом вычислительной ячейки,четвертый вход которой соединен с вторым входом второго двухвходового элемента

ИЛИ-НЕ, выход которого и выход первого двухвходового элемента ИЛИ-НЕ соединены соответственно с вторыми входами пятого и шестого двухвходовых элементов И, выход трехвходового элемента ИЛИ соединен с первым выходом вычислительной ячейки, выход четвертого двухвходового элемента И соединен с вторым выходом вычислительной ячейки, выход двухвходового элемента ИЛИ соединен с третьим выходом-вычислительной ячейки, первый, второй и третий выходы i-й вычислительной ячейки соединены с первым, вторым и третьим входами 1-й группы входов решающего узла, первые, вторые и третьи выходы с первой по 1-ю групп которого являются разрядными выходами устройства, разрядными входами которого являются первые, вторые, третьи и четвертые входы с первой по и-ю ячейки.

1656522 (и Ел Лгу

Составитель В. Лях

Редактор Л. Веселовская Техред M.Ìîðãåíòàë Корректор И. Муска

Заказ 2052 Тираж 400 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб.. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101