Устройство для извлечения корня третьей степени

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Цель изобретения - расширение области применения за счет возможности извлекать корень степени больше трех. Устройство , содержащее триггеры 1, 3, 4, регистры мантиссы 13, 17, 19, 27, регистры порядка 6, 10, 11, блоки памяти 8, 9, 15, 28, умножитель 16, сумматор 18. за счет введения регистра 22 степени, элемента И 24, буферного регистра 25 и второго умножителя 26 позволяет реализовать режим извлечения корней произвольных степеней для чисел с плавающей запятой. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)я 6 06 F 7/552

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4671370/24 (22) 03.04.89 (46) 15.06.91. Бюл. М 22 (71) Ленинградский электротехнический институт им. B.È.Óëüÿíîâà (Ленина) (72) Е.А.Колесников, А.С.Просочкин и С.Ф,Свиньин (53) 681.325(088,8) (56) Авторское свидетельство СССР

М 883898, кл. 6 06 F 7/552, 1981.

Авторское свидетельство СССР

М 1288695, кл. G 06 F 17/552, 1987. (54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ

КОРНЯ ТРЕТЬЕЙ СТЕПЕНИ

Изобретение относится к вычислительной технике и может быть использовано для извлечения корня произвольной целой степени в вычислительных машинах и устройствах с обработкой данных в формате с плавающей запятой.

Цель изобретения — расширение области применения за счет возможности йзвлекать корень степени больше трех.

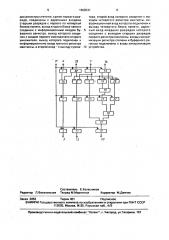

На чертеже представлена структурная схема устройства. Устройство содержит триггеры 1 — 3, вход 4. выход 5 знака устройства, первый регистр 6 порядка, вход 7 порядка устройства, первый 8 и второй 9 блоки памяти, второй 10 и третий 11 регистры порядка, выход 12 порядка, первый регистр 13 мантиссы, вход 14 мантиссы устройства, третий блок 15 памяти, первый умножитель

16, второй регистр 17 мантиссы, сумматор

18, третий регистр 19 мантиссы, выход 20 мантиссы устройства, вход 21 синхронизации устройства, регистр 22 степени, вход 23 степени устройства, элемент И 24, буферный

„„Я „„1656531 А1 (57) Изобретение относится к вычислительнойтехнике. Цельиэобретения-расширение области применения за счет возможности извлекать корень степени больше трех. Устройство, содержащее триггеры 1, 3, 4, регистры мантиссы 13, 17, 19, 27, регистры порядка 6. 10, 11, блоки памяти 8, 9, 15, 28, умножитель 16, сумматор 18, за счет введения регистра 22 степени, элемента И 24, буферного регистра 25 и второго умножителя 26 позволяет реализовать режим извлечения корней произвольных степеней для чисел с плавающей запятой. 1 ил, регистр 25, второй умножитель 26, четвертый регистр 27 мантиссы, четвертый блок 28 памяти.

Для вычисления функции вида (М. 2 ) используется соотношение (M 21 =M 2Р гдеM =2 1 (.М ;

P = )Р/N(;

М вЂ” мантисса;

Р— порядок;

}Р/N(— целая часть частного.

Функции )Р/й(и 2 1 (вычисляются прямым табличным способом.

Устройство работает следующим образом.

Подается первый тактирующий импульс с входа 21 синхронизации на входы синхронизации триггера 1, регистра 22 степени, первого регистра 6 порядка и первого регистра 13 мантиссь . По этому синхроимпульсу в триггер 1 заносится код знака с входа 4 ввода знака, регистр 6 порядка принимает код порядка с входа 7 ввода порядка, в регистр 13 мантиссы заносится код мантиссы

1656531

10

20 с входа 14 ввода мантиссы, регистр 22 степени принимает код степени с входа 23 ввода кода степени, Если старший разряд регистра 22 кода степени равен единице, то на информационный вход триггера 2 поступает код знака с выхода триггера 1, если нулю, то на информационном входе триггера 2 появляется сигнал логического нуля. Остальные разряды кода иэ регистра 22 кода степени поступают на адресный вход старших разрядов блоков В, 9, 15 и 26 памяти и позволяют выбирать из них только те значения, которые относятся к вычислению корней степени. Иэ блока 8 памяти считывается значение )Р/N(, которое поступает на информационный вход второго регистра 10 порядка. Из блока 9 памяти считывается значение 2 " (, которое поступает на информационный вход буферного регистра

25. На адресный вход младших разрядов блока 15 памяти подаются старшие разряды с первого регистра 13 мантиссы. Из блока

15 памяти считывается значение коэффициента наклона функции М Hà 1-м участке, где I = 1...1, которое умножается умножителем 16 на величину (М вЂ” M )/n, определяемую кодом младших разрядов первого регистра 13 мантиссы, результат поступает на информационный вход второго регистра

17 мантиссы. На адресный вход младших разрядов блока 28 памяти подаются старшие разряды первого регистра 13 мантиссы. Из блока 28 памяти считывается значение М, где М вЂ” значение мантиссы в узловой точке. Результат поступает на информационный вход четвертого регистра 27 мантиссы.

По второму тактирующему импульсу, поступившему по входу 21 синхронизации, производится запись во второй триггер 2, второй регистр 10 порядка, буферный регистр 25, второй регистр 17 мантиссы и четвертый регистр 27 мантиссы кодов, поступивших на их информационные входы.

Содержимое второго 17 и четвертого 27 регистров мантиссы складывается на сумматоре

18, а результат умножается умножителем 26 на код из буферного регистра 25. Таким образом, на информационный вход третьего регистра 19 мантиссы поступает следующее выражение: (° (М К ) где К - коэффициент наклона функции М на I-и участке ее аппроксимации.

По первому тактирующему импульсу следующего цикла s триггер 3 записывается

55 значение иэ триггера 2, третий регистр 11 порядка принимает значение из второго регистра 10 порядка, а третий регистр 19 мантиссы — код со своего информационного входа. На вход 5 вывода знака поступает код знака результата иэ триггера 3, на вход 12 выхода порядка — код порядка из третьего регистра 11 порядка, на вход 20 выхода мантиссы — код мантиссы результата иэ третьего регистра 19 мантиссы.

Формула изобретения

Устройство для извлечения корня третьей степени, содержащее с первого по третий триггеры, четыре регистра мантиссы, умножитель, с первого по третий регистры порядка, сумматор, четыре блока памяти, причем информационный вход первого триггера соединен с входом знака устройства, выход второго триггера соединен с информационным входом третьего триггера, выход которого является выходом знака устройства, информационный вход первого регистра порядка подключен к входу порядка устройства, а выход — к адресным входам младших разрядов первого и второго блоков памяти, выход первого блока памяти соединен с информационным входом второго регистра порядка, выход которого соединен с информационным входом третьего регистра порядка, выход которого является выходом порядка устройства, информационный вход первого регистра мантиссы подключен к входу мантиссы устройства, а выход старших разрядов — к адресным входам младших разрядов третьего блока памяти, выход которого соединен с входом первого сомножителя первого умножителя, вход второго сомножителя которого соединен с выходом младших разрядов первого регистра мантиссы, а выход — с информационным входом второго регистра мантиссы, выход которого соединен с первым входом сумматора; выход третьего регистра мантиссы является выходом мантиссы устройства, входы синхронизации с первого по третий триггеров, первого, второго и третьего регистров порядка, с первого по четвертый регистров мантиссы соединены с входом синхронизации устройства. о т л и ч а ю щ е ес я тем, что, с целью расширения области применения эа счет воэможности извлекать корень степени больше трех, в него введены регистр степени, буферный регистр, элемент И и второй умножитель, причем информационный вход регистра степени соединен с входом степени устройства, а выход первого разряда — с первым входом элемента И, второй вход которого подключен к выходу первого триггера, а выход — к информационному входу второго триггера, выходы раэря1656531

20

Составитель Е.Колесников

Редактор Л.Веселовская Техред М.Моргентал Корректор М.Демчик

Заказ 2053 Тираж 401 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35. Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101 дов регистра степени, кроме первого разряда, соединены с адресными входами старших разрядов с первого по четвертый блоков памяти, выход второго блока памяти соединен с информационным входом буферного регистра, выход которого соединен с входом первого сомножителя второго умножителя, выход которого floäêëþ÷åí к информационному входу третьего регистра мантиссы, а второй вход — к выходу сумматора, второй вход которого соединен с выходом четвертого регистра мантиссы, информационный вход которого подключен к выходу четвертого блока памяти, адрес5 ный вход младших разрядов которого соединен с выходом старших разрядов первого регистра мантиссы, входы синхронизации регистра степени и буферного регистра подключены к входу синхронизации

10 устройства.