Система прямого доступа к общей памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для управления коллективным доступом абонентов к общей памяти. Цель изобретения - повышение быстродействия системы путем мультиплексирования прямого доступа к общей памяти. Система прямого доступа к общей памяти содержит магистраль 1, блок 2 захвата магистрали, регистр 4 данных, блок 6 управления, буферную память 14. общую память 7, регистр 11 текущего адреса , регистр 12 конечного адреса, схему 13 сравнения, сумматор 10. За счет применения мультиплексоров информации и адреса организуется запись в память не только массивов информации абонентов, но и текущего и конечного адресов считываемого или записываемого слова массива для каждого абонента. 2 з.п. ф-лы, 5 ил. К абонента

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (!9у ((() (siis G 06 F 12/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

f абонентаи

01 (Я

0с

Сл

4ь (21) 4497648/24 (22) 24,10.88 (46) 15.06.91. Бюл. М 22 (72) В.А.Мансуров, Н.К.Сумин, А.Е.Колчин и А.В.Юровских (53) 681.325.5(088.8)

{56) Шевкопляс Б.В. Микропроцессорные структуры, M. Радио и связь, 1986, с. 90. (54) СИСТЕМА ПРЯМОГО ДОСТУПА К ОБЩЕЙ ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано для управления коллективным доступом абонентов к общей памяти. Цель изобретения —. повышение быстродействия системы путем мультиплексирования прямогодоступа к общей памяти. Система прямого доступа к общей памяти содержит магистраль 1, блок 2 захвата магистрали, регистр 4 данных. блок 6 управления, буферную память 14, общую память 7, регистр 11 текущего адреса, регистр 12 конечного адреса, схему

13 сравнения, сумматор 10. За счет применения мультиплексоров информации и адреса организуется запись в память не только массивов информации абонентов, но и текущего и конечного адресов считываемого или записываемого слова массива для каждого абонента. 2 з,п. ф-лы, 5 ил.

1656541

Изобретение относится к вычислительной технике и может быть использовано для построения систем коллективного доступа к общей памяти.

Цель изобретения — повышение быстродействия системы путем мультиплексирования прямого доступа к общей памяти.

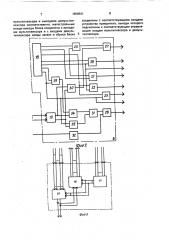

На фиг, 1 изображена структурная схе-! ма системы прямого доступа к общей памяти; на фиг. 2 — то же, блока управления; на фиг. 3 — то же, блока захвата магистрали; на фиг. 4, 5 — временные диаграммы работы системы.

Система прямого доступа к общей памя,ти (фиг. 1) содержит магистраль 1, блок 2 захвата магистрали с и входами линий связи ,с абонентами 3 (и — количество абонентов), регистр данных, состоящий из регистра 4 ,, информации и регистра 5 адреса, блок 6 ,управления, общую память 7, мультиплек, сор 8 информации, мультиплексор 9 адреса, сумматор 10, регистр 11 текущего адреса, . регистр 12 конечного адреса, схему 13 сравнения, буферную память 14.

Блок захвата магистрали (фиг.3) содержитдемультиплексор 15, мультиплекстор 16 .и устройство 17 приоритета.

Блок управления (фиг. 2) содержит формирователь 18 синхроимпульсов, дешифратор 19, семь логических элементов И 20 — 26, пять логических элементов ИЛИ 27 — 31, элемент НЕ 32.

Система работает следующим образом.

ЭВМ осуществляет настройку системы доступа к общей памяти, для чего через ма. гистраль производит запись начального и конечного адресов для всех абонентов в память общего доступа, причем начальный (текущий) адрес абонента записывается по . адресу абонента, который является порядковым номером абонента, а конечный адрес- по адресу, младшие разряды которого равны разрядам адреса абонента. Старший

l-й разряд устанавливается в "1" блоком управления.

Для прямого доступа к общей памяти абонент посылает через блок захвата магистрали свой адрес, в старших незначащих разрядах которого задаются признаки рода работы для блока 6 управления (считывание, запись) и при необходимости — информация для записи, Адрес и информация из магистрали 1 записываются на регистры 4 информации и

5 адреса.

На фиг. 4 изображена временная диаграмма работы устройства управления, на фиг. 5 — временная диаграмма сигналов блока формирователя импульсов синхронизации, Блок 6 управления организует доступ к общей памяти 7 за 4 такта.

5 В первом такте из памяти 7 по адресу абонента считывается текущий (начальный) адрес, при этом I-й управляющий вход второй группы мультиплексора 9 адреса блоком управления устанавливается в "0". Этот адрес записывается на регистр 11 текущего адреса.

Во втором такте из памяти считывается конечный адрес по тому же адресу, только в

I-м разряде блока 6 управления устанавливается "1". Конечный адрес записывается в регистр 12 конечного адреса, В случае совпадения текущего и конечного адресов схема сравнения выдает управляющий сигнал — признак конца массива — в блок управления, который прекращает обмен с абонентом.

В третьем такте по адресу абонента в память 7 записывается модифицированный на единицу текущий адрес, KQTopblA снимается с выходов сумматора 10 через мультиплексор 8 информации.

В четвертом такте по текущему адресу, который снимается с регистра 11 текущего

30 адреса, через мультиплексор 9 адреса производится считывание информации из памяти 7, которая переписывается в буферную память и передается в магистраль, либо запись информации иэ регистра 4 информации. Режим записи или считывания задается блоку управления информацией в старших незначащих разрядах посылаемого абонентом адресного слова. После получения очередного слова абонент либо

40 подтверждает занятие магистрали, либо освобождает ее для работы других абонентов или ЭВМ.

Система обеспечивает прямой доступ любого числа абонентов к общей памяти, 45 при этом объем оборудования практически не зависит от числа абонентов (от него зависит только объем памяти общего доступа).

Система позволяет достичь повышения быстродействия обслуживания любого ко50 личества абонентов за счет организации хранения адресов памяти в памяти общего доступа.

Формула изобретения

1. Система прямого доступа к общей

55 памяти, содержащая блок захвата магистрали, регистр данных, блок управления, .регистр текущего адреса, регистр конечного адреса, схему сравнения, сумматор и буферную память, причем вход регистра данных

1656541 через магистраль подключен к магистральным входам-выходам блока захвата магистрали, вход признака конца массива блока управления подключен к одноименному выходу схемы сравнения, первый вход которой соединен с выходом регистра конечного адреса, а второй вход и вход сумматора соединены с выходом регистра текущего адреса, выходы управления данными, буферной памятью, текущим адресом блока управления соединены с соответствующими входами регистра данных, буферной памяти и регистра текущего адреса соответственно, отличающаяся тем, что, с целью повышения быстродействия системы путем мультиплексирования прямого доступа к общей памяти, в нее введены мультиплексор информации и мультиплексор адреса, причем первый и второй входы мультиплексора информации соединены с выходом сумматора и с информационным выходом регистра данных соответственно, а выход является выходом системы для подключения к информационному входу общей памяти, первый адресный вход мультиплексора адреса подключен к выходу регистра текущего адреса, а второй адресный вход и адресный вход блока управления подключены к адресному выходу регистра данных, выход мультиплексора адреса является выходом системы для подключения к адресному входу общей памяти, входы регистра текущего адреса, регистра конечного адреса и буферной памяти образуют вход системы для подключения к выходу общей памяти, выход буферной памяти через магистраль.подключен к магистральным входам — выходам блока захвата магистрали, абонентские входы и выходы которого являются входами и выходами связи с абонентами системы, а входы заявок и сброса являются входами заявок и сброса от абонентов системы, управляющий вход и вход управления адресом мультиплексора адреса, вход управления информацией мультиплексора информации, вход управления конечным адресом регистра конечного адреса соединены с соответствующими выходами блока управления, выход управления памятью которого является входом управления общей памяти.

2. Система по и. 1, отличающаяся тем, что блок управления содержит формирователь синхроимпульсов, дешифратор, с первого по седьмой элементы И, с первого по пятый элементы ИЛИ, элемент НЕ, причем первый выход формирователя синхроимпульсов соединен с первым входом

nepsoro элемента И, выход которого подключен к первому входу первого элемента

ИЛИ, выход которого соединен с выходом уп ра аления данными блока управления, второй выход формирователя подключен к первому

5 входу второго элемента И, выход которого соединен с выходом управления текущим адресом блока управления, третий выход формирователя синхроимпульсов подключен к первому входу третьего элемента И, выход которого подключен к выходу управления конечным адресом блока управления и к первому входу четвертого элемента И, выход которого соединен с выходом управления-,буфером блока управления, четвертый выход формирователя синхроимпульсов подключен к второму входу первого элемента И, к первому входу второго элемента

ИЛИ, выход которого соединен с выходом управления адресом блока управления и к второму входу второго элемента И, пятый выход формирователя синхроимпульсов соединен с вторым входом второго элемента

ИЛИ, с управляющим выходом блока управления и с вторым входом третьего элемента

И, шестой выход формирователя синхроимпульсов соединен с первым входом третьего элемента ИЛИ, выход которого подключен к второму входу пятого элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, выход которого подключен к первому входу седьмого элемента И, выход которого соединен с выходом управления памятью блока управления, седьмой выход формирователя синхроимпульсов соединен с вторым входом третьего элемента ИЛИ, с вторым входом четвертого элемента И, с выходом управления информацией блока управления и с первым входом шестого эле40 мента И, выход которого соединен с вторым входом пятого элемента ИЛИ, адресный вход блока управления является входом дгшифратора, первый выход которого соединен с первым входом четвертого элемента

45 ИЛИ, выход которого подключен к второму входу гервого элемента ИЛИ и к первому входу пятого элемента И, второй выход дешифратора соединен с вторым входом четвертого элемента ИЛИ и с вторым входом

50 шестого элемента И, выход которого соединен с вторым входом пятого элемента ИЛИ, вход признака конца массива блока управления через элемент НЕ соединен с вторым входом седьмого элемента И.

3. Система по и. 1, отличающаяся тем, что блок захвата магистрали содержит демультиплексор, мультиплексор и устройство приоритета, причем абонентские входы и выходы блока являются входами

1656541 мультиплексора и выходами демультиплексора соответственно, магистральные входы-выходы блока соединены с выходами мультиплексора и с входами демультиплексора, входы заявок и сброса блока соединены с соответствующими входами устройства приоритета, выходы которого подключены к соответствующим управляющим входам мультиплексора и демуль5 типлексора.

1656541

5 т. соз

С07 - - Ф. 5

Составитель В.Сычев

Редактор А.Маковская Техред М.Моргентал Корректор С.Черни

Заказ 2053 Тираж 404 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101