N-разрядный буферный регистр

Иллюстрации

Показать всеРеферат

Изобретение относится к информационно-измерительной и вычислительной технике и может быть использовано для записи и хранения информации Р интерфейсных буферных устройствах Цель изобретения - упрощение регистра, Это достигается за счет сокращения схемы управления до двух логических элементов, в его D-триггерах цепи передачи информации и обратной связи выполнены коммутируемыми, для чего в каждый из триггеров в цепь передачи информации введен элемент И 4, а в цепь обратной связи - ключевой элемент 5, выход которого управляет элементом И 4. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 G 11 С 19/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4683262/24 (22) 10.03,89 (46) 15.06.91. Бюл. и 22 . (71) Азербайджанский институт нефти и химии им. M.ÀýèýáåêîBà (72) М.П. Грановский, А,А.Мамедов и И.П.Сколейкий (53) 681.327.66 (088,8) (56) Шило В.Л. Популярные цифровые микросхемы. — M. Радио и связь, 1987, с, 67, рис.1.45.

Аналоговые и цифровые интегральные микросхемы. — М.: Радио и связь, 1984, с.210, рис.422.

Изобретение относится к и нформационно-измерительной и вычислительной технике и может быть использовано для записи и хранения цифровой информации в интерфейсных буферных устройствах.

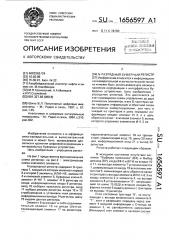

Цель изобретения — упрощение регистра, На фиг.1 представлена функциональная схема регистра; на фиг.2 — электрическая схема ключевого элемента.

N-разрядный регистр содержит D-триггеры 1, каждый из которых включает первый

2 и второй 3 элементы, ИЛИ вЂ” НЕ. элемент И . 4 и ключевой элемент 5, буферные ключи 6, элемент И вЂ” HE 7. элемент И 8 регистра на входе, информационные входы 9 регистра, вход 10 выборки кристалла регистра, вход

11 выбора режима регистра, входы 12 и 13 стробирования и установки нуля регистра, информационные выходы 14 регистра, шину

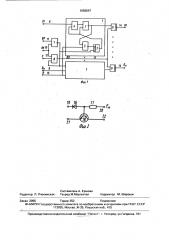

15 выдачи данных регистра, Элемент 5 включает в себя ограничительный элемент 16 на диоде Шоттки, токозадающий элемент 17 на резисторе, . Ы 1656597 А1 (54) N-РАЗРЯДНЫЙ БУФЕРНЫЙ РЕГИСТР (57) Изобретение относится к информационно-измерительной и вычислительной технике и может быть использовано для записи и хранения информации в интерфейсных буферных устройствах. Цель изобретения— упрощение регистра. Это достигается за счет сокращения схемы управления до двух логических элементов, в его D-триггерах цепи передачи информации и обратной связи выполнены коммутируемыми, для чего в каждый из триггеров в цепь передачи информации введен элемент И 4, а в цепь обратной связи — ключевой элемент 5, выход которого управляет элементом И 4, 2 ил. переключательный элемент 18 на транзисторе, управляющий вход 19, шину 20 питания, информационный вход 21 и выход 22 регистра.

Регистр работает следующим образом.

В исходном состоянии отсутствие сигналов "Выборка кристалла" (ВК) и Выбор 0 режима (ВР), когда ВК-0 и ВР-0 на входах 10 (Л и 11, на выходе элемента 7 устанавливается О

1, разрешающая по входу 19 включение эле- (у ментов 5, замыкающих цепь обратной связи в триггерах с выхода элемента ИЛИ вЂ” НЕ 3 на входы элемента 2 и элемента 4, на выходе элемента 8 устанавливается "0", запрещающий по шине 15 (ВД) и вторым входам буферных ключей 6 выдачу данных с триггеров на выходы 14 регистра.

Если состояние триггера "0", то поступающая с выхода включенного элемента 5

"1", хотя и разрешает передачу через элемент 4 входной информации с D-входа на элемент 2, но одновременно удерживает (блокирует) этот элемент в нулевом состоя1656597 нии, поэтому состояние триггера является устойчивым.

Если состояние триггера "1", то поступающий с выхода элемента 5 "0" запрещает (блокирует) по второму входу элемента 4 поступление через него информации на элемент 2, поэтому и в этом случае состояние триггера является устойчивым, Следовательно, при В К-О (В Р-Х) включена обратная связь в триггерах, регистр находится. в режиме хранения записанной информации, что можно отобразить записью:

ХР=ВК

Выдача информации из регистра через ключи происходит при подаче на входы 10 и

12 единичных сигналов "Выборка кристалла" и "Строб считывания" в отсутствие сиг., нала "Выбор режима" на входе 17, т.е. при ВК=1, С=1 и БР=О, В этом случае на выходе элемента 7 сохраняется "1" (так как ВР=-О)., которая под,держивает элемент 5 во включенном сост 3янии, а на выходе элемента Я (и шине ВД) устанавливается "1", так как на всех его входах присутствуют "1". Поэтому буферные ключи б открываются и информация: триггеров поступает на выходы 14 регистра.

Следовательно, выдача данных с perucTp3 ooMcbiBBeTcB формулой:

ВД=ВК; С р ВР.

Запись информации в регистр происходит при подаче на входы 10 и 11 сигналов

ВК=1 и ВР=1 (C=X), При этом срабатывает элемент 7 и на его выходе устанавливается

"0", который выключает элемент 5 по входу

19 элемента 5 во всех триггерах и блокирует через элемент 8 по шине 15 и управляющим входам буферных ключей 6 поступление через них информации с триггеров на выходы регистра.

Элемент 18 закрывается (фиг,2) и на выходе последнего прекращает действовать какой-либо потенциал (разрыв цепи обратной связи), нулевой или единичный, что соответствует подаче разрешения на входы элементов 4 и 2 и их деблокирование. Поэтому сигнал 21, воздействуя через элемент

4. устанавливает элементы и в соответствии со своим значением в состояние "01" или

"10", т.е. в триггер передается входная информация, После окончания сигнала ВР по его отрицательному фронту элемент 7 переходит в состояние "1" при котором включается элемент 5 (закрывается диод 16

Шоттки) и на его выходе появляется "0" или

"1", поступающие на входы элементов 4 и 2, т.е. включится цепь обратной связи и триг15

55 гере, его состояние фиксируется и изменения информации на входе не могут это состояние изменить, Таким образом, буферный регистр имеет более простую схему управления, обеспечивающую многорежимность работы, а его

D-триггеры с коммутируемыми цепями передачи информации и обратной связи имеют более высокое быстродействие, что обеспечивает высокое быстродействие регистра в целом.

Формула изобретения

К-разрядный буферный регистр (M=1,n), содержащий элемент И вЂ” НЕ, первый вход которого является входом выборки кристалла регистра, D-триггеры, буферные ключи, выходы которых являются информационными выходами регистра, информационные входы О-триггеров являются информационными входами регистра, выходы О-триггеров подключены соответственно к информационным входам соответствующих буферных ключей, управляющие входы которых обьединены и подключены к шине выдачи данных регистра. каждый D-триггер

N-ro разряда выполнен на двух элементах

ИЛИ-НЕ, причем выход первого элемента

ИЛИ-HE подключен к первому входу второго элемента ИЛИ-НЕ и информационному входу буферного ключа этого же разряда, отличающийся тем, что, с целью упрощения регистра, в него введен элемент

И, а в каждый N-разряд регистра элемент И и ключевой элемент, выход которого подключен к первым входам элемента И и первого элемента ИЛИ вЂ” НЕ этого же разряда. второй вход nepeoro элемента ИЛИ-НЕ подключен к выходу элемента И того же разряда, второй вход которого подключен к ийформационному входу 0-триггера того же. разряда, выход второго элемента ИЛИ-HE подключен к информационному входу ключевого элемента того же разряда,управляющие входы ключевых элементов 0триггеров всех разрядов объединены и подключены к выход элемента И-HE и первому входу элемента И регистра, второй вход которого является входом стробирования регистра, а третий вход подключен к входу выборки кристалла регистра, второй. вход элемента И вЂ” НЕ является входом выборки режима регистра, вторые входы вторых элементов ИЛИ-HE всех разрядов объединены и являются входом установки нуля регистра, шина выдачи данных регистра подключена к выходу элемента И регистра, 1656597

1У 1б

Составитель А. Ершова

Редактор Л. Пчолинская Техред M.Ìîðãåíòàë Корректор М. Шароши

Заказ 2055 Тираж 352 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101