Двухтактный усилитель мощности

Иллюстрации

Показать всеРеферат

СО1ОЗ СО13Г 1СVÈÕ

С011ИАПИСТИЧЕСКИХ

ГГ.=Г,ПУГЭЛИК

s Н 03 F 3/26

VCC",ДЛ111TE3tННЫй KOML11Fr

Г1О иэовг е 1е ниям и Отк1? ытиям 11?И 1V1П С .,Р,, "Ь?, °

?1-1 с -? 1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКOMУ СВИДЕТЕЛЬСТВУ (21) 4620647/09 (22) 15 12 88 (46) 15,06,91, Ьюл. N 22 (71) Куйбышевскии авиационный институт им, акад. С. П. Королева (72) В..И. Иванченко, С. Б. Мирошниченко, С. В. Мурзина и В. А. Абакумов (53) 621.375 026(088.8) (56) Патент США M 3319175, кл. 330-22, 1967, (54)ДВУХТАКТНЫЙ УСИЛИТЕЛЬ МОЩНОСТИ (57) Изобретение относится к электронике.

Цель изобретения — увеличение выходного напряжения, Двухтактный усилитель мощносги содержит два плеча нэ транзисторах, нагрузку, источник питания с заземленной

Изобретение относится к электронике и предназначено для усиления электрических сигналов.

Цель изобретения — увеличение выходного напряжения.

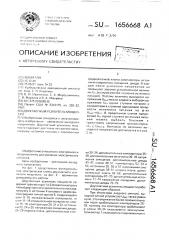

На фиг, 1 представлена функциональная электрическая схема двухтактного усилителя мощности: на фиг. 2 — временные диаграммы его работы.

Двухтактный усилитель мощности содержит транзисторы 1 и 2 (первого и второго плеча) двухтактного усилительного каскада, нагрузку 3, источник 4 питания с заземленной средней точкой-шиной 5, содержащей и шин 6-10 положительной полярности, m шин 11-15 отрицательной полярности, ключи 16 -19. компараторы 20, 21 и 22, источниvol 23, 24 и 25 напряжения смещения, диоды

26-29 первого плеча, дополнительные клю„„Я2„„ 1656668 А I средней точкой, ключи, компэраторы, источники напряжения смещения, диоды. В каждом плече усилителя нап ряжение не превышает заранее установленной величины Ucc? (в случае равных ступеней источника питания). Поэтому величину выходного напряжения 0»> можно задавать выбором напряжения Uc? одной ступени питания и количеством и ступеней одинаковой полярности источника питания по ф-ле

0эых=-п0ст В предельном случае напряжение 0 одной ступени источника питания можно выбрать близким к граничному напряжению транзисторов:

Ос? < U?aorp Выигрыш по величине выходного напряжения достигается в и раз.

2 ил. чи 30 — 34, дополнительные компараторы 3538, дополнительные источники 39- 42 напряжения смещения, дополнительные диоды

43-47, ключи 48-51, компарэторы 52, 53 и

54, источники 55, 56 и 57 напряжения смещения, диоды 58-61 второго плеча, дополнительные ключи 62 — 66, дополнительные компараторы 67-70, дополнительные источники 71 — 74 напряжения смещения. дополнительные диоды 75 — 79.

Двухтактный усилитель мощности работает следующим образом, При отсутствии входного сигнала, выходной сигнал устройства UB X также равен нулю. Это напряжение более положительно, чем порог срабатывания компараторов 3538, поэтому эти компараторы срабатывают и ключи 30 —,34 оказываются замкнутыми, Транзистор 1 оказывается подключенным к

1656668 шине 6 источника 4 питания, Кроме того, нулевое выходное напряжение усилителя меньше порога срабатывания компараторов 70. 67, 68, 69 и они замыкают ключи 66, 62, 64, 65. Транзистор 2 оказывается подключенным к шине 11 источника 4 питания.

Таким образом, напряжение на транзисторе 1 определяется разностью потенциалов шин 6 и 5 и равно U<.». Напряжение на транзисторе 2 равно разности потенциалов шин 11 и 5 и равно — Ucrg, При подаче входного сигнала положительной полярности, транзистор 2 закрывается, транзистор 1 открывается и проводит ток в нагрузку. На нагрузке появляется напряжение положительной полярности (фиг, 2а), напряжение нэ транзисторе 1 (фиг. 2б) убывает, на транэисгоре 2 по модулю возрастает (фиг. 2в).

Когда напряжение на нагрузке превысит порог срабатывания компаратора 70 (момент времени t,, фиг. 2). он выключается и рэз1 мыкает ключ 66. Транзистор 2 оказывается подключенным < lшi<и н<е e 5 5 и <с-,очникл питания и модуль напряжения на нем скачком уменьшлегся. При длльнейшем увеличении выходного напряжения в момент времени tt, когда напряжение Uf<$«(превысит порог срабатывания компарэтора 22; он включается и злмыкаег ключ 19. Транзистор 1 оказывается подключенным к шине 7 источника питания и напряжение на нем скачком воэрэстэет.

При превышении выходным сигналом лоро э срабатывания компэратора 69 он

Bb«

1 источника питания в момент. времени t < и модуль «лг<ряжения нл нем ска <ком уменьшлеtcч

В дальнейшем при увеличении выходного сигнала нл транзистор 1 подается напряжение третьей ступени источника питлния положительной полярности и напряжение нл нем скачком возрастает в Мо мент времени ty. При превышении выходнь<м нлпряжением порога срабатывания комплрлторл 68 он выключается и размыкает кл<оч 64. Транзистор 2 оказывается

1 подключенным в момент времени t 2 к шине

7 и модуль напряжения на нем скачком уменьшается.

В дальнейшем при увеличении выходньго напряжения процессы в схеме двухтактного усилителя мощности протекают аналогично.

При превышении порога срабатывания

KOMllBP3TOP3 20 (<.Бает(р-1) UcM, фИГ. 2д), ОН срабатывает и замыкает ключ 16. При этом в момент времени тз транзиСтор 1 подклю5

55 чается к шине 10 и напряжение на нем скачком увеличивается, При превышении выходным напряжением порога срабатывания компаратора 67 он выключается и размыкает ключ 62. При этом в момент времени t з транзистор 2

1 оказывается подключенным к шине 9 источника питания и напряжение на нем скачком уменьшается.

При уменьшении выходного напряжения ниже порога срабатывания компаратора 67 он выключается и замыкает ключ 62.

Транзистор 2 оказывается подключенным к шине 8 в момент времени t 4 и модуль на1 пряжения на нем скачком увеличивается.

В момент времени t4, при уменьшении выходйого напряжения ниже порога срабатывания компаратора 20, он выключается и размыкает ключ 16. Транзистор 1 подключается к шине 9 и напряжение на нем скачком уменьшится. Далее, при уменьшении выходного напряжения процессы в схеме протекают аналогично. При уменьшении выходного напряжения ниже порога срэбатывэния комплратора 68 он включается в момент времени t 5 и замыкает ключ 64.

Транзистор 2 подключается к шине 6 и модуль напряжения на нем скачком увеличится. В дальнейшем при уменьшении выходного напряжения транзистор 1 подключается к третьей ступени напряжения питания положительной полярности и напряжение на нем скачком уменьшается в момент времени tq.

При уменьшении выходного напряжения ниже порога срабатывания компараторэ 69 он включлется и замыкает ключ 65 в

1 момент времени t p. При этом транзистор 2 подключается к шине 5 и модуль напряжения на нем скачком увеличивается, Затем при уменьшении выходного напряжения ниже порога срабатывания компаратора 22 он выключается и размыкает ключ 19 в момент времени t<;. При этом транзистор 1 подключается к шине 6 и напряжение на нем скачком уменьшается.

При уменьшении выходного напряжения ниже порога срабатывания компаратора 70 он включается и замыкает ключ 66 в

1 момент времени t 7. В этот момент транзистор 2 подключается к шине 11 и модуль напряжения на нем скачком увеличивается.

При уменьшении выходного напряжения ниже порога срабатывания компаратора 35 он выключается и размыкает ключ 30 в момент времени тт, При этом транзистор 1 подключается к шине 5 и напряжение на нем скачком уменьшается.

При уменьшении выходного напряжения ниже порога срабатывания комплраторэ 52 он включается и замыкает ключ 48, <

При этом в момен< времени t я транзистор

2 подключается >. шине 12 и модуль напряжения на нем скачком увеличивается. При уменьшении выходного напряжения ниже поро а сраба<ывания компарэтора 36 он выключается и размыкает ключ 31 в момент времени t<<. При этом транзистор 1 подключается к шине 11 и напряжение на нем скачком уменьшается.

Далее при уменьшении выходного напряжения транзистор 2 подключается к третьей ступени напряжения питания отрицательной полярности, модуль напряжения на нем скачком увеличивается в момент времени t g. При уменьшении выходного на1 пряжения ниже порога срабатывания компаратора 37 он выключается и размыкает ключ 32 в момент времени tg. Транзистор

1 при этом оказывается подключенным к шине 12 и напряжение на нем скачком уменьшается.

Далее при уменьшении выходного напряжения, процессы в схеме усилителя мощности протекают аналогично.

При уменьшении выходного напряжения ниже порога срабатывания компаратора 54 он включается и замыкает ключ 51 в

< момент времени t

2 подключается к шине 15 и модуль напряжения на нем скачком увеличивается. При уменьшении выходного напряжения ниже порога срабатывания компэратора 38 он выключается и рэзмь.кает ключ 34. При этом в момент времени t

Далее выходное напряжение устройства достигает своего максимума отрицательной полярности и начинает увеличиваться, При увеличении выходного напряжения выше порога срабатывания компэратора 38 он включается и замыкает ключ 34 в момент времени т< <. При этом транзистор 1 подключается к шине 13 и напряжение на нем скачком увеличивается. При увеличении выходного напряжения выше порога срабатывания компаратора 54 он выключается и размыкает ключ 51. При этом в момент времени t « транзистор 2 подключается к шине

14 и модуль напряжения на нем скачком уменьшается.

В дальнейшем при увеличении выходного сигнала устройства процессы в схеме протекают аналогично.

При превышении выходным сигналом порога срабатывания компаратора 37 он срабатывает и замыкает ключ 32 в момент времени t<и нэ«ря+.

5 питания отрица<ельной п«ляр><ос<и п мо

1 мент врЕмени < < и модуль нэ«ряхк ><ич ><;< нем скачком увеличивается

Затем при превыше><ии выход«ым сиг налом порога срабатывания компараторэ 38

10 он включается и замыкает ключ 31, В зго> момент времени <<з трэнзистор 1 пор«пе«;;ется к шине 5 и напряжение нэ нем скачком увеличивается. При превышении выходным сигналом порога срабатывания компэрато

15 рэ 52 он выключается и рэзмь<кэе< ключ 48.

В этот момент времени t <з транзистор 2 подключается к шине 11 и модуль ><апряжения на нем скачком уменьшае<ся.

При превышении выходным сигналом

20 порога срабатывания компэраторэ 35 он включается и замыкает ключ 30. В этот момент времени t<4 транзистор 1 подключается к шине б и напряжение на нем скачком возрастает.

25 Таким образом, напряжение нэ каждом плече устройства не превышает заранее установленной величины (<..<< <) в слу«ае равных ступеней источника питания). Поэтому величину выходного напряжения устройства

30 можно задавать выбором напряжения од ной ступени питания <3„< и коли <еством ступеней одинаковой полярности источника питания п;

0«><х=п«<с<.

35 В предельном случае напряжение одной ступени источника питания можно выбрать близким N граничному напряжению транзисторов: О,< < Li„„<р

Таким образом, в предложенном усили40 теле получается выигрыш по величине выходного напряжения в и раз по сравнению с известными устройствами.

Формула изобретения

Двухтактный усилитель мощности, со45 держащий двухтактный усилительный каскад и источник питания со средней точкой, имеющий и шин положительной полярности напряжения и m шин отрицательнои полярности напряжения, где m=n, а также (n-1)

50 диодов, ключей, кî>ëпэрэторов исто;Hèков напряжения смещения, причем первый вывод каждого диода соединен с выводом питания транзистора первого пле <а с двухтактного усилительного каскада, вывод

55 каждого i-го диода, где i=1, 2, ..., n-1, кроме первого, соединен с входом i-го ключа, выход которого подключен к (i+1)-й шине положительной полярности напряжения, первый вход 1-го компаратора соединен с первым выводом i-го источника напряжения смещения, второй вывод которого соединен с < й

16%668 шиной попожигепьной полярности напря.кения. вт, рой вход каждого компаратора соединен с выходом двухтактного усилительного каскада, и (m-1) диодов, ключей, компараторов, источников напряжения смещения, причем первый вывод j-ro диода, где j-1, 2, ..., m-1, кроме первого, соединен с выходом j-го ключа, выход которого подключен к () 1)-й шине отрицательной полярности напряжения, второй вывод каждого диода соединен с выводом питания транзисгори второго плеча двухтактного усилительного каскада, первый вход каждого компаратора соединен с вторым выводом

j-ro источника напряжения смещения, первый вывод которого соединен с J-й шиной отрицательной полярности напряжения, а выход каждого l-го компаратора соединен с управляющим входом каждого 1-го ключа, выход каждого J-го компаратора соединен с управляющим входом каждого J-го ключа соответственно, отличающийся тем, что, с цепью увеличения выходно о напряжения, в него введено m дополнительных диодов, ключей, компараторов. источников напряwåHèÿ смещения, причем первый вывод каждого дополнительного диода соединен с выводом питания транзистора первого плеча двухтактного усилительного каскада, второй вывод k-го дополнительного диода, где

k=-1, 2, ..., m, кром m-го, соединен с входом (k > 1)-ro дополнитег ьного ключа, выход которого соединен с (>-1)-й шиной отрицательной полярности напряжения, второй вывод

m-го дополнительного диода соединен c (m1)-и шиной отрицательной полярности напряжения, вход первого дополнительного ключа соединен с вторым выводом первого диода, выход — с первой шиной положительной полярности напряжения, первый вход

k-го дополнительного компаратора соединен с первым выводом k-го дополнительного источника напряжения смещения, второй вывод которого, кроме m-го дополнительного источника напряжения смещения, соеди5

45 нен с (j- 1)-й шиной отрицательной полярности напряжения, вторсй вывод m-го дополнительного источника напряжения смещения соединен с (m -1)-й шиной отрицательной полярности напряжения, вгорой вход каждого дополнительного компаратора соединен с выходом двухтактного усилительного каскада. а выход k-ro дополнительного компаратора соединен с управляющим входом k-го дополнительного ключа соответсгвенно, а также введено и дополнительных диодов, ключей, компараторов, источников напряжения смещения, причем первый вывод 1-го дополни тельного диода,где 1=1,2,...„ n кроме п-го,соединен

) с выходом (1+1)-го дополнительного ключа, вход которого соединен с (i-1)-й шиной отрицательной полярности напряжения, второй вывод каждого дополнительного диода соединен с выводом питания транзистора второго плеча двухтактного усилительного каскада, первый вывод п-го дополнительного диода соединен с (и-1)-й шиной положительной полярности напОяжения, вход первого дополнительного ключа соединен с первым выводом первого диода, выход — с первой шиной отрицательной полярности напряжения, первый вход каждого дополнительного компаратора соединен с выходом двухтактного усилительного каскада, второй вход 1-r o дополнительного ком пара тора соединен с вторым выводом 1-го дополнительного источника напряжения смещения, первый вывод которого. кроме п-го дополнительного источника напряжения смещения, соединен с (1-1)й шиной положительной полярности напряжения, первый вывод и-го дополнительного источника напряжения смещения соединен с (n — 1)-й шиной положительной полярности напряжения, а выход 1-го дополнительного компаратора соединен с управляющим входом 1-го дополнительного ключа соответственно.

1656668

16Г?бб?б?Л а) > Ocr(n-

Ос те

Uc r (rp- r) Редактор T. Клюкина

Заказ 2019 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35. Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Ucv

Q 0сг Усн Ост

Ocr

-Llcr - Огм

Составитель Н. Дубровская

Техред М.Моргентал Корректор M.Äåì÷èê