Шифратор

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки и передачи цифровой информации. Цель изобретения - повышение быстродействия шифратора. Шифратор содержит блок 1 мультиплексирования, элемент И 2, первый буферный регистр 3, элемент ИЛИ 4, первый регистр 7 сдвига, распределитель 8 импульсов , второй регистр 9 сдвига, блок 10 шифрации, элемент 11 задержки, второй буферный регистр 12 и триггер 13, группу 14 информационных входов, управляющий вход 15, вход 16 сброса, группу 17 информационных выходов и управляющий выход 18 шифратора. 4 ил.

СОЮЗ COBETCKVIX

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5!)5 Н 03 М 7/22

ГОС УДАР СТ В Е ННЪ| Й КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

6й(пц30

)(МЕРТВ - 7

Г." :Á:II t

ОПИСАНИЕ ИЗОБРЕТЕНИЯ!

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4709019/24 (22) 22.08.89 (46) 15.06,91.. Бюл. в 22 (72) В. С. Танасийчук, Р. Т. Смук и А. А.

Самчинский (53) 681.325(088.8) (56) Авторское свидетельство СССР

N 11333366224488, кл. Н 03 М 7/22, 1986.

Авторское свидетельство СССР йв 1439748, кл. Н 03 М 7/22, 1987. (54) ШИФРАТОР (57) Изобретение относится к автоматике и вычислительной технике и может быть ис5U 1656687 А1 пользовано в системах обработки и передачи цифровой информации, Цель изобретения — повышение быстродействия шифратора. Шифратор содержит блок 1 мультиплексирования, элемент И 2, первый буферный регистр 3, элемент ИЛИ 4, первый регистр 7 сдвига, распределитель 8 импульсов, второй регистр 9 сдвига, блок 10 шифрации, элемент 11 задержки, второй буферный регистр 12 и триггер 13, группу 14 информационных входов, управляющий вход 15, вход 16 сброса, группу 17 информационных выходов и управляющий выход 18 шифратора. 4 ил.

1656687

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки и передачи цифровой информации.

Цель изобретения — повышение быстродействия шифратора.

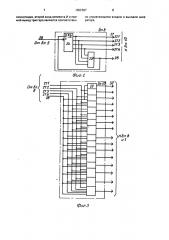

На фиг, 1 изображена схема шифратора; на фиг. 2 и 3 — схемы соответственно распределителя импульсов и блока шифрации; на фиг. 4 — временные диаграммы работы шифратора, Шифратор содержит блок 1 мультиплексирования, элемент И 2, первый регистр 3, элемент ИЛИ 4, генератор 5 тактовых импульсов, блок 6 коммутации, первый регистр 7 сдвига, распределитель 8 импульсов, второй регистр 9 сдвига, блок 10 шифрации, элемент 11 задержки, второй буферный регистр 12 и триггер 13. Шифратор имеет группу 14 информационных входов. управляющий вход 15, вход 16 сброса, группу 17 информационных выходов и управляющий выход 18, Блок мультиплексирования построен на группе 19 логических элементов И-НЕ с открытым коллектором на выходе и блоке 20 резисторов.

Блок коммутации построен на основе группы 21 логических элементов И-НЕ с открытым коллектором на выходе, резисторе 22 и инверторе 23.

Распределитель импульсов содержит регистр 24 сдвига, элемент ИЛИ вЂ” НЕ 25, а также синхровход 26, группу 27 выходов и выход 28.

Формирователь стробирующих импульсов содержит группу 29 элементов ИЛИ и имеет группу 30 выходов, Первые входы элементов И вЂ” НЕ группы 19 являются информационными входами блока мультиплексирования, Вторые входы каждых К элементов И вЂ” НЕ 19 объединены и являются управляющими входами блока мультиплексирования. Выходы I-x элементов И-НЕ 19 каждой группы (И,К) подключены к одному из резисторов блока 20 и являются 1-м выходом блока 1 мультиплексирования.

Первые входы элементов И-НЕ группы

21 являются информационными входами блока 6 коммутации. Вторые входы элементов груг,пы 21 являются управляющими входами блока 6 коммутации. Выходы элементов И-НЕ объединены и подключены к резистору 22 и входу инвертора 23, выход которого является выходом блока 6 коммутации.

Синхровход регистра 24 сдвига является синхровходом распределителя 8 импульсов, группа выходов которого соедине га с

50 выходами регистра 24 сдвига и входами элемента ИЛИ вЂ” НЕ 25, выход которого подключен к информационному входу регистра 24 и является выходом распределителя 8 импульсов.

Группа 14 состоит из и информационных входов, разбитых на группы по k входов в каждой, причем количество групп и/k должно быть меньше или равно количеству входов в группе k. Количество информационных входов блока б коммутации и количество выходов формирователя стробирующих равно k. Количество выходов руппы 27 распределителя 8 импульсов определяется количеством двоиччых разрядов, необходимых для представления в выходном коде числа К-1. Так, для шифратора, преобразующего 256-разрядный унитарный входной код (единица в одном из 256-ти разрядов) в 8-разрядный двоичный код, группа 27 распределителя 8 импульсов содержит 4 выхода (256 входов разбито на 16 групп по 16 входов в группе, для представления К-1=15 в двоичном коде необходимо

4 разряда).

Блок 10 шифрации содержит группу 29 из логических элементов ИЛИ, выходы которых являются группой 30 выходов блока 10.

Первые входы группы 29 логических элементов ИЛИ объединены и являются входом 28 блока 10. (j+1)-й вход i-го элемента группы

29 логических элементов ИЛИ, содержащего единицу e I-м разряде числа 1, представленном в выходном коде шифратора . подключен к I-му входу группы 27 входов блока 10. где )-О,..., m (m — количество единиц в числе 1, представленном в выходном коде шифратора); I=O,...,К-1: I=O...S (S — количество двоичных разрядов, необходимых для представления в выходном коде числа

К вЂ” 1).

Например, при К=16 третий элемент

ИЛИ (i-3) группы 29 имеет три входа (m-2, поэтому j+1=1„.,3), причем первый вход подключен к второму входу блока 10, второй вход подключен к первому входу группы 27 входов, а третий — к второму входу этой группы (фиг. 3).

Шифратор работает следующим образом.

В исходном состоянии на управляющем входе 15 шифратора присутствует лог."О", который, пройдя через элемент И 2, запрещает работу генератора 5 тактовых импульсов. Триггер 13 находится в сброшенном состоянии, т, е. на его инверсном выходе грисутствуег лог."1". Потенциал nor."!" на выходе 28 распределителя 8 импульсов, постугая на вход блока 10, переводит его выхорь в единичное состояние. Все элементы

1656687

10

И-НЕ группы 19 открыты единичными потенциалами, поступающими с выходов блока 10.

Временные диаграммы работы шифратора, когда на его входах присутствует код, содержащий единицу в десятом разряде шестой группы, приведены на фиг, 4, Работа шифратора начинается по сигналу на входе 15, который пройдя через элемент И 2, разрешает работу генератора

5 тактовых импульсов и записывает в регистр 3 состояние выходов блока 1 мультиплексирования. B рассматриваемом случае это будет лог."0" в десятом разряде на фоне лог."1" во всех остальных разрядах, Фронт импульса с выхода генератора 5, поступая на синхровход распределителя 8 импульсов, вызывает появление на его первом выходе группы выходов 27 лог."1", которая, поступая на входы соответствующих элементов ИЛИ группы 29, вызывает появление на выходах блока 10 кода А=1010 1010

1010 1010.

Код А, поступая на управляющие входь блока 1 и блока 6, вызывает появление лог."0" и лог."1" соответственно на выходе элемента ИЛИ 4 и выходе блока 6 коммутации.

По спаду тактового импульса первый и пятый разряды выходного кода шифратора записываются соответственно в регистры 7 и 9. Следующий фронт тактового импульса переключает распределитель 8, выходные сигналы которого вызывают появление на выходах блока 10 кода В=1100 1100 1100

1100, Код В, поступая на управляющие входы блока 1, разрешает прохождение входных сигналов во второй, третьей, шестой, седьмой, десятой, одиннадцатой, четырнадцатой и пятнадцатой группах элементов

И вЂ” НЕ. Единица на десятом входе шестой группы элементов И вЂ” НЕ вызывает появление единицы на выходе элемента ИЛИ 4, лог."1" появляется также и на выходе блока

6 коммутации, так как десятый элемент группы 21 логических элементов И-НЕ открыт и разрешает прохождение лог."1" с десятого входа блока 6 на его выход.

Спадом тактового импульса в регистрах

7 и 9 фиксируются второй и шестой разряды выходного кода шифратора. В последующих двух тактах работы шифратора в регистры 7 и 9 записываются третий, четвертый, седьмой и восьмой разряды выходного кода шифратора, При этом на выходах формирователя 10 последовательно устанавливаются коды С=1111 0000 1111 0000 и D--1111

1111 0000 0000. Последний тактовый импульс вызывает появление фронта на выхо15

55 де 28 распределителя 8, который записывает в регистр 12 состояние выходов регистров 9 и 7 и, пройдя через элемент 11 задержки, устанавливает триггер 13 в единичное состояние. Элемент 11 имеет время задержки, равное времени переключения регистра 12. Лог."0" на инверсном выходе триггера 13, пройдя через элемент И 2, останавливает работу генератора 5 тактовых импульсов.

Формула изобретения

Шифратор, содержащий блок мультиплексирования, входы которого являются информационными входами шифратора, выходы блока мультиплексирования соединены с соответствующими информационными входами первого буферного регистра, триггер, вход сброса которого является входом сброса шифратора, инверсный выход триггера соединен с первым входом первого элемента И, второй буферный регистр, выходы которого являются информационными выходами шифратора, генератор тактовых импульсов, элемент ИЛИ, элемент задержки, отличающийся тем, что, с целью повышения быстродействия шифратора, в него введены регистры сдвига, распределитель импульсов, блок шифрации и блок коммутации, выходы первого буферного регистра соединены с соответствующими информационными входами блока коммутации. выход которого соединен с информационным входом первого регистра сдвига, выходы которого соединены с соответствующими первыми информационными входами второго буферного регистра, входы элемента ИЛИ подключены к соответствующим выходам блока мультиплексирования, выход элемента ИЛИ соединен с информационным входом второго регистра сдвига, выходы которого соединены с соответствующими вторыми информационными входами второго буферного регистра. выход элемента И соединен с синхровходом первого буферного регистра и управляющим входом генератора тактовых импульсов, выход которого соединен с синхровходами регистров сдвига и распределителя импульсов, выходы которого соединены с соответствующими входами блока шифрации, синхровход второго буферного регистра объединен с входом элемента задержки и подключен к последнему выходу распределителя импульсов, выход элемента задержки соединен с синхровходом триггера, выходы блока шифрации соединены с соответствующими управляю цими входами блока мультиплексирования и блока

1656687

&д коммутации, второй вход элемента И и прямой выход триггера являются соответственФиг 2 но управляющими входом и выходом шифратора, Кбл. б и8

1656687

Я7.

Составитель О,Неплохое

Техред М,Моргентал Корректор Т.Палий

Редактор Е.Копча

Заказ 2057 Тираж 463 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва. Ж-35, Раушская наб.. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород. ул.Гагарина, 101