Устройство для сопряжения источника и приемника информации

Иллюстрации

Показать всеРеферат

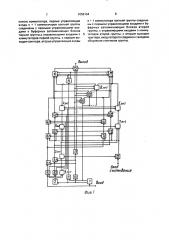

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства преобразования и буферизации данных в системах контроля, а также для сопряжения ЭВМ с каналами связи . Цель изобретения - расширение функциональных возможностей за счет возможности регулирования выходного информационного потока. Устройство содержит два регистра, формирователь признаков записи, п+1 группу счетчиков записи, две группы буферных запоминающих блоков, три гоуппы коммутаторов, группу блоков управления записью, два дешифратора, счетчик, триггер, три коммутатора . 3 ил.

СОЮЗ СОГ4ЕТСКИХ

СОЦИАЛИС1ИЧГСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕ HHbl Й КОМИТЕТ по изоБРетениям и ОткРытиям

ПРИ ГКНТ СССР

IGtC0 йййИТИ:-l,Á f1È

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4700618/24 (22) 05.06.89 (46) 23.06.91. Бюл. ¹ 23 (72) Ю.Н. Агеев и А.К. Леонтьев (53) 681.3 (088.8) (56) Авторское свидетельство СССР

¹ 1522220, кл. G 06 F 13/00, 30.08,88, (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИСТО4НИКА И ПРИЕМНИКА ИНФОРМАЦИИ (57) Изобретение относится к вычислительной технике и может быть использовано в качестве устройства преобразования и буИзобретение относится к вычислительной технике и может быть использовано в качестве устройства преобразования и буферизации данных в систел4ах контроля, а также для сопряжения ЭВМ с каналами связи, Цель изобретения — расширение функциональных возможностей за счет возможности регулирования выходного информационного потока, На фиг, 1 изображена структурная схема устройства для сопряжения источника и приемника информации; на фиг. 2 — струк турная схема блока управления записью; на фиг, 3 — диаграммы, почсняющие работу блока управления записью.

Устройство сопряжения источника и приемника информации содержит первыи регистр 1, формлрователь 2 признаков записи, первый счетчик и группу и счетчиков

3.1 — З,п + 1, первый буферный запоминающий блоки, первую группу буферных запоминающих блоков 4 1 — 4.п 1, второй

„.,5U„„1658164 А1 феризации данных в системах контроля, а также для сопряжения ЭВМ с каналами связи, Цель изобретения — расширение функциональных возможностей эа счет возможности регулирования выходного информационного потока. Устройство содержит два регистра, форм и ро вател ь признаков записи, и+1 группу счетчиков записи, две группы буферных запоминающих блоков, три группы коммутаторов, группу блоков управления записью, два дешифратора, счетчик, триггер, три коммутатора, 3 ил, буферный запоминающий блок и вторую группу буферных запоминающих блоков 5.1—

Б.n + 1, второй коммутатор и первую группу и коммутаторов 6.1 — 6.п 1, третий коммутатор и вторую группу и коммутаторов 7.1 — 7.n + 1, третью группу коммутаторов 8.1 — 8.n + 1, группу блоков 9.1 — 9.п + 1 управления записью, первый 10 и второй 11 дешифраторы, второй счетчик 12, триггер 13, второй регистр 14, первый 15. четвертый 16 и пятый

17 коммутаторы, Блок управления записью содержит два э емента 18 и 19 задержки. элемент И 20 и сдновибратор 21, Устройство работает следующим образом.

Поступающее иэ источника в регистр 1 адресно- информационное слово разделяется в нем на адрес и информацию Адрес поступает на вход формирователя 2 признаков. записи, на вход дешифратора 10. на адресный вх д дешифратора 11

1658164

Информация с выхода регистра 1 поступает на информационные входы дешифратора 11 и коммутаторов 8.1 — 8.п ь 1.

Дешифратор 10 при поступлении фиксированного адреса, свидете.ьствующего об окончании цикла записи-. <итывания устройства, выдает сигнал для обнуления гчет чиков 12 и 3,1 — З.п -I 1 и переключения триггера 13, который управляет переключением буферных запомина<о.цих блоков 4.1—

4.fl + 1 в режиме записи (или считывания) и буферных запоминающих блоков 5 1 — 5.n+

1 в режим счигывания (или записи) в зависимости от состояния выходов. (<ап,эилii.,р, исходное состояние триггера 13 "01", при этом буферные запоми ающие блоки 4,1—

4,п i- 1 находя гся в режиме записи. а буферные запоминающие блоки 5 1 — 5.n+ 1 находятся в режиме считывания. Г!р<л этом к выходу коммутатора 15 подключается его второй информационный вход, свяэа;<ный с выходом коммутатора 17, к первым выходам коммутаторов 8.1 - 8,n + ;, сг<язанны л с входами выходами буферных aaf

КОД, . PBH :L, .йСЯ В f1OC fORI;i<ОЛ -;.BI Oi. И;:<Ющем ус ройстве по этому адресу. При налиЧИИ < B О,IIС<Л1 ИAИ HЕСVПГ6КИХ, аЗРЯДак постоя<<ного заг<омина« щ ..го ус, ройства, соответствующих выходов формирова< ..ля 2 признаков записи, поступают сигналы нл вторые R

На первых и вторых выходах с< 6 ветствующих GfloKQB 9. 1 -- 9. л + 1 записью формируются стробы записи, поступающие на счетные входы сос т«етствующих c4fтчиков 3,1 — 3 и + 1 (фиг, Зг) u на вторы > управляющие входы соотяс;ствующих буферных запоминающих блоков 1,1—

4.п + 1 5 1 — 5 и + 1 (фиг, Зд). 1-<а вь<ходях соответствующих счетчиков 3.1 — З.fi - 1 формируются адреса записи, Адреса записи через коммутаторы 6.1—

6сп + 1 поступают на адресныс вкось<, а информация через коммута и ры R. 1 — 8. n + 1—

25 0

35 л0

55 на входы -выходы буферных запоминающих блоков 4.1 — 4,n + 1. Запись информации происходит в те буферные запоминающие блоки, на управляющих входах которых сформированы стробы записи. Таким образом, поступившие адресно- информационное слово записывается в одно или несколькс буферных запоминающих блоков.

Параллельно с записью информации в буферные запоминающие блоки 4.1 — 4п + 1 происходит считывание информации одного иэ буфернь<х запоминающих блоков 5.1 — 5.n+ 1 следующим образом, Буферный запоминающий блок, из которого дол:кна быть считана ин 5орглация, определяется источником инфо,.<мации (например, цифровой вычислительной си темой), который по результатам ал< пр тмического и а паратурного контроля

Фу,-<хцИОНаГ6ЧЫХ ПОдСИСтЕМ В КОНЦЕ КаждОГО цикл "„ писи-считывания формирует команду на выбор буферного запоминающего блока, соп роеождаемую фиксированным адресом.

Адрес«о -информационное слово, содержащс;е кс<манду на выбор буферного запоминаю,!cia блок-<, поступает на вход дешифратора

11, " сфор лированнь<й им признак номера бу<, ерног; запоминающего блока записывается в регистр 14 и там храни-ся до поступления очередной I.ouaai

Уира«ля ощил< сигналом с одного из выходов регигггра 14 вход-выход выбранного б фсрного запоминающего блока подключа <тся врез коммутаторы 17 и 15 к выходу у;тройства.

Для считывания информации на вход считывания устройства из приемника поступа от сигналы считывания. Счетчик 12 при пос1уплении каждого очередного сигнала считывания формирует адрес считывания, который через коммутаторы 7,1 — 7.n + 1 посту« е1 на адресные входы буферных запс мина«1щих блоков 5.1 — 5.fl + 1. Считывание из выбранного буферного запол «нающего блока осуществляется по

vBIu:äof ó сигналу считывания. Информация из буферных запоминающих блоков 5.1 — 5,fl

1 поступает на информационные входы

:соммутатора 17 и далее через коммутатор

15 на выход устройства, При поступлении на дешифратор 10 фиксированного адреса, свидетельствую<.го об окончании цикла записи — считывания устройства, происходит установка с <етчиков 12 и 3.1 — З.n + 1 в исходное сс .тояние и смена состояния триггера 13 на

"10". Триггер 13 переключает буферные запоминающие блоки 3< 1 — 5,п + 1 е режим записи, а буферные запол<инающие блоки

1658164

4,1 — 4.п + 1 в режим считывания, при этом к выходу коммутатора 15 подключается его первый информационный вход, связанный с коммутатором 16, к вторым выходам коммутаторов 8.1 — 8.п - 1, связанным г входами — выходами буферных запоминающих блоков 5.1 — 5.п+ 1, подключаются их информационные входы, к выходам коммутаторов

6.1 — 6.п+ 1 подключаются их информационные входы, связанные с выходами сче чиков 3.1 — 3.п + 1. Запись и считывание информации происходит аналогично описанному, Устройство помимо буферизации принимаемой информации осуществляет регулирование выходного информационно Ъ потока, что позволяет выбирать и передавать наиболее важную на текущий момент информацию передатчика и, таким образом, эффективно испольэовать пропускную способность и производительность приемника информации.

Формула изобретения

Устройство для сопряжения источника и приемника информации, содержащее два счетчика, триггер, с первого по пятый коммутаторы, два буферных запоминающих блока, блок управления записью, первый дешифратор, регистр, выход разрядов адреса которого соединен с входом первого дешифратора, выход которого соединен с входами обнуления первого и второго счетчиков, входом триггера, первый выход триггера соединен с первым управляющим входом первого коммутатора, с первым управляющим входом первого буферного запоминающего блока, с управляющим входом второго коммутатора, DTopovl выход триггера соединен с первым управляющим входом второго буферного запоминающего блока, с управляющим входом третьего коммутатора, с вторым управляющим входом первого коммутатора, выход которого является выходом устройства для подключения к входу данных приемника, первый и второй информационные входы первого коммутатора соединены соответственно с выходами четвертого и пятого коммутаторов, информационные входы которых соединены соответственно с входами-выходами первого и второго буферных запоминающих блоков. вторые управляющие входы которых соединены с первым выходом блока управлоения записью, адресные входы первого и второго буферных запоминающих блоков соединены соответственно с выходами второго и третьего коммутаторов, первые информационные входы которых соединены с выходом первого счетчика, вторые информационные входы — с выходом второго счетчика, счет5

55 ный вход первого счетчика соединен с вторым выходом блока управления записью, первый вход которого соединен с входом первого регистра и является информационным входом устройства для подключения к информационному выходу источника, вход второго счетчика является входом устройства для подключения к выходу считывания приемника, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет возможности регулирования выходного информационного потока, в него введены второй дешифратор, второй регистр, две группы по и коммутаторов, третья группа иэ n+ 1 коммутаторов, группа из п счетчиков, группа из и блоков управления записью. две группы по и буферных запоминающих блоков, формирователь признаков записи, вход которого соединен с выходом разрядов адреса первого регистра и адресным входом второго дешифратора, первый выход формирователя признаков записи соединен с вторым входом первого блока управления записью, а остальные п выходов соединены с первыми входами соответствующих и блоков управления записью группы, вторые входы которых соединены с входом устройства для подключения к информационному выходу источника, первые выходы и блоков управления записью группы соединены со счетными входами соответствующих и счетчиков группы, выходы которых соединены с первыми информационными входами соответствующих п коммутаторов первой и второй групп, вторые информационные входы которых соединены с выходом второго счетчика, выходы и коммутаторов первой и второй групп соединены с адресными входами соответствующих и буферных запоминающих блоков соответственно первой и второй групп, вторые управляющие входы которых соединены с вторыми выходами соответствующих п блоков управления записью, входы — выходы и буферных запоминающих блоков первой и второй групп соединены соответственно с информационными входами четвертого и пятого коммутаторов, управляющие входы которых соединены с соответствующими выходами второго регистра, вход которого соединен с выходом второго дешифратора, информационный вход которого соединен с информационным выходом первого регистра и с информационными входами n + 1 коммутаторов третьей группы, первые выходы которых соединены с соответствующими входами четвертого коммутатора, вторые выходы п + 1 коммутаторов третьей группы соединены с соответствующими входами

1658164

041 пятого коммутатора, первые управляющие входы n + 1 коммутаторов третьей группы соединены с первыми управляющими входами и буферных запоминающих блоков первой группы,с управляющими входами и коммутаторов первой группы, с первым выходом триггера, вторые управляющие входы и + 1 коммутатора третьей группы соединены с первыми управляющими входами и буферных запоминающих блоков второй группы, с управляющими входами и комму5 таторов второй группы, с вторым выходом триггера, вход которого соединен с входами обнуления счетчиков группы.

1658164

Йа l

Фиг 2

Составитель А. Грошев

Редактор И. Дербак Техред М,Моргентал Корректор А.Осауленко

Заказ 1714 Тираж 410 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул. Гагарина, 101