Устройство блочной синхронизации

Иллюстрации

Показать всеРеферат

Изобретение относится к технике электрической связи и может быть использовано для блочной синхронизации в цифровых системах передачи информации. Цель изобретения - повышение помехоустойчивости. Устройство содержит счетчик 1 текущей цифровой суммы, последовательные регистры 2 и 3, параллельный регистр 4, дешифратор 5 запрещенных комбинаций, счетчик-накопитель 6, решающий блок 7, блок 8 формирования импульсов разрешения и элемент ИЛИ 9. Повышение помехоустойчивости достигается за счет использования сигнала с выхода младшего разряда счетчика 1 текущей цифровой суммы в качестве сигнала окончания блоков информации, при этом фазировка счетчика 1 не зависит от ошибок в канале связи. 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

1660193 А1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Ф

О

ЪФ (21) 4636354/09 (22) 12.01.89 (46) 30.06.91. Бюл. ¹ 24 (72) СЛ. Макаренко (53) 621.394.662(088.8) (56) Авторское свидетельство СССР

¹ 1328941, кл. Н 04 L 7/00, 1987.

I (54) УСТРОЙСТВО БЛОЧНОЙ СИНХРОНИЗАЦИИ (57) Изобретение относится к технике электрической связи и может быть использовано для блочной синхронизации в цифровых системах передачи информации, Цель изобреs Н 04 1 7/00, 7/02, 7/08 тения — повышение помехоустойчивости.

Устройство содержит счетчик 1 текущей цифровой суммы, последовательные регистры 2 и 3, параллельный регистр 4, дешифратор 5 запрещенных комбинаций, счетчик-накопитель 6, решающий блок 7, блок 8 формирования импульсов разрешения и элемент ИЛИ 9, Повышение помехоустойчивости достигается за счет использования сигнала с выхода младшего разряда счетчика 1 текущей цифровой суммы в качестве сигнала окончания блоков информации, при этом фазировка счетчика 1 не зависит от ошибок в канале связи. 4 ил.

i 660193

Изобретение относится к технике электрической связи и может быть использовано для блочной синхронизации в цифровых системах передачи информации.

Цель изобретения — повышение помехоустойчивости устройства.

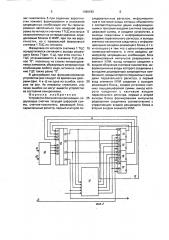

На фиг. 1 изображена структурная электрическая схема предлагаемого устройства; на фиг. 2 — вариант выполнения счетчика текущей цифровой суммы; на фиг. 3 — вариант выполнения счетчика-накопителя; на фиг. 4 — временные диаграммы, поясняющие работу устройства.

Устройство содержит счетчик 1 текущей цифровой суммы (ТЦС), первый 2 и второй 3 последовательные регистры, параллельный регистр 4, дешифратор 5 запрещенных комбинаций (3K), счетчик — накопитель 6, решающий блок 7, блок 8 формирования импульсов разрешения (ФИР) и элемент

ИЛИ 9.

Счетчик 1 текущей цифровой суммы 1 состоит из дешифратора 10 входных комбинаций (ВК), арифметика-логического устройства 11 (АЛУ), дешифратора текущей цифровой суммы (ТЦС) и блока 13 памяти, состоящего из четырех D-триггеров

14-17.

Счетчик-накопитель 6 состоит иэ первого 18 и второго 19 RS-триггеров, элемента

И 20 и первого 21 и второго 22 0-триггеров

21 и 22.

Устройство работает следующим образам.

При включении устройства счетчик 1

ТЦС устанавливается в произвольное состояние(например, в состояние. соответствующее ТЦС = +3 (фиг, 4г-з), которое не совпадает с истинным значением ТЦС ни по величине, ни по четности этого значения), Одновременно блок 8 ФИР со второго своега выхода формирует короткий импульс (фиг. 4х), который через элемент ИЛИ 9 (фиг.

4ш) сбрасывает в нулевое состояние D-триггеры 21 и 22 (фиг. 4 т, у, ф) счетчика-накопителя 6, а на первом выходе блока 8 ФИР формируется импульс большой длительнаСти, поступающий на вход разрешения решающего блока 7 (фиг. 4ц), Работа счетчика ТЦС 1 показана на временных диаграммах фиг, 4в-з, Поступающие íà его информационные входы двоичные сигналы У1 и У2, представляющие четырехуровневый символ, в дешифраторе 10 входных комбинаций преобразуются в двоичную комбинацию

81...84, представляющую вес четырехуровневого символа четыремзэрядным двоичным кодам.

50 ный сигнал, поступая на информационные входы последовательных регистров 2 и 3, преобразуется в параллельный вид (фиг. 4 и — м) с помощью параллельного регистра 4, управляемого сигналом с выхода счетчика 1

ТЦС, Дешифратор 5 ЗК выделяет при этом запрещенные комбинации (фиг, 4 н, о), которые могут возникать в случае ошибок в канале передачи либо в случае отсутствия синхрониэма. Счетчик-накопитель 6 увеличивает свое содержимое на единицу (фиг. 4 т, у, ф) только в том случае, если на его входах присутствует информация о запрещенных комбинациях обоих видов, что позволяет защитить счетчик-накопитель 6 от однапалярных ошибок. Для этого информация с каждого выхода дешифратора 5 ЗК запоминается в соответствующем RS-триггере 18 или 19 (фиг, 3 и фиг. 4 и. р), а импульс с выхода элемента И 20(фиг. 4 с) появляется лишь в случае появления запрещенных комбинаций обоих видов.

Анализ информации с выходов счетчика-накопителя 6 может осуществляться решающим блоком 7 лишь в период времени, который задается длительным импульсом разрешения..поступающим на вход разрешения решающего блока 7 с первого выхода блока 8 ФИР (фиг. 4 ц). Длительность этого импульса и емкость счетчика-накопителя 6 должны быть выбраны такими, чтобы счетАрифметика — логическое устройство 11 ,(АЛУ), включенное в режиме суммирова-,. ния, суммирует входную комбинацию

В1.„84 АЛУ 11 с двоичной комбинацией предыдущего результата сложения, которая поступает на входы А1...А4 АЛУ 11 с выходов

0-триггеров 14-17 блока 13 памяти (фиг, 2).

При превышении АЛУ 11 граничных значений ТЦС дешифратор 12 ТЦС устанавливает выходы блока 13 памяти в состояние, соответствующее ближайшему разрешенному значению ТЦС, которое на временных диаграммах (фиг, 4 д-з) показано цифрами. При появлении уровня логической единицы на

15. входе установки дешифратора 12 ТЦС выходы блока 13 памяти будут установлены в состояние, соответствующее нулевому значению ТЦС.

Кэк видно иэ временных диаграмм (фиг.

4а — фиг. 4щ) до поступления на вход установки счетчика ТЦС 1 импульса с выхода решающего блока 7 младший разряд Х4 АЛУ

11 осуществляет неверное разделение входнога сигнала на блоки, но ни одно из превышений граничного значения ТЦС не меняет фазы сигнала блочной синхронизации, роль которого выполняет младший разряд Х4

АЛУ 11 (фиг, 2), Одновременно входной информацион1660193 . чик-накопитель 6 при заданных вероятностях ложного формирования и искажения запрещенных комбинаций мог бы гарантированно заполниться при неверной фаэировке по четности счетчика 1 ТЦС и остаться незаполненным эа интервал времени, определяемый блоком 8 ФИР, при тех же вероятностях, но с правильной фазировкой счетчика 1 ТЦС по четности.

Фаэировка по четности счетчика 1 ТЦС осуществляется сигналом с выхода решающего блока 7 (фиг. 4 щ), при этом счетчик 1

ТЦС устанавливается в значение ТЦС,равное "0", поскольку на стыках четырехуровневых символов, образующих запрещенную комбинацию любого вида, истинное значение ТЦС также равно "0".

8 дальнейшем при функционировании устройства (как следует из временных диаграмм (фиг. 4 в-э) ни одна из ошибок, которые на фиг. 4в показаны стрелками. или пачек ошибок не могут вывести устройство иэ состояния синхронизма.

Формула изобретения

Устройство блочной синхронизации, содержащее счетчик текущей цифровой ñóìмы, счетчик-накопитель, решающий блок, параллельный регистр, первый и второй последовательные регистры, информационные и тактовые входы которых обьединены с соответствующими двумя информационными и тактовым входами счетчика текущей

5 цифровой суммы, и входами устройства, а выходы соединены с информационными входами параллельного регистра, а выходы счетчика-накопителя соединены с информационными входами решающего блока, о т л10 ича ющееся тем, что,сцельюповышения помехоустойчивости, в него введены дешифратор запрещенных комбинаций, блок формирования импульсов разрешения и элемент ИЛИ, выход которого соединен с

15 входом обнуления счетчика-накопителя, информационные входы которого соединены с выходами дешифратора запрещенных комбинаций, входы которого соединены с выходами параллельного регистра, а первый

20 вход элемента ИЛИ соединен с выходом решающего блока, входом установки счет чика текущейцифровой суммы, выход которого соединен с тактовым входом параллельного регистра, первый и второй

25 выходы блока формирования импульсов разрешения соединены соответственно с управляющим входом решающего блока и вторым входом элемента ИЛИ, Составитель С. Аджемов

Редактор В. Евдокимов Техред М.Моргентал Корректор Т. Малец

Заказ 1856 Тираж 399 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r, Ужгород, ул.Гагарина, 101