Многофункциональный логический модуль

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении многофункциональных устройств цифровой обработки информации и узлов промышленной автоматики. Цель изобретения - упрощение многофункционального логического модуля при вычислении симметрических булевых функций. Модуль содержит элемент ИЛИ 1, сдвиговый регистр 2, демультиплексор 3, шифратор 4, блок 5 вычисления элементарных симметрических булевых функций, триггер 6, элемент И 7, счетчик 8. На информационные входы модуля поступают двоичные переменные X<SB POS="POST">1</SB>, X<SB POS="POST">2</SB>,..., X<SB POS="POST">N</SB>, а в сдвиговый регистр заносится двоичный код φ(F) реализуемой симметрической булевой функции F = F(X<SB POS="POST">1</SB>, X<SB POS="POST">2</SB>,..., X<SB POS="POST">N</SB>). В течение N + 1 тактового цикла на выходе модуля реализуется значение функции F, определяемой двоичным кодом φ F. 1 з.п. ф-лы, 1 табл., 2 ил.

„„SU „„1661752

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (51)5 С 06 F 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCH0MV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4722059/24 (22) 24.07.89 (46) 07.07.91. Бюл. Y 25 (72) Л.Б.Авгуль, В.П.Супрун, Н.А.Егоров и В,И.Костеневич (53) 681.3 (088 ° 8) (56) Авторское свидетельство СССР 1",- 1559337, кл. G 06 F 7/00, 1988.

Авторское свидетельство СССР и 1137457, кл, С 06 F 7/00, 1983, (54) МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ

МОДУЛЬ (57) Из"бретение относится к вычис лительной технике и может быть использовано при построении многофункциональных устройств цифровой обработки информации и узлов промышленной автоматики. Цель изобретения—

2 упрощение многофункционального логи— ческого модуля при вычислении симметричных булевых функций. Модуль содержит элемент ИЛИ 1, сдвиговый регистр 2, демультиплексор 3, шифратор 4, блок 5 вычисления элементарных симметрических булевых функций, триггер 6, элемент И 7, счетчик

8. На информационные входы модуля поступают двоичные переменные Х, .Х,..., Х,, а в сдвиговый регистр заносится двоичный код й(Р) реализуемой симметрической булевой функ ции F = F (Х, Х,..., X ). В течение п+1-тактового цикла на выходе модуля реализуется значение функции

F, определяемой двоичным кодом B (F).

1 з. и. ф-лы, 2 ил., 1 табл.

1661752

Изобретение относится к вычислительной технике и может быть использовано при построении многофункциональных устройств цифровой обработки информации и узлов промышленной ав5 томатики.

Цель изобретения — упрощение многофункционального логического модуля при вычислении симметрических булевых функций (СБФ).

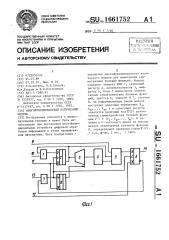

На фиг.1 представлена структурная схема многофункционального логичес1 кого модуля, на фиг.2 — функциональная схема блока вычисления элемен15 тарных СБФ (ЭСБФ), входящего в состав модуля, Модуль содержит элемент ИЛИ 1, сдвиговый регистр 2, демультиплексор 3, шифратор 4, блок 5 вычисления ЭСБФ, триггер 6, элемент И 7, счетчик 8, группу информационных входов 9, вход 10 настройки, первый

11 и второй 12 входы сброса модуля соответственно, тактовый вход 13 и 25 выход 14.

Блок вычисления ЭСБФ содержит и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 15 -15ll (n а количество аргументов реализуемых

ЭСБФ),мажоритарный элемент 16 с порогом и, мажоритарный элемент 17 с порогом п+1 (имеет только инверсный выход), элемент И 18, и информацион-. ных входов 191-191, и-1 настроечных входов 20 -20 1, вход 21 запрета и выход 22.

Модуль работает следующим образом.

Известно, что произвольная СБФ и аргументов F = F (Х<, Х, ° .., X )

40 может быть однозначно представлена в виде

F = ll F V ll,. F 9 ...Ф„F, (1) где F — элементарные (или фундаменI

6 45 тальные) СБФ от и аргументов, й; (0,1) и i"-О, 1..., п, При этом I

Таким образом, имеет место взаимнооднозначное соответствие между СБФ

Г = F (Х,, Х,...,Х <) и (и+1) -разрядным двоичным кодом Т (F) = (7 Я,, ° ° °

° ° llew)

Из (1 ) следует также, что 55

F = 3Fnl (2) где дизъюнкция берется по всем К, для которых Ок = 1.

Поскольку все ЭСБФ F взаимно орК тогональны, то на заданном наборе двоичных переменных Х, Х, ..., Х значение логической единицы принимает не более одной ЭСБФ из множества с

Г„ ). Следовательно, для вычисления

К1 произвольной СБФ Г=Г(Х,Х...,X ) от п аргументов Х„, Х,..., Х, зап1 данной посредством своего двоичного кода 1 (Г), можно предложить следующую пРоцедуРу: вычислять последовательно значения ЭСБФ из Г у на данг,К7 ном наборе аргументов Х „, Х до получения единичного значения и тогда F = 1 на данном наборе, либо до полного перебора всех ЭСБФ из F г К ъ п и тогда F = 0, так как на данном аборе все слагаемые в (2) равны нулю.

Модуль содержит сдвиговый регистр

2, в который заносится код g(F) реализуемой СБФ F = F (Х<, XZ> Х1,), Через демультиплексор 3 значение старшего разряда регистра 2 — значение очередного компонента 6 ° двоичного

I кода Ч (Г) управляет работой шифратора 4, формирующего код настройки блока 5 вычисления ЭСБФ: если ll-, = 1, шифратор 4 настраивает блок 5 на вычисление функции F, значение которой

4 на данном наборе фиксируется в тригл, гере 6, если 1; = О, работа шифратора

4 и последующих узлов блокируется.

Затем в сдвиговом регистре 2 осуществляется кольцевой сдвиг информаци на один разряд и производится аналогичный анализ компонента »; „, Работа продолжается либо да перебора всех компонент двоичного кода

6 запрещает поступление тактовых импульсов через элемент И 7 на вход модуля и свидетельствует о завершении вычисления значения F на данном наборе. Счетчик 8 в процессе работы указывает номер анализируемого компонента И;.

Многофункциональный логический модуль работает следующим образом.

Перед началом работы подаются импульсы на первый 11 и второй 12 входы сброса модуля, которые обнуляют сдвиговый регистр 2, триггер 6 и счетчик 8. Далее осуществляется настройка модуля на реализацию СБФ

166

1752 6

5(5

F = F (Х, Xg, ...,Хп), заданной своим двоичным кодом ll (F) = (пп, и и,..., и 1, ), В сопровождении серии из и+1 тактовых импульсов, подаваемых на тактовый вход 13, на вход 10 настройки поступают последовательно значения компонентов п, й, /э» ..., и„. В результате этого в (и+1)-м

Р разрядном сдвиговом регистре 2 записывается код и (Р), причем в стар/ шем разряде, соединенном с входом демультиплексора 3, входом запрета блока 5 вычисления ЭСБФ и.входом элемента ИЛИ 1 имеет место значение Т, а в младшем — значение 11

Модуль счета счетчика 8 равен n+1, Очевидно, разрядность счетчика равно т = ) 1ид (пт1), поэтому после подачи указанной серии из и+1 тактовых импульсов счетчик 8 снова переходит в нулевое состояние, код которого указывает двоичный номер компонента и вектора ll (F) подклюу, ченного к входу демультиплексора 3, Поскольку счетный вход счетчика 8 соединен .с тактовым входом сдвиго- вого регистра 2, то всегда г-раз-. рядный двоичный код i состояния счетчика 8 указывает номер компонента и;, находящегося в данный момент з старшем разряде сдвигового регистра 2. После занесения кода п(Р) в сдвиговый регистр 2 модуль готов к работе. На и шин группы информационных входов 9 модуля подаются двоичные аргументы Х1, Х, ° .., ° ° ° у Хе1 °

В течение (и+1) -го тактового цикла подготовки модуля к работе триггер 6 находится в нулевом состоянии т и единичный сигнал с его инверсно,. го выхода, подаваемый на вход элемента И, разрешает прохождение тактовых импульсов с тактового входа 13 на тактовый вход сдвигового регистра

2 и счетный вход счетчика 8, Это обеспечивается тем, что во время занесения в сдвиговый регистр 2 кода

l я(Г) на входе запрета блока 5 вычис ления ЭСБФ присутствует сигнал старшего разряда предварительно обнуленного сдвигового регистра 2. Этот нулевой сигнал и запрещает формирование сигнала логической единицы на выходе блока 5 во время подготовки модуля к работе.

Демультиплексор 3 имеет и+1 выход (с нулевого по и-й), один инфор5

4с мационный вход, связанный с выходом старшего разряда сдвигового регистра 2, и r = )1о8 (и+1)(адресных входов, на которые поступают сигналы с соответствующих разрядов счетчика 8 °

При этом при кольцевом сдвиге информации в сдвиговом регистре 2 в процессе вычисления СБФ F = F (Х<, Х,..., Х ) в старшем разряде последовательно присутствуют компоненты ум- у- Л

ll ", °,п 1, Ип, И,... и, таким I образом, значения этих компонентов в такой же последовательности имеют место на выходах демультиплексора 3. нулевом, первом,..., и-м, нулевом, первом,>и т,д.

Блок 5 вычисления ЭСБФ имеет и информационных входов, на которые с информационных входом 9 модуля поступают параллельно двоичные переменные

Х1, Х,..., Х yj реализуемой СБФ F

= Р (Х,, Х,..., Х,), и n — 1 настроечных входов, на которые поступает код настройки V = (П;, U 2,..., U 1) с выходов шифратора 4 и S = 1, 2,...,и-1. Функции шифратора 4 заключаются в преобразовании сигнала логической единицы на i-м входе (i = О, 1.. ., и) в (n-1)-й разрядный вектор V на выходе. Следовательно, шифратор 4 имеет n+1 входов и и-1 выходов. Поскольку выходы демультиплексора 3 соединены с соответствующими входами шифратора 4, одновременно на входах шифратора может действовать не более одного сигнала . логической единицы, поэтому всегда будет однозначное соответствие между сигналом llew = 1, действующим íà i-й вход шифратора 4, и вектором V, настраивающим блок 5 на вычисление ЭСБФ

F g (i = О, 1.. ., и), В исходном состоянии в старшем разряде сдвигового регистра 2 находится компонент и, вектора и (F), счетчик 8 обнулен. На нулевом выходе демультиплексора 3 также присутствует сигнал пд .

Если 1 = 1, шифратор 4 формирует вектор настройки (Пь, Uot

Upped ), настраивающ :й блок 5 на

l о реализацию функции F . Значение F

n H на данном наборе аргументов Х,, Х,..., Х 1, с выхода блока 5 подается на информационный вход триггера

6. По переднему фронту первого син1661752 хроимпульса рабочей серии, поступившего на тактовый вход 13 модуля, значение F записывается в одноступенЯ чатый триггер 6 (в качестве такого

5 триггера может быть выбран, напримЕР, синхронный D-триггер). Если.

F = 1 на данном наборе аргументов, Ь а следовательно Г = Г (Х, Х2...,, Х „) = 1 на данном наборе, сигналом с инверсного выхода триггера 6 дальнейшее поступление синхроимпульсов на тактовый вход 13 блокируется. Значение реализуемой функции

F равно логической единице и зафиксировано в триггере 6.

Если Ио = О (ЭСБФ F не входит в и (2) или F = О на данном наборе), то

5 по переднему фронту первого рабоче( гр синхроимпульса нулевое состоян е триггера 6 подтвердится, если

1 = 1, то значение старшего разряда сдвигового регистра 2, подаваемое на вход запрета блока .5, заблокирует его выходной сигнал. 25

В обоих случаях (к =О или и = 1) по заднему фронту первого синхроимп льса в сдвиговом регистре 2 произойдет кольцевой сдвиг информации (В старший разряд запишется значе- 30 нне,, в младший II ), а состояние

c åT÷èKà 8 увеличится на единицу и укажет номер компонента ф векто.. Ра q((Г), находящегося в данный мо-. мент в старшем разряде сдвигового регистра 2. При этом на первом выходе

35 демультиплексора 3 присутствует сигнал Ф и при II = 1 шифратор 4 нал

1 страивает блок 5 на реализацию функции F

Если после подачи первого рабоче 1 го синхроимпульса триггер 6 остался в нулевом состоянии, подается следующий рабочий синхроимпульс, по переднему фРонту котоРого в тРиггеР 45 б записывается значение F П на данном

I наборе аргументов Х, Х,..., X11 (при я 1 = 1), либо подтверждается нулевое состояние триггера 6 (при

= О). По заднему фронту этого

1 синхроимпульса также производится кольцевой сдвиг информации в сдвиговом регистре 2 и увеличение содержимого счетчика 8 на единицу. Если после второго такта триггер 6 остался в нулевом состоянии, подается третий синхроимпульс, по переднему фронту которого в триггер 6 заносится значение ЭСБФ Г„ на данном наборе (при

Если значение Г=Г(Х,Х2...,,Х ) было вычислено "досрочно" (единичное значение F было зафиксировано в триггере 6 за 1(t а n+1 тактовых импульсов), нет необходимости заканчивать текущую серию из и+1 рабочих тактовых импульсов. Триггер 6 обнуляется, а новое значение аргументов

Х, Х,..., Х сопровождается очередной серией тактовых импульсов. При этом, очевидно, начинается анализ не с компонента IIо (и соответствУюЩей функции F„ np II = 1), а с компонента II (и соответствующей функции F> при Я = 1). Таким образом, среднее время вычисления СБФ F=F(X 1,Х,..., XII) составит веничину (и+1) Л

Т =

2 (3) где c — период тактовых импульсов.

Коды настройки V " (U„, U 2, U ) и соответствующие им реализуе l. g

l ° мые ЭСБФ F (i = О, 1, ..., 4) для блока 5 (фиг. 2) при и = 4 представлены в таблице (значение сигнала на

Я = 1), либо подтверждается нуле2 вое состояние триггера. По заднему фронту синхроимпульса также происходит кольцевой сдвиг информации в сдвиговом регистре 2 и увеличение содержимого счетчика 8 на единицу.

Вычисление значения СБФ Г = Г(Х„, Х . .. Х ) на данном наборе аргументов продолжается либо до фиксации в триггере 6 единичного значения (это указывает, что F = 1 на данном наборе аргументов), либо до окончания

Ф рабочей серии из и+1 тактовых импульсов, подаваемых на тактовый вход 13.

В последнем случае значение F определяется состоянием триггера 6 после окончания (n+1)-го тактового импульса.

Для вычисления значения заданной

СБФ F = F (Х1, Х, ..., X„) Ha npYгом наборе аргументов на информационные входы 9 модуля подаются новые значения аргументов Х,, Х,..., Х, триггер 6 обнуляется подачей импульса на второй вход 12 сброса, а на тактовый вход 13 подается очередная рабочая серия из n+1 тактового импульса (последовательно импульс за импульсом либо до фиксации в триггере 6 единичного значения, либо до окончания всей серии импульсов).

1661752 (4) Ь! = а 3 а4 °

2. Модуль по п. 1, о т л и ч а ю40 шийся тем, что блок вычисления элементарных симметрических булевых функций содержит элемент И, мажоритарный элемент с порогом и (п — количество аргументов реализуемых эле45 ментарных симметрических булевых функций), мажоритарный элемент с порогом и+1 и п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход i-го (i = 1, 2. .. П) из которых соединен с- i-м информационным входом блока, второй вход соединен с первым настроечным входом блока, а выход соединен с 1-и входом мажоритарного элемента с порогом и

Ъ и х-м входом мажоритарного элемента

55 с порогом и+1т(n+j) é (j=l,?, °" -2) вход которого соединен с (j+1) м настроечным входом блока и (и+))-м входом мажоритарного элемента с порогом п, выход которого соединен с (5) входе 21 запрета равно при этом логической единице).

Как следует из фиг, 1 и 2, на вход

2 1 запрета блока 5 вычисления ЭСБФ поступает значение компонента q ° с л, выхода старшего разряда сдвигового регистра 2. Очевидно, если н =О, то л. в соответствии с (2) значение Г на данном наборе аргументов Х 11 ХС. " у

: ...,Х игнорируется -вследствие появления нулевого сигнала на выходе 22 блока 5, соединенного с информационным входом триггера 6.

Структуру шифратора 4 рассмотрим на примере для п = 4.Для этого воспользуемся таблицей настроек блока 5, Введем следующие обозначения: пусть а — сигнал на i-м выходе деI мультиплексора 3 (и соответственно на i-м входе шифратора 4), Ъ вЂ” сигнал на j-м выходе шифратора 4, соединенного с настроечным входом 20> блока 5, где i 0, 1, ..., 4 и j

1, 2, 3.

Как следует иэ таблицы настроек

Ь = а, b = а,Ча„Ча .

Таким образом, как следует из (4), при n = 4 шифратор 4 состоит из двух элементов ИЛИ на три входа каж.дый.

Если учесть ортогональность сигналов на входах шифратора 4, то

Ь =а

Ь =а уа<

) О

Из (5) следует, что шифратор 4 может быть построен также на основе двух двухвходовых элементов ИЛИ-НЕ.

Дополнительным положительным эффектом изобретения является более высокое быстродействие.

Формула и э о б р е т е н и я

1. Многофункциональный логический модуль, содержащий счетчик, сдвиговый регистр и элемент ИЛИ, первый вход которого соединен с входом настройки модуля, выход старшего разряда сдвигового регистра соединен с вторым входом элемента ИЛИ, выход

35 которого соединен с входом младшего разряда сдвигового регистра, вход установки в "О" которого соединен с входом установки в "0" счетчика и первым входом сброса модуля, о тл и ч а ю шийся тем, что, с целью упрощения при вычислении сим.метрических булевых функций, содержит демультиплексор, шифратор, блок вычисления элементарных симметрических булевых функций, триггер и элемент И, тактовый вход модуля соединен с первым входом элемента И, второй вход которого соединен с инверсным выходом триггера, выход элемента И соединен со счетным входом счетчика, с тактовым входом триггера и с тактовым входом сдвигового регистра, выхол старшего разряда которого соединен с входом запрета блока вычисления элементарных симметрических булевых функций и с информационным входом демультиплексора, адресные входы которого соединены с выходами счетчика, выходы демультиплексора соединены с входами шифратора, выходы которого соединены с настроечными входами блока вычисления элементарных симметрических булевых функций, информационные входы которого соединены с информационными входами модуля, а выход соединен с информационным входом триггера, вход установки в "О" которого соединен с вторым входом сброса модуля, а прямой выход соединен с выхолом модуля.

1661752

Реализуемая функция

Значения сигналов на входах настроечных

Г (19) 19 19-„194 20(20 20э о

Р, = Х, Х, У.,:.,1 !

F = Xi XzXgXqV Х1х хзх Ч X

Р = Х1 Х Х Х Ч Х Х хз Х q Ч Х, Х Хз Х Ч

М Х Х Х Х Ч Х1Х ХЗХ Ч Х Х х Х

= X(XzX X × X, X,X, X X(XZ X X Y

4.

V X,,X2XsX Ф

F = Х,х,х,х х х х х, 1 О О

1 0 I

1 1 1

0 О 1. 0 0 О

Фиг. 2

Составитель В.Сорокин

Редактор И.Горная Техред g.дидык

Корректор М.Самборская

Заказ 2124 Тираж 399 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101 первым входом элемента И, второй вход вход запрета блока соединен с третьим которого соединен с инверсным выходом входом элемента И, выход которого сомажоритарного элемента с порогом п+1, единен с выходом блока.