Имитатор дискретного канала связи

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для статистического моделирования дискретных каналов связи. Цель изобретения - расширение функциональных возможностей за счет моделирования несимметричных M-ичных каналов связи. Поставленная цель достигается введением дополнительно линии задержки, счетчика тактов, генератора тактовых импульсов, второго порогового сумматора, второго элемента И и блока памяти вероятностей. Предложенный имитатор дискретного канала связи позволяет имитировать прохождение дискретной информации в M-ичном несимметричном канале. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (sl)5 G 06 F 15/20

ГОСУДАРСТВЕ ННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4731387/24 (22) 19,06.89 (46) 07.07,91. Бюл, М 25 . (72) А,В. Астанин, B,Ã. Петров, Г.В. Стогов и

П.Г. Тараненко (53) 661.3(088.8) (56) Авторское свидетельство СССР

М 807312, кл. G 06 F 15/20, 1978.

Авторское свидетельство СССР

hb 1562926, кл. G 06 F 15/20, 1988. (54) ИМИТАТОР ДИСКРЕТНОГО КАНАЛА

СВЯЗИ (57) Изобретение относится к вычислительной технике и может быть использовано для

Изобретение относится к вычислительной технике и может быть использовано для статистического моделирования дискретных каналов связи, Цель изобретения — расширение функциональных возможностей за счет моделирования несимметричных m-ичных каналов связи.

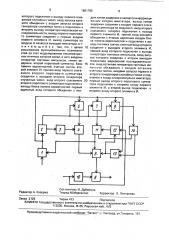

На чертеже приведена схема имитатора дискретного канала связи.

Имитатор дискретного канала связи содержит блок 1 синхронизации, генератор 2 марковской последовательности, блок 3 промежуточной памяти, первый пороговый

4 сумматор, первый генератор 5 случайных чисел, первый элемент И 6, второй генератор 7 случайных чисел, сумматор 8 по модулю m, генератор 9 тактовых импульсов, линию 10 задержки, второй пороговый сумматор 11, блок 12 памяти верятностей, счетчик 13 тактов и второй элоемент И 14.

Имитатор дискретного канала связи работает следующим образом.. Ю 1661788 А1 статистического моделирования дискретных каналов связи, Цель изобретения — расширение функциональных возможностей за счет моделирования несимметричных m-ичных каналов связи. Поставленная цель достигается введением дополнительно линии задержки, счетчика тактов, генератора тактовых импульсов, второго порогового сумматора, второго элемента И и блока памяти вероятностей. Предложенный имитатор дискретного канала связи позволя ет и м ити ровать прохождение дискретной информации в m-ичном несимметричном ка. нале. 1 ил.

На первый вход блока 1 синхронизации поступают внешние синхроимпульсы, сопровождающие информационные символы, поступающие на информационный вход имитатора. Блок 1 вырабатывает сигнал, поступающий на синхровход имитатора и запускающий генераторы 5 и 7 случайных чисел, останавливающий генератор 9 тактовых импульсов, обнуляющий счетчик 13 тактов и запускающий генератор 2 марковской последовательности. После окончания поиска состояния цепи Маркова с второго выхода генератора 2 поступает сигнал, останавливающий генераторы 5 и 7 случайных чисел и запускающий генератор 9 тактовых импульсов. Для определения . значения выходного символа имитатора а по входному символу аь где j=0 m — 1, осуществляются две операции параллельно: формирование сигнала разрешения искажения символа а> и определение числа k такого, что (а + k) mod m=a .

1661788

Первая операция осуществляется с помощью блока 3 промежуточной памяти, порогового сумматора 4 и генератора 5 случайных чисел; С первого выхода генератора 2 на вход блока 3 поступает код адреса ячейки памяти, в которой хранится значение вероятности ошибки символа, соответствующей данному состоянию цепи

Маркова, значение этой вероятности складывается в сумматоре 4 со значением случайного, равномерно распределенного в интервале от 0 до 1 числа, сформированного в генераторе 5. Пороговый сумматор 4 вырабатывает разрешающий сигнал на первый вход элемента И 6 только в том случае, если сумма чисел на его входах не меньше единицы. Этот сигнал представляет собой сигнал переноса старшего разряда сумматора.

При отсутствии разрешающего сигнала элемент И 6 закрыт, и информационный символ, задержанный в линии 10 задержки на время принятия решения, проходит через сумматор 8 по модулю m без искажений на выход имитатора, Вторая операция представляет собой поиск числа и осуществляется параллельно с первой и с помощью генератора 7 случайных чисел, генератора 9 тактовых импульсов, сумматора 11, блока 12 памяти вероятностей, счетчика 13 тактов и элемента И 14.

Блок 12 памяти вероятностей представляет.собой матрицу раэмером m (m-1). в каждой ячейке которой хранится значение вероятностей Ря, определяемых по формуле

k рц,=, Р (а(, 1 )„„д,„/а ) ! =1 где а — значение входного информационного символа;

Р (а (yy) ad a<) — вероятность перехода символа а в символ а(l+р)modm при условии искажения символа аь

Так, если m=8, а =3, четвертая строка матрицы содержит значения следующих вероятностей:

P31=P(84/à3);

Р32= Р(а4/аз)+Р(а5/аз);

Рээ=р(а4/аэ)+Р(ав/аэ)+Р(аб/аэ);

РЗ5=Р(а4/аз)+ ... +Р(а7/аз)+Р(ао/аз);

РЗ7 1.

С выхода блока 12 памяти вероятностей на первый вход порогового сумматора 11 поступает значение вероятности р из ячейки памяти, адрес которой определяется значением входного символа аь поступающего с информационного входа имитатора, и содержимым счетчика 13 тактов, Пороговый

45 сумматор 11 суммирует случайное, равномерно распределенное в интервале от 0 до

1 число с выхода генератора 7 случайных чисел и значение вероятности от блока 12„

На первом выходе сумматора 11 появляется разрешающий сигнал только в случае, когда сумма чисел на его входах не меньше единицы. В противном случае разрешающий потенциал поступает на второй вход элемента И 14 с второго инверсного выхода сумматора 11, Тактовые импульсы с выхода генератора 9 тактовых импульсов, запущенного управляющим сигналом с второго выхода генератора 2 марковской последовательности, через элемент И 14 поступают в счетчик 13 тактов, с выхода которого на второй вход блока 12 памяти вероятностей поступает код номера столбца матрицы вероятностей, причем номер строки определяется значением входного информационного символа ai на весь цикл работы имитатора, Потактовое изменение содержимого счетчика 13 тактов, а следовательно, и номера столбца матрицы вероятностей блока 12 осуществляется до тех пор, пока сумма чисел на входах сумматора 11 меньше единицы. Как только эта сумма становится равной или больше единицы, разрешающий сигнал с второго выхода сумматора 11 прекращает поступать на второй вход элемента И 14, и последний закрывается для прохождения тактовых импульсов в счетчик 13 тактов.

Одновременнц с этим на первом выходе сумматора 11 появляется разрешающий сигнал, подготавливающий блок 1 синхронизации к новому циклу работы имитатора и при наличии разрешающего сигнала на первом входе элемента И 6 разрешающий прохождение через элемент И 6 кода k содержимого счетчика 13 тактов на второй вход сумматора 8 по модулю m. На первый вход сумматора 8 с выхода линии 10 задержки поступает символ а, складывается по модулю m с числом. k и поступает на выход имитатора.

Формула изобретения

Имитатор дискретного канала связи, содержащий генератор марковской последовательности, блок промежуточной памяти, первый пороговый сумматор, первый и второй генераторы случайных чисел, первый элемент И, сумматор по модулю m, причем вход синхроимпульса имитатора соединен с входом запуска генератора марковской последовательности, первый выход которого подключен к адресному входу блока промежуточной памяти, выход которого соединен с входом первого слагаемого первого порогового сумматора, вход второго слагаемого

1661788

Составитель И, Дубинина

Техред М.Моргентал Корректор Э, Лончакова

Редактор А. Козориз

Заказ 2126 Тираж 413 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 которого подключен к выходу первого генератора случайных чисел, вход запуска которого объединен с входом запуска второго генератора случайных чисел и подключен к второму выходу генератора марковской по- 5 следовательности, выход первого noporoeoго сумматора соединен с первым входом первого элемента И, выход сумматора по модулю mявляется выходом имитатора,,о тл и ч а ю шийся тем, что, с целью 10 расширения функциональных возможностей за счет моделирования несимметричных m-ичных каналов связи, в него введены генератор тактовых импульсов, линия задержки, второй пороговый сумматор, блок 15 памяти вероятностей, счетчик тактов, второй элемент И, причем вход первого слагаемого второго порогового сумматора соединен с выходом второго генератора случайных чисел, вход второго слагаемого 20 второго порогового сумматора подключен к выходу блока памяти вероятностей, первый адресный вход которого объединен с входом линии задержки и является информационным входом имитатора, выход линии задержки соединен с входом первого слагаемого сумматора по модулю m, вход второго слагаемого которого подключен к выходу первого элемента И, третий вход которого объединен с вторым адресным входом блока памяти вероятностей и подключен к выходу счетчика тактов, счетный вход которого соединен с выходом второго элемента И, первый вход которого подключен к выходу генератора тактовых импульсов, вход запуска которого соединен с вторым выходом генератора марковской последовательности, вход останова генератора TBKTQBblx импульсов объединен с входом останова счетчика тактов, входами запуска первого и второго генераторов случайных чисел и подключен к входу синхроимпульса имитатора. первый выход второго порогового сумматора подключен к второму входу первого элемента И, а второй выход подключен к второму входу второго элемента И.