Быстродействующий компаратор

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в детекторах, приемниках цифровых сигналов. Цель - повышение помехоустойчивости. Быстродействующий компаратор с ЭСЛ выходами содержит узел 1 сравнения, первый 2 и второй 3 входы устройства, источник 4 питающего напряжения, резисторы 5 и 6, первый 7 и второй 8 выходы устройства, шину 9 синхронизации, источник 10 опорного напряжения, два конденсатора 11 и 12 и два буферных элемента 13 и 14. Блокирование выходов узла 1 сравнения во время режима сравнения с помощью буферных элементов 13 и 14 обеспечивает исключения возможности генерации узла 1 сравнения, чем и достигается поставленная цель. 3 ил.

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫИ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4625035/21 (22) 26.12.88 (46) 07.07.91. Бюл. М 25 (72) Н.К.Ваулин и А.M.Ñèìàãèí (53) 621.374.34 (088.8) (56) Электронная промышленность. 1979, М

7, с,22, рис.1. (54) БЫСТРОДЕЙСТВУЮЩИЙ КОМПАРАТОР (57) Изобретение относится к импульсной технике и может быть использовано в детекторах, приемниках цифровых сигналов.

Цель- повышение помехоустойчивости. Бы. Ж 1661983 А1 стродействующий компаратор с ЭЛС выходами содержит узел 1 сравнения, первый 2 и второй З.входы устройства, источник 4 питающего напряжения, резисторы 5 и 6, первый 7 и второй 8 выходы устройства, шину 9 синхронизации, источник 10 опорного напряжения, два конденсатора 11 и 12 и два буферных элемента 13 и 14. Блокирование выходов узла 1 сравнения во время режима сравнения с помощью буферных элементов 13 и 14 обеспечивает исключение возможности генерации узла 1 сравнения, чем и достигается поставленная цель. 3 ил.

С

С

К

1661983

Изобретение относится к.импульсной. технике и может быть использовано в детекторах. приемниках цифровых сигналов и аналого-цифровых преобразователях, Цель изобретения — повышение помехоустойчивости за счет исключения условий генерации.

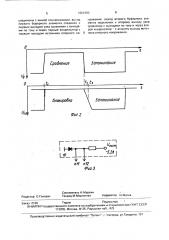

На фиг.1 представлена блок-схема быстродействующего компаратора; на фиг.2— временная диаграмма, поясняющая работу компаратора; на фиг.3 — принципиальная схема источника питания.

Быстродействующий компаратор содержит узел 1 сравнения с выходами по току, первый и второй входы которого являются соответственно первым 2 и вторым 3 входами устройства, источник 4 питающего напряжения, выход которого соединен с первыми выводами первого 5 и второго 6 резисторов, причем второй вывод первого резистора 5 объединен с первым выходом узла 1 сравнения с выходами по току и явля ется первым выходом 7 устройства, второй вывод второго резистора 6 соединен с вторым выходом узла 1 сравнения с выходами по току, является вторым выходом 8 устройства, шина 9 синхронизации устройства подключена к третьему входу узла 1 сравнения с выходами по току, источник 10 опорного напряжения через первый 11 и второй

12 конденсаторы соединен с соответствующими выходами первого 13 и второго 14 буферных элементов и первым 7 и вторым 8 выходами устройства, а входы буферных элементов 13 и 14 объединены и подключены к шине 9 синхронизации.

Компаратор работает следующим образом.

При поступлении синхроимпульсов с шины 9 на третий вход узла 1 сравнения на

его выходах, являющихся выходами 7 и 8 всего устройства, формируются сигналы в виде уровней ЭСЛ логики, причем и ри высоком уровне синхросигнала производится сравнение входных напряжений на входах

2 и 3 (режим сравнения), а при низком— запоминание результата сравнения (режим запоминания).

При поступлении на входы буферных элементов 13 и 14 (переход из режима запоминания в режим сравнения) положительного перепада (момент t1, фиг,3) на выходе буферных элементов 13 и 14 формируются обычные крутые фронты, так как небольшие емкости конденсаторов 11 и 12 (примерно

20-100 пФ) переэаряжаются коллекторными токами выходных транзисторов в узле 1, включенных по схеме эмиттерного повторителя (как во всех логических ЭСЛ элементах). В режиме сравнения (между t> и t:j

55 буферные элементы 13 и 14, соединенные с выходами узла 1 по схеме ПРОВОДНОЕ

ИЛИ, удерживают (блокируют) выходные каскады узла 1 за пределами линейной зоны, исключая положительные обратные связи с выхода узла 1 на его входы.

При поступлении на входы буферных элементов 13 и 14 (переход от сравнения к запоминанию) отрицательного перепада (момент т2, фиг.3) выходные транзисторы узла 1 запираются и конденсаторы 11 и 12 перезаряжаются через резисторы 5 и 6, что вызывает затягивание (задержку тз — t2) отрицательного фронта на выходе буферных элементов 13 и 14 относительно аналогично фронта на входе синхронизации узла 1. При подаче отрицательного фронта синхроимпульс определяется, и на элементе памяти узла 1 фиксируется выходной сигнал узла 1,Этот сигнал остается на его выходах после снятия блокировки (момент ta). Таким образом, в режиме сравнения выходной сигнал. узла 1 не меняется.

Блокирование выходов узла 1 сравнения производится во время режима сравнения потому, что только в этом режиме возможна генерация, Блокирование выходов узла 1 и, следовательно, выходов 7 и 8 устройства (так как они объединены) позволяет простым схемными средствами надежно исключить возможность генерации, При отсутствии блокировки используется очень сложный для широкополосных устройств, к которым относится и быстродействующий компаратор, технологический путь — оптимизация монтажа, введение посеребренных экранов и другие средства, приводящие к уменьшению уровня генерации, а не к ее исключению.

Формула изобретения

Быстродействующий компаратор. содержащий узел сравнения с выходами по току, первый и второй входы которого являются соответственно первым и вторым входами устройства, источник питающего напряжения, выход которого соединен с первыми выводами двух резисторов, второй вывод первого из которых объединен с первым выходом узла сравнения с выходами по току и является первым выходом устройства, второй вывод второго резистора соединен с вторым выходом узла сравнения с выходами по току и является вторым выходом устройства, шина синхронизации устройства подключена к третьему входу узла сравнения с выходами по току, о т л и ч а юшийся тем, что. с целью повышения помехоустойчивости, в него введены источник опорного напряжения, два конденсатора и два буферных элемента. входы которых

1661983 л0 к12

PuzЗ

Составитель Н.Маркин

Техред M.Ìîðãåíòàë Корректор И.Минска

Редактор О.Головач

Заказ 2136 Тираж .Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101 соединены с шиной синхронизации, выход первого буферного элемента соединен с первым выходом узла сравнения с выходами по току и через первый конденсатор с первым выходом источника опорного напряжения, выход второго буферного элемента подключен к второму выходу узла сравнения с выходами по току и через второй конденсатор — к второму выходу источ5 ника опорного напряжения.

l num)

-ХZB