Преобразователь двоично-десятичного кода в двоичный

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для быстрого преобразования десятичных чисел в двоичные. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что в преобразователе, содержащем входной регистр 1, блоки 2 памяти, первый и второй блоки 3, 5 суммирования и промежуточный регистр 4, адресные входы блоков памяти соединены с выходами K старших тетрад подгрупп тетрад регистра 1, а выходы блока 5 суммирования соединены с входами блока 3 суммирования, что обеспечивает умножение на 10<SP POS="POST">K</SP>. 2 ил. 2 табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5Н5 Н 03 M 7/12

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

) л (21) 4406544/24 (22) 08;04.88 (46) 07.07.91. Бюл. Я 25 (72) В,П.Тукаль и А.А.Шостак (53) 681.325 (088.8) (56) Патент США М 4325056, кл. 340-347, 1982.

Авторское свидетельство СССР

М 1569993, 04.04.88, (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА В ДВОИЧНЫЙ (57) Изобретение относится к вычислительной технике и может быть использовано для, Ы „, 1662004 А1 быстрого преобразования десятичных чисел в двоичные. Целью изобретения является повышение быстродействия, Поставленная цель достигается тем, что в преобразователе, содержащем входной регистр 1, блок 2 памяти, первый и второй блоки 3, 5 суммирования и промежуточный регистр 4, адресные входы блоков памяти соединены с выходами К старших тетрад подгрупп тетрад регистра 1, а выходы блока 5 суммирования — с входами блока 3 суммирования, что обеспечивает умножение на 10К, 2 ил.

2 табл.

1662004

Изобретение относится к вычислительной технике и может быть использовано для быстрого преобразования десятичных чисел в двоичные, Целью изобретения является повышение быстродействия.

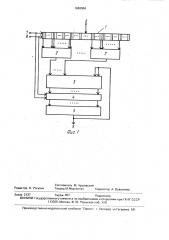

На фиг.1 приведена структурная схема предлагаемого преобразователя двоичнодесятичного кода в двоичный; на фиг.2— и реоб раза ватель 16-разрядного входного кода при К = 1, m = 2, р = 8, Q = 1.

П реобразователь содержит входной регистр 1, блоки 2 памяти, первый блок 3 сум ъ мирования, промежуточный регистр 4, второй блок 5 суммирования, информационный вход 6 устройства, управляющий 7 и тактовый 8 входы преобразователя и выход 9, В блоках 2 памяти по определенным адресам хранятся суммы двоичных эквивалентов К старших тетрад (К = 1,2,...) соответствующей подгруппы тетрад преобразуемого кода, на которые условно разбит регистр 1. Регистр 1 разбит íà m подгрупп (m =) — (, где n — число разрядов и

8К входного кода). Блок памяти может объединять выходы старших тетрад нескольких подгрупп.

Первый блок 3 суммирования осуществляет преобразование (Q + G)-рядного кода в S-рядный, где G — количество единичных оазоядов в двоичном представлении веса

10 /2. Рядность кода, формируемого на к взводах блока 3 суммирования, объясняется тем, что на первую группу входов поступает

m сумм двоичных эквивалентов К старших тетрад подгрупп соответствующих групп, хранимых в блоках 2 памяти, На входы второй группы входов поступает код, сформированный в блоке 5 суммирования и сдвинутый на число разрядов, соответствующее номерам единичных оазоядов в двоичном представлении веса 10 /2. Например, если К = 1, 10 /2 = 5 = 101 и сдвиг

1 осуществляется на один и три разряда.

Сдвиг осуществляется в сторону старших разрядов(сложение сдвинутого кода на один и на три разряда в сторону старших разрядов, равносильно умножению этого кода на десять), Второй блок 5 суммирования производит преобразования S-рядного кода, сформированного на выходе блока 3 суммирования и хранимого в регистре 4, в однорядн ый код.

Этот блок может быть реализован на быстродействующих сумматорах с ускоренным образованием переноса.

Преобразователь работае следующим образом.

Пусть в исходном состоянии в регистре 1 узла хранится двоична-десятичный код преобразуемого числа, а регистр 4 обнулен.

Тогда в первом такте работы устройства осуществляется следующее действие. На выходах блоков 2 памяти образуются значения сумм двоичных эквивалентов старших тетрад подгрупп соответствующих групп, которые образуют Q-разрядный код, поступающий далее на первую группу входов первого блока 3 суммирования. На выходы второй группы входов блока 3 (при К = 1 со сдвигом на один разряд на один вход и на второй со сдвигом на три разряда в сторону его старших разрядов) поступает однорядный код, сформированный в блоке 5 суммирования (в первом такте его значение равно нулю). Далее с помощью блока 3 суммирования (Q + 2)-рядный код преобразуется в

S-рядный, который по приходу второго синхроимпульса с разрешения потенциала на входе 8 устройства записывается B регистр

4. Одновременно с записью информации в регистр 4 по этому же синхроимпульсу происходит сдвиг содержимого регистра 1 на К десятичных разрядов в сторону его старших разрядов, На этом первый такт преобразования заканчивается.

Во втором такте работы устройства одновременно с чтением следующих двоичных эквивалентов из блоков 2 памяти происходит преобразование S-рядного кода в однорядный вторым блоком 5 суммирования, результат этого преобразования подается на вторую группу входов первого блока 3 суммирования. По окончании переходного процесса в блоке 3 и по приходу третьего синхроимпульса с разрешения потенциала на входе 8 устройства результат преобразования записывается в регистр 4, Одновременно с записью информации в регистр 4 по этому же синхроимпульсу происходит сдвиг содержимого регистра 1 на К десятичных разрядов в сторону его старших разрядов.

Аналогичным образом выполняются все последующие такты работы устройства, число которых определяется количеством тетрад в подгруппах каждой группы тетрад.

Меняя количество тетрад в подгруппах можно таким образом регулировать скорость и аппаратурные затраты, необходимые на реализацию устройства преобразования, что является достоинством предлагаемого устройства, Пример. Преобразование двоично-десятичного кода 1001 1000 0111 0110(2)

=9876(1o) в двоичный код. Предполагают, что тетрады регистра 1 образуют одну группу, которая содержит две подгруппы (m = 2), 1662004

Таблица 1 ресные входы блока

Таолица 2 о каждая из которых содержит по две тетрады, Результат на выходе первого блока 3 суммирования формируется в 2-рядном коде(Я =2), Структурная схема такого устройства приведена на фиг,2. В регистре 1 преобразуемого кода указано значение исходного кода. Группа блоков 2 памяти в данном случае может быть объединена в один блок памяти с одной группой выходов, Пример и риведен для такой реализации.

Значение разрядов, подаваемых B i-м такте на адресные входы блока 2 памяти, приведено в табл.1.

Процесс преобразования в устройстве двоично-десятичного кода 1001 1000 0111

0110 в двоичный код приведен в табл,2.

Формула изобретения

Преобразователь двоично-десятичного кода в двоичный, содержащий входной регистр, состоящий из тетрад, объединенных и в m подгрупп (m = ) — (, где n — разрядность

8К входного кода, а К вЂ” целое число); группу из

0 = 4 mK/р блоков памяти, где р — число адресных входов. блока памяти, первый и второй блоки суммирования и промежуточный регистр, информационные входы которого соединены с выходами первого блока

5 суммирования, первая группа входов которого соединена с выходами соответствующих блоков памяти группы, выходы второго блока суммирования являются выходами преобразователя, информационные входы

10 которого соединены с информационными входами входного регистра, вход записи которого соединен с управляющим входом преобразователя и входом сброса и ромежуточного регистра, вход записи которого со15 единен с тактовым входом преобразователя и входом сдвига входного регистра, о т л ич а ю шийся тем, что. с целью повышения быстродействия, в нем адресные входы блока памяти группы соединены с выходами К

20 старших тетрад соответствующих подгрупп входного регистра, выходы второго блока суммирования соединены с вторыми входами первого блока суммирования со сдвигом на R разрядов в сторону старших разрядов, 25 где R — номера единичных разрядов в дво-, ичном представлении веса 10к/2, 1662004

Редактор Н. Рогулич

Заказ 2137 Тираж 457 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

Составитель М. Аршавский

Техред М.Моргентал Корректор А. Осауленко