Устройство для последовательного обнаружения и исправления ошибок

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и передаче данных, может быть использовано для последовательного обнаружения и исправления ошибок. Цель изобретения - расширение области применения за счет обнаружения и исправления ошибок типа смещения. Эта цель достигается путем введения первого, второго, третьего и четвертого триггеров 1.1 - 1.4, первого, второго, третьего, четвертого, пятого и шестого элементов ИЛИ 2.1 - 2.6, первого, второго и третьего элементов 3.1 - 3.3 и элемента 4 запрета, счетчика 5 и соответствующих связей. Устройство может быть использовано в промежуточных и оконечных усилительных станциях систем передачи данных. 1 табл., 1 ил.

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 03 M 13/00

ГосудАРственныЙ кОмитет

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4453419/24 (22) 01.07,88 (46) О?,07.91. Бюл. М 25 (72) А,В,Ткаченко, l0.È.Hèêoëàåâ, С,А.Красиков, В,О.Александров и И.Е,Седов (53) 681.3 (088.8) (56) Авторское свидетельство СССР

N 1568248,,кл. Н 03 M 13/00, 25.11.87, Авторское свидетельство СССР по заявке

N. 4240804/24-24, кл, Н 03 М 13/00, 07.05,87, (54) УСТРОЙСТВО ДЛЯ ПОСЛЕДОВАТЕЛЬНОГО ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ

ОШИБОК ЫЦ, 1662008 А1 (57) Изобретение относится к вычислительной технике и передаче данных, может быть использовано для последовательного обнаружения и исправления ошибок. Цель изобретения — расширение области применения за счет обнаружения и исправления ошибок типа смещения, Эта цель достигается путем введения первого, второго, третьего и четвертого триггеров 1.1-1.4, первого, второго, третьего, четвертого, пятого и шестого элементов

ИЛИ 2.1 — 2.6, первого, второго и третьего элементов 3.1-3.3 и элемента 4 запрета, счетчика 5 и соответствующих связей. Устройство может быть использовано в промежуточных и оконечных усилительных станциях систем передачи данных. 1 ил., 1 табл. оь

iQ

Ю

С)

С)

00 )

1 ъ

1662008 а(0) а(1) а(2) ... a(m — 1), преобразовать в последовательность

0 а(0) 0 а(1) 0 а(2) 0...0 a(m-1) О, (1) где между кодовыми разрядами помещаются по защитному нулевому разряду слева и справа.

Полученная кодовая последовательность имеет длину и = 2m+1. Если в качестве исходного кода используют классическую двоичную систему счисления мощностью

2m, помехоустойчивая система счисления формы (1).задается многочленом

А =, a(S) 2

s =o ($ - !)/г n — (!! - !)/г (s + !)/г

1 при 2 SA $ в(К)2 (2

K =S!2 (s - !)/г — (к — !)/г (в + !)/г

О при 2 >А- 2. e(K) 2 а2 в ="я+г

e (S) Сигналы Е и l(k), с помощью которых обнаруживаются и исправляются ошибки смещения точки пересечения уровня влево— вправо, формируются согласно соотношениям (при k = 2S+1) Е = а(2) Ча(4) Ч „, V a(n-5) V a(n-3); (2)

l(k) = fa(k-2) 8 a(k-1)) V (a(k+1) 3 а (k+2)). (3) Изобретение относится к вычислительной технике и передаче данных, может быть использовано для обнаружения и исправления ошибок.

Целью изобретения является расширение области применения за счет об наружения и исправления ошибок типа смещения.

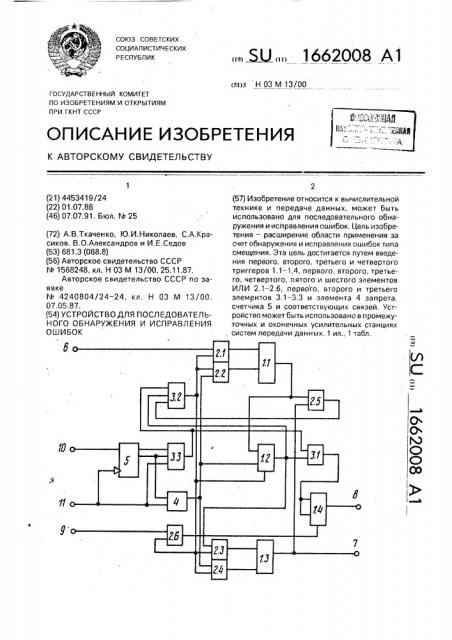

На чертеже представлена схема устройства для последовательного обнаружения и исправления ошибок.

Устройство содержит с первого 1.1 по четвертый 1.4 триггеры, с первого 2,1 по шестой 2,6 элементы ИЛИ, с первого 3.1 по третий 3.3 элементы И, элемент 4 запрета, счетчик 5, информационный вход 6 устройства, информационный выход 7 устройства, контрольный выход 8 устройства, вход 9 сброса устройства, вход 10 установки устройства и тактовый вход 11 устройства.

С целью исправления части ошибок и обнаружения всех ошибок типа смещения предлагают исходную последовательность символов

Исходное состояние счетчика 5 синхроимпульс сдвигает код, 4— отк ыт

Синхооим

Синхроимпульс сдвигает код, 4— отк ыт р

Синхроимпульс контролирует и исправляет код, 4 — закрыт, 3,3— отк ыт

Счетчик 5 устанавливается в исходное состояние импульсом на входе 10 устройст35 ва.

На вход 6 подается кодовая комбинация, а с выхода 7 снимается. Контрольный выход 8 предназначен для выдачи сигнала о наличии ошибки. Если сигнал сбрасыва40 ется автоматически, ошибка исправлена, в противном случае необходимо сбросить триггер 1.4 импульсом на входе 9 сброса, вход 11 используют для подачи синхроимпульсов, каждый второй из которых

45 производит сдвиг кодовой комбинации (табл и ца).

Устройство работает следующим образом, Пусть на вход 6 подается кодовая ком50 бинация согласно комбинации (1), одновременно на вход 11 поступают синхроимпульсы в два раза большей частоты, чем код на вход 6, После записи двух первых символов в триггеры 1.1 и 1.2 про55 изволится проверка наличия "0" в триггере

1.2 — состояние "11", открыты элементы И

3.3 и 3.1, если первый разряд кода в состоянии "1", т.е, произошел переход "1" из второго разряда по формуле (1), элемент И

3.1 выдает ошибку, а так как срабатывание

Триггеры 1.1 — 1.3 предназначень! для прохождения через них кодовой комбинации и ее обработки. Триггер 1.4 — для фиксации ошибки смещения в запрещенный

5 (нулевой) разряд, если ошибка исправляется, импульсом "1" она сбрасывается в нулевое состояние через вход сброса.

Элементы ИЛИ 2.1 — 2,4 обеспечивают объединение сигналов на входы и синхров10 ходы триггеров 1,1 и 1.3. Элементы ИЛИ 2.5, И 3.1 и 3.2 реализуют функции исправления и обнаружения ошибок по формулам (2) и (3).

Элемент ИЛИ 2.6 объединяет автоматический сброс сигнала ошибки нэ триггере 1,4

15 и сброс с входа 9 сброса.

Счетчик 5 и элементы И 3,3 и 4 запрета выполняют функцию управления устройства, они задают режимы работы, представленные в таблице состояния выходов

20 счетчика 5.

1662008 элемента И 3,2 не произойдет, то ошибка не исправлена.

Таким образом, при переходе "1" кода в любой соседний нулевой разряд происходит срабатывание элемента И 3.1, на второй вход которого подается импульс элементом

И 3.3 (таблица).

Исправление устройством кодовой комбинации производится в следующих ситуациях;

Ситуация А 1 0 1,-° - ..1 1 0

a(!) 0 a(! !) a(!) 0 а(! !) Ситуация В 1 0 1- - о;,. 0 1 1 а(!) 0 а(! !) a(i) 0 а(! 1) Очевидно, что "1", перешедшая в "охранный" разряд, находится в соседнем нулевом разряде (ситуация А — в а(! — 1), ситуация  — в а(!)). Такое исправление и роизводит элемент И 3.2. Одновременно он сбрасывает "охранный" разряд в нулевое состояние по единичным импульсам, подаваемым с триггера 1,2 и элемента И 3.3 (табл и ца), Формула изобретения

Устройство для последовательного обнаружения и исправления ошибок, содержащее с первого по четвертый триггеры, с первого по шестой элементы ИЛИ, с первого по третий элементы И, причем выход первого триггера соединен с информационным входом второго триггера и первым входом пятого элемента ИЛИ, выход которого соединен с первым входом второго элемента И, второй вход которого.соединен с выходом третьего элемента И, выход второго триггера соединен с первым входом первого элемента И, вход сброса устройства соединен с первым входом шестого элемента ИЛИ, выход которого соСоставитель А, клюев

Редактор Н. Рогулич Техред М.Моргентал Корректор А. Осауленко

Заказ 2137 Тираж 463 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

\ единен с входом установки е ""0" четвертого триггера, выход которого является контрольным выходом устройства, о т л и ч а ющ е е с я тем, что, с целью расширения области применения за счет обнаружения и исправления ошибок типа смещения, оно содержит элемент запрета и счетчик, причем информационный вход устройства соединен с первым входом первого элемента

ИЛИ, выход которого соединен с информационным входом первого триггера, вход разрешения записи которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с вторыми входами первого и шестого элементов ИЛИ, с первыми входами третьего и четвертого элементов

ИЛИ, входом установки в "0" второго триггера и выходом второго элемента И, третий вход которого соединен с вторым входом третьего элемента ИЛИ и выходом второго триггера, вход разрешения записи которого соединен с вторыми входами второго и четвертого элементов ИЛИ и выходом элемента запрета, управляющий вход которого соединен с первым входом третьего элемента И и выходом первого разряда счетчика, выход второго разряда которого соединен с вторым входом третьего элемента И, третий вход которого соединен с информационным входом элемента запрета, счетным входом счетчика и тактовым входом устройства, вход установки которого соединен с установочным входом счетчика, выходы третьего и четвертого элементов ИЛИ соединены соответственно с информационным входом разрешения записи третьего триггера, выход которого соединен с вторым входом пятого элемента ИЛИ и является информационным выходом устройства, выход третьего элемента И соединен с вторым выходом первого элемента И, выход которого соединен с информационным входом разрешения записи четвертого триггера.