Устройство для цифрового пикового детектирования

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике. Цель изобретения - увеличение быстродействия и точности детектирования. Устройство содержит двухполупериодный выпрямитель 1, блоки 2 и 10 вычитания, пороговые блоки 3 и 12, постоянные запоминающие устройства 4 и 5, перемножители 6 и 7, сумматор 8, регистр 9 памяти и блок 11 сдвига разрядов. Пороговый блок 12 состоит из электронного ключа 13 и порогового элемента 14. Уменьшение количества операций умножения позволяет увеличить быстродействие устройства, а уменьшение влияния цепи формирования постоянной времени спада выходного сигнала устройства на цепь формирования постоянной времени нарастания этого сигнала позволяет увеличить точность детектирования. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (s»s G 01 и 19/04

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4649736/09 (22) 13.02.89 (46) 15.07.91. Бюл. N- 26 (71) Ленинградский электротехнический институт связи им. проф. M.À. Бонч-Бруевича (72) Б.Д. Матюшкин и А,Ю, Виноградов (53) 621.376.23(088.8) (56) IAES, 1984, vol. 32, ЬЬ 5, р. 316 — 327, fig 3. (S4) УСТРОЙСТВО ДЛЯ ЦИФРОВОГО ПИКОВОГО ДЕТЕКТИРОВАНИЯ (57) Изобретение относится к радиотехнике.

Цель изобретения — увеличение быстродействия и точности детектирования. Устройст„„Ы2„„16635б9 А1 во содержит двухполупериодный выпрямитель 1, блоки 2 и 10 вычитания, пороговые блоки 3 и 12, постоянные запоминающие устройства 4 и 5, перемножители 6 и ., сумматор 8, регистр 9 памяти и блок 11 сдвига разрядов. Пороговый блок 12 состоит из электронного ключа 13 и порогового элемента 14, Уменьшение количества операций умножения позволяет увеличить быстродействие устройства. а уменьшение влияния цепи формирования постоянной времени спада выходного сигнала устройства на цепь формирования постоянной времени нарастания этого сигнала позволяет увеличить точность детектирования. 2 ил.

1663569

Изобретение относится к области радиотехники и может быть использовано в радиовещательной технике, технике связи и звукозаписи.

Цель изобретения — увеличение быстродействия и точности детектирования.

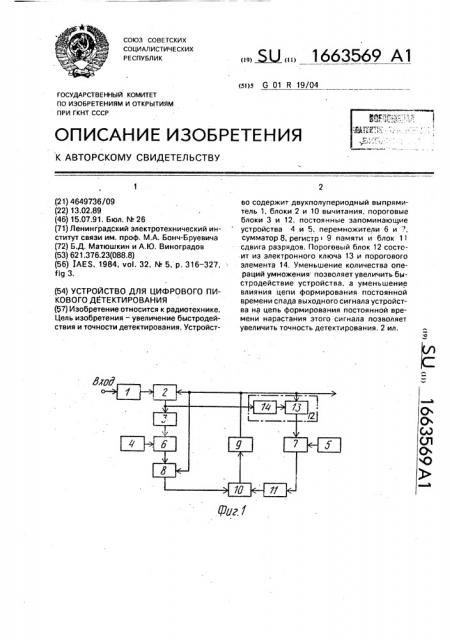

На фиг. 1 приведена структурная электрическая схема устройства для цифрового пикового детектирования; на фиг, 2 — диаграммы сигналов управления.

Устройство содержит двухполупериодный выпрямитель 1, первый блок 2 вычитания, первый пороговый блок 3, первый и второй ПЗУ 4 и 5, первый и второй перемножители 6 и 7, сумматор 8, регистр 9 памяти, второй блок 10 вычитания, блок 11 сдвига разрядов и второй пороговый блок 12, состояший из электронного ключа 13 и порогового элемента 14.

Устройство работает следующим образом, Алгоритм работы устройства описывается следующим разностным уравнением у(n 1)-у(п-1).b, при)х(п) y(n — 1)(1a)

g(n) ((х (и ) j -у (n — 1 ) ) а + у (и — 1 ), при ) x(n)j> у (n — 1) (1б) где х(n), у(n ) — соответственно входной и выходной сигнал на и-м такте; а и b — коэффициенты, записанные соответственно в первом и втором ПЗУ 4 и 5.

С выхода двухполупериодного выпрямителя 1 модуль входного сигнала ) xj n Цбодается на первый вход первого блока 2 вычитания, на второй вход которого с вы хода регистра 9 памяти поступает отсчет у (n-1), вычисленный на предыдущем и-1 такте. Разность величин ) х (n ) (-у(и-1 ) поступает на входы первого и второго пороговых устройств 3 и 12. Выходной сигнал первого порогового устройства 3 в(n),,определяемый соотношением

)(О. при х(п)) — y(n — 1) 0 (2а) (j x(n) Py(n-1), при 1x(n) Py(n — 1)>0 (2б) подается на первый вход первого перемножителя 6, на второй вход которого с выхода первого ПЗУ 4 поступает коэффициент а.

Результат произведения а а(n) подается на первый вход сумматора 8, на второй вход которого с выхода устройства поступает отсчет у (п-1 ). Полученная таким образом сумма а в (п )+у (и-1j с выхода сумматора

8 поступает на первый вход второго блока

10 вычитания.

Пороговый элемент 14 второго пороговогоустройства 12, подключенного к выходу первого блока 2 вычитания, управляет работой электронного ключа 13 по следующему алгоритму;

20

y(n-1j, при )х(п)1-y(n — 1) 0 (За)

Q, при x(n) — y(n — 1)>0 (Зб) где V (n ) — выходной сигнал электронного ключа 13.

Этот сигнал подается на второй вход второго перемножителя 7, на первый вход которого с выхода второго ПЗУ 5 поступает коэффициент Ь. Результат перемножения

V(n) Ь, через блок 11 сдвига разрядов подается на второй вход второго блока 10 вычитания, Выходной сигнал второго блока 10 вычитания является выходным сигналом устройства у(и ) и после его записи в регистре

9 памяти íà n+1 такте выводится на выход устройства

Коэффициент Ь обеспечивает заданную постоянную времени спада выходного сигнала устройства, а коэффициент а — заданную постоянную времени нарастания выходного сигнала. В случае использования предлагаемого устройства в измерителях уровня звуковых сигналов коэффициент Ь должен быть на 4 — 5 порядков меньше коэф25 фициента а. Поэтому во второе ПЗУ 5 записывается коэффициент (Ь 2 )= т.е.

N сдвинутый на Й двоичных разрядов влево.

Конкретное значение М выбирается исходя из разрядности второго перемножителя 7

30 динамического диапазона. возможных значений коэффициента Ь и требуемой точности воспроизведения заданной постоянной времени спада. Блок 11 сдвига.разрядов осуществляет сдвиг выходного сигнала вто35 рого перемножителя 7 V(n j(2 Ь) íà N разрядов вправо, т.е. на втором входе второго блока 10 вычитания формируется сигнал

V (n) b.

Постоянные времени нарастания и спа40 да выходного сигнала аналогичны постоянным времени заряда и разряда в аналоговом пиковом детекторе.

Синхронизация работы устройства осуществляется под воздействием микроко45 манд управления, приведенных на фиг, 2, при реализации устройства на микросхемах серии 1802, при этом F1 — запуск двухполупериодного выпрямителя 1; F2 — запуск первого блока 2 вычитания; F3 — запуск первого

50 и второго пороговых устройств 3 и 12; F4— запуск электронного ключа 13; F5 — запуск первого и второго перемножителей 6 и 7; F6 — запуск сумматора 8 и блока сдвига разрядов 11; F7 — запуск второго блока 10 вычита55 ния; F8 и F9 — соответственно запись и считывание состояния регистра 9 памяти.

Уменьшение количества операций умножения с двух до одной позволило увеличить быстродействие устройства, а уменьшенное влияние цепи формирования постоянной времени спада выходного сиг1663569

ЯЮ

80&m

Фиг 2

Составитель А. Осипович

Техред М.Моргентал Корректор Л. бескид

Редактор О. Спесивых

Заказ 2264 Тираж 417 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Ъ нала устройства на цепь формирования постоянной времени нарастания этого сигнала позволило увеличить точность детектирования. 5

Формула изобретения

Устройство для цифрового пикового детектирования, содержащее последовательно соединенные двухполупериодный выпрямитель, первый блок вычитания, пер- 10 вый пороговый блок, первый перемножитель, сумматор, второй блок вычитания и регистр памяти, выход которого подключен к второму входу первого блока вычитания, и к второму входу сумматора, первое постоян- 15 ное запоминающее устройство, выход которого соединен с вторым входом первого

1 перемножителя, последовательно соединенные второе запоминающее устройство, второй перемножитель и блок сдвига разрядов, выход которого подключен к второму входу второго блока вычитания, о т л и ч аю щ е е с я тем, что, с целью увеличения быстродействия и точности детектирования, введен второй пороговый блок, состоящий из порогового элемента и электронного ключа, вход и выход которого подключены соответственно к выходу регистра памяти и к второму входу второго перемножителя, а вход и выход порогового элемента соединены соответственно с выходом первого блока вычитания и с входом управления электронного ключа,