Устройство для контроля блоков памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для функционального контроля оперативных запоминающих устройств и определения области их устойчивой работы. Целью изобретения является повышение достоверности контроля за счет более полной проверки адресной части блока памяти. Устройство содержит блок 1 задания начальных условий и анализа результата, первый 2, второй 10 и третий 7 регистры данных, первый 3 и второй 11 регистры адреса, блок 4 задания частот, первый 5, второй 13 и третий 34 управляющие триггеры,триггер 6 записи - чтения, блок 8 формирования временных диаграмм, триггер 9 ошибки, элемент НЕ 12, первый 14 и второй 15 цифроаналоговые преобразователи, элемент 16 задержки, первый 17 и второй 18 элементы И - НЕ, регистр 20 результата, блок 21 сравнения, вспомогательный регистр 22 результата, первый 23 и второй 35 элементы И, счетчик 32, мультиплексор 33. Устройство позволяет формировать тестовые последовательности программы контроля с помощью ЭВМ. Повышение достоверности контроля адресной части блока памяти достигается за счет того, что переключение адреса осуществляется в каждом такте работы проверяемого блока памяти. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 О 11 С 29 00

ГОСУДАРСТВЕ ННЫ И КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ щггц;ц т;- = (61) 1569903 (21) 4693966/24 (22) 04.04,89 (46) 15.07,91. Бюл ¹26 (71) Московский энергетический институт (72) Ю.В.Сычев и Д,И,Дудукин (53) 681.327,6 (088.8) (56) Авторское свидетельство СССР

К 1569903, кл. 6 11 С 29/00, 1988. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано для функционального контроля оперативных запоминающих устройств и определения области их устойчивой работы, Целью изобретения я вляется повышение достоверности контроля за счет более полной проверки адресной части блока памяти.

Устройство содержит блок 1 задания начальных условий и анализа результата, пер Ы „1663627 А2 вый 2, второй 10 и третий 7 регистры данных, первый 3 и второй 11 регистры адреса, блок 4 задания частот, первый 5, второй 13 и третий 34 управляющие триггеры, триггер

6 записи-чтения, блок 8 формирования временных диаграмм, триггер 9 ошибки, элемент НЕ 12, первый 14 и второй 15 цифро-аналоговые преобразователи, элемент 16 задержки, первый 17 и второй 18 элементы И вЂ” НЕ, регистр 20 результата, блок 21 сравнения, вспомогательный регистр 22 результата, первый 23 и второй 35 элементы И, счетчик 32, мультиплексор 33.

Устройство позволяет формировать тестовые последовательности программы контроля с помощью Э ВМ. Повышение достоверности контроля адресной части блока памяти достигается за счет того, что пере кл ючение адреса осуществл я ется в каждом такте работы проверяемого блока памяти. 1 ил.

1663627

15

55

Изобретение относится к вычислительной технике и может быть использовано для функционального контроля оперативных запоминающих устройств и определения области их устойчивой работы, 5

Цель изобретения — повышение достоверности контроля за счет более полной проверки адресной части блока памяти.

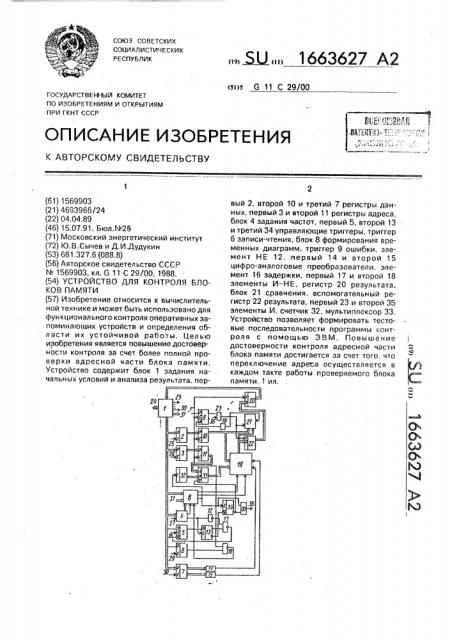

На чертеже приведена функциональная схема устройства для контроля полупроводниковой памяти.

Устройство содержит блок 1 задания начальных условий и анализа результата, первый регистр 2 данных, первый регистр 3 адреса, блок 4 задания частот,.первый управляющий триггер 5, триггер 6 записи чтения, третий 7. регистр данных, блок 8 формирования временных диаграмм, триггер 9 ошибки, второй 10 регистр данных, второй 11 регистр адреса, элемент НЕ 12, второй 13 управляющий триггер, первый 14 и второй 15 цифроаналоговые преобразователи,.элемент задержки 16, первый 17 и второй 18 элементы И вЂ” НЕ, проверяемый блок 19 памяти, регистр 20 результата, блок

21 сравнения, вспомогательный регистр 22 результата, первый элемент И 23, информационные входы-выходы 24 устройства, управляющие выходы 25 — 31 блока 1, счетчик

32, мультиплексор 33, третий управляющий триггер 34, второй элемент И 35 и его выход

36, Устройство для контроля блоков памяти работает следующим образом.

Устройство представляет собой адаптер, подключаемый, например, к интерфейсу ЭВМ типа "ДВК" или "Электроника-60".

Адаптер содержит программируемые регистры, в которые информация может записываться со стороны ЭВМ. Один из регистров предназначен для чтения информации из

ЭВМ, В него заносятся результаты контроля. При этом старшие разряды адреса пред- назначаются для выбора адаптера, а младшие для выбора регистра внутри адаптера.

Формирование тестовых последовательностей в устройстве осуществляется программным способом с помощью ЭВМ.

Перед началом работы устройства ЭВМ загружает регистры 2 и 3 кодами данных и адресов. В триггер 6 записывается код режима работы проверяемой памяти (первоначальная команда — "Запись" ). В регистр 7 записывается код напряжений питания, поступающих на клеммы питания полупроводниковой памяти. В регистры блока формирования временных диаграмм записываются коды значений переднего и заднего фронтов сигналов, управляющих работой проверяемой памяти. Триггеры 5, 9, 13 и 34 устанавливаются в исходное состояние (цепи сброса не показаны), В блок 4 задания частот записывается значение кода цикла записи чтения проверяемой памяти.

По команде из ЭВМ триггер 5 устанавливается в единичное состояние, что приводит к тому, что по сигналу с блока задания частот триггер 13 изменяет свое состояние из "0" в "1". По сигналу с выхода триггера 13 в регистры 10 и 11 переписывается содержимое регистров 2 и 3 и начинается контроль блока памяти. На выходе элемента 17 вырабатывается сигнал "0", который сбрасывает триггер 5 в исходное состояние, Первый импульс строба считывания проходит на вход элемента 23, осуществляя контроль записанной в блок 19 памяти. По заднему импульсу считывания триггер 34 изменяет свое состояние из "1" на инверсном выходе на "0", обеспечивая подключение к адресным входам ячейки 19 памяти выходы счетчика 32 и запрещая в следующем такте прохождение импульса строба считывания на вход элемента 23. В этом такте информация считывается из блока 19 памяти без ее сравнения. Второй импульс строба считывания переключает триггер 34 в исходное состояние. обеспечивая считывание информации из проверяемой ячейки с ее сравнением. Исходное состояние счетчика

32 не имеет значения, так как он должен только обеспечить изменение адреса, поступающего в проверяемую блока 19 памяти.

Сравнение считываемой и записанной в блок памяти инфоромации осуществляется блоком 21 сравнения, В случае несравнения записанной и считанной информации по сигналу 36 с выхода элемента И в регистр 22 записывается код считываемого числа, Во время контроля блока памяти ЭВМ перезагружает первый 2 регистр данных и первый 3 регистр адреса и анализирует состояние регистра 20 результата контроля.

Предлагаемое устройство позволяет формировать тестовые последовательности и программы контроля с помощью ЭВМ, обеспечивая контроль блоков памяти на их предельной (рабочей) частоте.

Формула изобретения

Устройство для контроля блоков памяти по авт. св. М 1569903, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, в него введены счетчик, мультиплексор, третий управляющий триггер, второй элемент И, выход которого соединен с вторым входом первого элемента И, третий выход блока формирования времени диаг1663627

Составитель М. Лапушкин

Редактор Л. Пчолинская Техред М,Моргентал Корректор M. Кучерявая

Заказ 2267 Тираж 346 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород. ул.Гагарина, 101 рамм соединен с входом синхрониэаци счетчика, с входом синхронизации третьего управляющего триггера, и с первым входом второго элемента И, второй вход которого соединен с управляющим входом мультиплексора и с инверсным выходом третьего управляющего триггера, установочный вход которого соединен с инверсным выходом второго управляющего триггера, выходы второго регистра адреса соединены с информационными входами первой группы мультиплексора, информационные входы

5 второй группы которого соединены с выходами счетчика, информационные выходы мультиплексора являются адресными выходами устройства.