Устройство для контроля времени опережения синхронизатора

Иллюстрации

Показать всеРеферат

Изобретение относится к электронике. Цель изобретения - расширение функциональных возможностей за счет обеспечения контроля времени опережения при безвахтенном режиме обслуживания. При срабатывании синхронизатора 1 одновибраторы 2 и 3 формируют импульсы, длительности которых равны минимально и максимально допустимым значениям времени опережения синхронизатора. Блок 4 формирования напряжения биений срабатывает в момент равенства напряжений сети и генератора. Цель достигнута в результате специального выполнения логического дешифратора 6, который определяет находится ли импульс, вырабатываемый блоком 4, в пределах между минимально и максимально допустимыми значениями времени опережения синхронизатора. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 02 J 3/40

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4665189/07 (22) 23,03.89 (46) 15.07.91. Бюл. М 26 (71) Ленинградский институт водного транспорта (72) Н.В. Широков, В.А, Родин и Г,А. Широкова (53) 621.316.729 (088.8) (56) Авторское свидетельство СССР

М 1554071, кл. Н 02 1 3/40, 1988, Авторское свидетельство СССР

М 1536477, кл, Н 02 J 3/40, 1988. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ВРЕМЕНИ ОПЕРЕЖЕНИЯ СИНХРОНИЗАТОРА (57) Изобретение относится к электронике.

Цель изобретения — расширение функциоИзобретение относится к электротехнике и может быть использовано для диагностирования синхронизатора с постоянным временем опережения, Целью изобретения является расширение функциональных возможностей устрой- ства за счет обеспечения контроля времени опережения синхронизатора при безвахтенном режиме обслуживания.

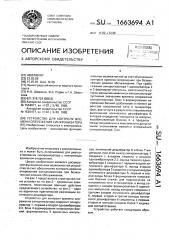

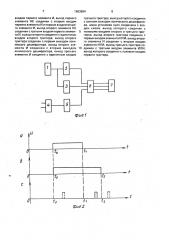

На фиг.1 представлена структурная схема устройстза; на фиг.2 — временные зависимости, поясняющие принцип действия предлагаемого устройства; на фиг.3 — один из вариантов практической реализации логического дешифрэтора.

Устройство для контроля времени опережения синхронизатора содержит синхронизатор 1, первый и второй одновибраторы

2,3, блок 4 формирования напряжения биений, формирователь 5 единичных импуль„,. Ы„„1663694 А1 нальных возможностей за счет обеспечения контроля времени опережения при безвахтенном режиме обслуживания. При срабатывании синхронизатора 1 одновибаторы 2 и 3 формируют импульсы, длительности которых равны минимально и максимально допустимым значениям времени опережения синхронизатора. Блок 4 формирования напряжения биений срабатывает в момент равенства напряжений сети и генератора, Цель достигнута в результате специального выполнения логического дешифратора 6. который определяет находится ли импульс, вырабатываемый блоком 4, в пределах между минимально и максимально допустимыми значениями времени опережения синхронизатора. 3 ил. сов, логический дешифратор 6 и блок 7 индикации, при этом выход синхронизатора 1 соединен с входами первого и второго одновибраторов 2;3, выход первого одновибратора 2 соединен с первым входом логического дешифратора 6, выход второго одновибратора 3 соединен с вторым входом логического дешифратора 6, первый и второй входы блока 4 формирования напряжения биений служат для подключения на напряжение сети и генератора, а выход соединен с входом формирователя 5 единичных импульсов, выход которого соединен с третьим входом логического дешифратора

6, первый, второй и третий выходы логического дешифратора 6 соединены с первым, вторым и третьим входами блока 7 индикации соответственно, Устройство работает следующим образом.

1663694

В момент срабатывания синхронизатора 1 на его выходе формируется сигнал логической единицы, который поступает на входы первого и второго одновибраторов

2,3. На выходе первого одновибратора 2 формируется сигнал логической единицы длительностью, равной минимально допустимой величине времени опережения синхронизатора (фиг.2а). На выходе второго одновибратора 3 формируется сигнал логической единицы длительностью, равной . максимально допустимой величине времени опережения синхронизатора (фиг.2б).

Сигналы логической единицы с выходов первого и второго одновибраторов 2,3 поступают на первый и второй входы логического дешифратора 6 соответственно. На первый и второй входы 4 блока формирования напряжения биений поступают сигналы, пропорциональные напряжениям сети и генератора. На его выходе формируется сигнал в виде напряжения, величина которого пропорциональна разности фаз напряжений сети и генератора, которое подается на вход формирователя 5 единичных импульсов. На выходе формирователя 5 единичных импульсов появляется единичный импульс, когда разность фаз напряжений сети и генератора равна нулю (фиг.2с), Этот сигнал поступает на третий вход логического дешифратора 6, который определяет в какой из интервалов времени (to, t1), (t1, ) или позже, чем t2 (фиг.2) произошло совпадение фаз напряжений генератора и сети и был сформирован единичный импульс на выходе формирователя 5. Если совпадением фаз напряжений сети и генератора произошлб в интервале (то, t>), то на третьем выходе логического дешифратора 6 появляется сигнал логической единицы и поступает на третий вход блока 7 индикации, который представляет информацию обслуживающему персоналу о том, что время опережения синхронизатора меньше нормы, Если совпадение фаз напряжений сети и генератора произошло в интервале времени (ty, t.„ ), то на втором выходе логического дешифратора

6 появится единичный сигнал. поступит на второй вход блока 7 индикации, который представит информацию о том, что время опережения синхронизатора в норме, Если же совпадение фаз напряжений сети и генератора произойдет позже, чем в момент времени сг,то на первом выходе логического дешифратора 6 появится сигнал логической единицы, поступит на первый вход блока 7 индикации, который предоставит обслуживающему персоналу информацию о том, что время опережения синхронизатора больше нормы.

ИЛИ 16, шину 17 установки нуля и ключ 18, причем первый вход логического дешифра10 тора соединен с единичным входом первого

25 второго элемента И 12, выход второго эле. мента НЕ 13 соединен с третьим входом

Логический дешифратор 6; один из вариантов практической реализации которого представлен на фиг.3, содержит первый триггер 8, первый элемент И 9, второй тригrep 10, первый элемент НЕ 11, второй элемент И 12, второй элемент НЕ 13, третий элемент И 14, третий триггер 15, элемент триггера 8, входом первого элемента НЕ 11 и третьим входом третьего элемента И 14, второй вход логического дешифратора соединен с входом второго элемента НЕ 13, третьим входом второго элемента И 12 и первым входом третьего элемента И 14, третий вход логического дешифратора соединен с четвертым входом первого элемента И

9, вторым входом второго элемента И 12, вторым входом третьего элемента И 14, выход пеового триггера 8 соединен с первым входом первого элемента И 9, выход первого элемента НЕ 11 соединен с вторым входом первого элемента И 9 и первым входом первого элемента И 9, выход которого соединен с единичным входом второго триггера 10, выход второго триггера 10 соединен с первым выходом логического дешифратора, выход второго элемента И 12 соединен с вторым выходом логического дешифратора, выход третьего элемента И 14 соединен с единичным входом третьего триггера 15, выход которого соединен с третьим выходом. логического дешифратора, шина 17 установки нуля соединена с входом ключа 18, выход которого соединен с нулевыми входами второго и третьего триггеров 10, 15, выход второго триггера 10 соединен с первым входом элемента ИЛИ 16, выход второго элемента

И 12 соединен с вторым входом элемента

ИЛИ 16, выход третьего триггера 15 соединен с третьим входом элемента ИЛИ 16, выход которого соединен с нулевым входом первого триггера 8.

Логический дешифратор 6 работает следующим образом.

В момент срабатывания синхронизатора на первый и второй входы логического дешифратора 6 поступают сигналы логической единицы. С первого входа логического дешифратора 6 сигнал логической единицы поступает на единичный вход первого триггера 8 и устанавливает его в единичное состояние. При этом на его выходе фиксируется сигнал логической единицы, который поступает на первый вход первого элемента И 9, Сигнал логической единицы с первого входа логического дешифратора 6

1663694

20 поступает на третий вход третьего элемента

И 14 и на вход первого элемента НЕ 11. На выходе первого элемента НЕ 11 появляется сигнал логического нуля и поступает на второй вход первого элемента И 9 и первый вход второго элемента И 12. Сигнал логической единицы с второго входа логического дешифратора 6 поступает на вход второго элемента НЕ 13 и на третий вход второго элемента И 12 и первый вход третьего элемента И 14, На выходе второго элемента НЕ

13 появляется сигнал логического нуля и поступает на третий вход первого элемента

И 9. Если в момент времени (то, t<) на третий вход логического дешифратора 6 будет подан единичный импульс, то он поступит на четвертый вход первого элемента И 9, второй вход второ о элемента И 12 и второй вход третьего элемента И 14. При этом на выходе первого элемента И 9 будет сигнал логического нуля, так как на его втором и третьем входах сигнал логического нуля, На выходе второго элемента И 12 — логический нуль, так как на его первом входе — логический нуль, На выходе третьего элемента И

14 — сигнал логической единицы, так как на всех трех его входах — сигнал логической единицы. Сигнал логической единицы с выхода третьего элемента И 14 поступает на единичный вход третьего триггера 15 и устанавливает его в единичное состояние, на выходе логического дешифратора 6 фиксирован сигнал логической единицы. Если единичный импульс на третий вход логического дешифратора 6 поступит в момент времени (то, ), то на первом входе логического дешифратора 6 уже будет логический нуль, на выходе первого элемента НЕ 11— логическая единица, на всех трех входах второго И 12 — сигнал логической единицы, а значит,и на его выходе (втором выходе логического дешифратора 6) — единичный сигнал. На третьем входе третьего элемента

И 14 — логический нуль, а значит,и íà его выходе — логический нуль. На третьем входе первого элемента И 9 логический нуль, а значит,и на его выходе — логический нуль.

Если единичный импульс поступит на третий вход логического дешифратора в момент времени позже, чем tz, то на первом и втором входах логического дешифратора— сигнал логического нуля, на выходах первого и второго элементов НЕ 11 и 13 — сигнал логической единицы, на всех четырех входах первого элемента И 9 — единичный сигнал, а следовательно, и на его выходе— сигнал логической единицы, В этом случае на выходах второго и третьего элементов И

12, 14 логический нуль. Сигнал логической единицы с выхода первого элемента И 9

55 поступает на единичный вход второго триггера 10 и устанавливает его в единичное состояние. При этом на первом выходе логического дешифратора появляется сигнал логической единицы. После того, как на первом, втором или третьем выходе логического дешифратора 6 появится сигнал логической единицы, он поступит на соответствующий вход элемента ИЛИ 16, с выхода которого поступит на вход установки нуля первого триггера 8, установит его в исходное состояние. Если время опережения синхронизатора отклонилось от заданного значения, оператор замкнет ключ 18, при этом сигнал логической единицы с шины установки нуля 17 поступит на нулевые входы второго и третьего триггеров 10, 15.

После размыкания ключа 18 логический дешифратор 6 вновь готов к работе.

Формула изобретения

Устройство для контроля времени опережения синхронизатора, содержащее блок формирования напряжения биений с входами для подключения на напряжение сети и генератора, выход которого соединен с входом формирователя прямоугольных импульсов, первый и второй одновибраторы с входами для подключения к выходу синхронизатора, индикатор, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства, за счет обеспечения контроля времени опережения синхронизатора при безвахтенном режиме обслуживания, дополнительно введен логический дешифратор, причем выходы первого и второго одновибраторов соединены с первым и вторым входами логического дешифратора соответственно, выход формирователя прямоугольных импульсов соединен с третьим входом логического дешифратора, первый, второй и третий выходы логического дешифратора соединены с первым, вторым и третьим входами индикатора соответственно, при этом логический дешифратор содержит три элемента И, три триггера, два элемента НЕ, элемент ИЛИ, шину установки нуля и ключ, причем первый вход логического дешифратора соединен с единичным входом первого триггера, входом первого элемента НЕ и третьим входом третьего элемента И, второй вход логического дешифратора соединен с входом второго элемента НЕ, третьим входом второго элемента И и первым входом третьего элемента И, третий вход логического дешифратора соединен с четвертым входом первого элемента И, вторым входом второго элемента И, вторым входом третьего элемента И, выход первого триггера соединен с первым

1663694 входом первого элемента И, выход первого элемента НЕ соединен с вторым входом первого элемента И и первым входом второго элемента И, выход второго элемента НЕ соединен с третьим входом первого элемента И, выход которого соединен с единичным входом второго триггера, выход второго триггера соединен с первым выходом логического дешифратора, выход второго элемента И соединен с вторым выходом логического дешифратора, выход третьего элемента И соединен с единичным входом третьего триггера, выход которбго соединен с третьим выходом логического дешифратора, шина установки нуля соединена с входом ключа, выход которого соединен с

5 нулевыми входами второго и третьего триггеров, выход второго триггера соединен с первым входом элемента ИЛИ, выход второго элемента И соединен с вторым входом элемента ИЛИ, выход третьего триггера со10 единен с третьим входом элемента ИЛИ, выход которого соединен с нулевым входом первого триггера, 1663694 и

Ouzel

Составитель К. Фотина .

Редактор М. 8асильева Техред М.Моргентал Корректор Т. Колб

Заказ 2270 Тираж 333 Подписное

ВНИИПИ Гос ударственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5 роизводственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101