Устройство сравнения частоты и фазы

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и может быть использовано в поисковых и адаптивных системах автоподстройки частоты. Целью изобретения является уменьшение времени восстановления выходного сигнала при пропадании входного сигнала. Устройство сравнения частоты и фазы содержит элемент индикации 1, частотный детектор 2, фазовый детектор, состоящий из триггера 3, коммутируемый элемент 4 на элементе ИЛИ, фильтр 5 нижних частот. Частотный детектор 2 содержит блок 6 задержки, элемент И 7, триггер 8. При пропадании входного сигнала выходной сигнал не выходит из рабочей зоны, а с приходом следующего входного сигнала обеспечивается быстрый переход к реальному управляющему потенциалу на выходе фильтра 5 нижних частот, тем самым обеспечивается устойчивость и надежность устройства. Введение дополнительного канала, образованного блоком 6 задержки, элементом И 7 и триггером 8, повышает точность процесса индикации синхронизма, реализуемого при помощи порогового блока 10, подключенного к выходу фильтра 5 через резистор 12, к общей шине - через ключ 9, управляемый с выхода триггера 8. 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 03 0 13/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ. (21) 4754730/09 (22) 25.09.89 (46) 23.07.91. Бюл; N 27 (71) Научно-исследовательский институт телевизионной техники "Электрон" (72) В.Т.Басий. В.А.Лавров и В.А.Халин (53) 621.376,255(088.8) (56) Патент CLUA М 3478178, кл. Н 02 К 17/20, 11.11.69. (54) УСТРОЙСТВО СРАВНЕНИЯ ЧАСТОТЫ

И ФАЗЫ (57) Изобретение. относится к радиотехнике и может быть использовано в поисковых- и адаптивных системах автоподстройки частоты. Целью изобретения является. уменьшение времени восстановления выходного сигнала при пропадании входного сигнала.

Устройство сравнения частоты и фазы содержит элемент индикации 1, частотный де„,5U, 1665496 А1 тектор 2, фазовый детектор, состоящий.из триггера 3, кбммутируемый элемент 4 на элементе ИЛИ, фильтр 5 нижних частот. Частотный детектор 2 содержит блок 6 задержки, элемент И 7, триггер 8. При пропадании входного сигнала выходной сигнал не выходит из рабочей эоны, а с приходом следующего входного сигнала обеспечивается быстрый переход к реальному управляющему потенциалу на выходе фильтра 5 нижних частот, тем самым обеспечивается устойчивость и надежность устройства. Введение дополнительного канала, образованного блоком 6 задержки, элементом И 7 и триггером 8, повышает точность процесса индикации синхронизма, реализуемого при помощи порогового блока 10, подключенного к выходу фильтра 5 через резистор 12, а к общей шине — через ключ 9, управляемый с выхода триггера 8. 1 э.п. ф-лы, 2 ил.

1665496

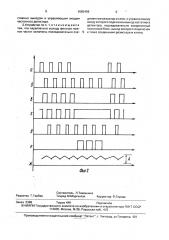

Изобретение относится к радиотехнике и мажет быть использовано в поисковых и адаптивных системах автоподстройки частоты, Целью изобретения является уменьшение времени восстановления выходного сигнала при пропадании входного сигнала, На фиг. 1 приведена структурная электрическая схема устройства сравнения частоты и фазы; на фиг. 2 — временные диаграммы в соответствующих точках схемы.

Устройс во сравнения частоты и фазы содержит элемент 1 индикации, частотный детектор 2, фазовый детектор, состоящий из триггера 3, коммутирующий элемент 4 на элементе ИЛИ, фильтр 5 нижних частот, Частотный детектор 2 содержит блок 6 задер жки и элемент И, прп этом блок 6 задержки

И 1, триггер Ь составляют частотный детектор 2, Кроме того, устройс во содержит ключ

9, пороговое устройство 10, индикатор 11, резистор 12, установленный вход триггера

3 выполнен динамическим, реагирующим на спад входного сигнала.

Устройство работает следующим образом.

Входной (фиг. 2,а) и опорный (фиг,2,б) сигналы поступают соответственно на счетный и установочный входы триггера 3. Входы выполнены динамическими и триггер 3 срабатывает по спаду поступающих сигналов. На инвертирующем выходе триггера 3 (фиг. 2,г} при опрокидывании его входным сигналом запрещающий потенциал закрывает элемент И 7 и опорный сигнал не проходит на вход триггера 8, в результате чего триггер 8 не опрокидывается. По заднему фронту (спаду) опорного сигнала опрокидывается триггер 3 и полученный (фиг. 2,в) "фазовый" импульс проходит через элемент

ИЛИ 4 и суммируется фильтром 5 (фиг, 2,ж).

При пропадании входного сигнала триггер 3 не опрокидывается и с его инвертирующего выхода на элементе И 7 появляется разрешающий потенциал. С приходом опорного сигнала он проходит чеоез эле-. мент И 7 и опрокидывает по N-входу триггера

8, а задержанный блоком 6 опорный сигнал (фиг. 2,д) возвращает триггер 8 в исходное состояние. Сформированный триггером 8 (фиг, 2,е) фазовый импульс через элемент

ИЛИ 4 поступает на фильтр 5, компенсируя тем самым пропадание входного сигнала.

Это позволяет сохранять уровень выходного сигнала на выходе фильтра 5 в зоне А (фиг, 2,ж) устойчивой работы.

Таким образом, при пропадании входного сигнала выходной сигнал не выходит из рабочей зоны и с приходом следующего входного сигнала обеспечивается быстрый

50 переход к реальному управляющему потенциалу на выходе фильтра нижних частот, тем самым обеспечивается устойчивость и соответственно надежность устройства, Следует заметить, что введение дополнительного канала, образованного блоком задержки, элементом И и триггером, повышает точность процесса индикации синхронизма. реализуемого, например, при помощи порогового устройства 10, подключенного к выходу фильтра 5 через резистор

12 и к общей шине через ключ 9, управляемый с выхода триггера 8.

При наличии входных сигналов и достижении на выходе фильтра 5 соответствующего уровня срабатывает пороговое устройство 10 и включают элемент 1 индикации. При отсутствии входных сигналов nocTóïëåHèå соответствующего уровня сигнала с фильтра 5 перекрывается ключом

9, Соответственно происходит "мигание" индикатора 11, индицируя пропадание сигнала на входе дискриминатора, т.е. наличие

"ложного" синхронизма, что повышает информативность индикации. Элементы схемы выполнены по типовых логических элементах с аналогичными наименованиями.

Блок задержки может быть выполнен как на элементах задержки, так и схемно (практически авторы использовали структуру схемы, аналогичную структуре источника опорного сигнала, и выполнили блок задержки последовательно, соединив генератор, счетчик и дешифратор, подав на установочный вход счетчика опорный сигнал (не показано), Формула изобретения

1. Устройство сравнения частоты и фазы, содержащее фазовый детектор, один вход которого является входом устройства сравнения частоты и фазы, входом опорного сигнала которого является другой вход фазового детектора, выход которого через коммутируемый элемент подключен к входу фильтра нижних частот, и вход частотного детектора, выход которого подключен к второму входу коммутируемого элемента, при этом частотный детектор состоит иэ блока задержки, элемента И и триггера, о т л и «аю щ е е с я тем, что. с целью уменьшения времени восстановления выходного сигнала, фазовый детектор выполнен в виде триггера, инверсный выход которого подключен

55 к управляющему входу частотного детектора, входом которого являются вход блока задержки и первый вход элемента И, выходы блока задержки и элемента И подключены к входам триггера, выход которого и второй вход элемента И являются соответ6

1665496

Составитель Л.Тимошина

Техред М.Моргентал Корректор В.Гирняк

Редактор Г.Гербер

Заказ 2398 Тираж 449 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r Ужгород, ул.Гагарина, 101 ственно выходом и управляющим входом частотного детектора.

2.Устройство по и. 1, о т л и ч а ю щ е е с я тем, что параллельно выходу фильтра нижних частот включены последовательно соединенные резистор и ключ, куправляющему входу которого подключен выход частотного детектора, последовательно соединенный поооговый блок, выход которого подключен

5 к точке соединения резистора и ключа,