Устройство для асинхронного переприема дельта- модулированного сигнала

Иллюстрации

Показать всеРеферат

Изобретение относится к технике связи и вычислительной технике. Его использование в цифровых системах передачи позволяет повысить точность устройства за счет нерегулярной коррекции скорости передачи дельта - модулированного сигнала. Устройство содержит триггеры 1, 2 задержки, счетные триггеры 5, 6, решающий блок 8, элемент 9 НЕ, электронный переключатель 11, ключевые элементы 12, 13, элемент 14 ИЛИ и регенератор 15. Благодаря введению триггеров 3, 4 задержки, блока 7 выделения серий паузных комбинаций и элемента 10 НЕ в устройстве обеспечивается выравнивание скоростей не с разностной частотой, а в случайные моменты времени при появлении паузных комбинаций символов 010101 или 101010. 1 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

/ (st)s Н 03 M 7/32,13/00

ГОСУДАР CT BE ННЫ Й КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ (21) 4722189/24 (22) 08.06.89 (46) 23.07.91. Бюл, ЬЬ 27

Фиг.1

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (72) В. А. Абрамов, M. Д. Венедиктов, Б, Ш.

Златкин и Н. И. Семенов (53) 621.394. 64(088,8) (56) Техника средств связи. Сер. Техника радиосвязи. 1982, № 1, с. 32-48.

Техника средств связи. Сер, Техника радиосвязи. 1985, № 1, с. 31 —.40. .Авторское свидетельство СССР

¹ 794742, кл. Н 04 В 3/46, 1979. (54) УСТРОЙСТВО ДЛЯ АСИНХРОННОГО

ПЕРЕПРИЕМА ДЕЛЬТА-МОДУЛИРОВАН НОГО СИГНАЛА . ц. Ж 1665516 А1 (57) Изобретение относится к технике связи и вычислительной технике. Его использование в цифровых системах передачи позволяет повысить точность устройства за счет нерегулярной коррекции скорости передачи дельта-модулированного сигнала. Устройство содержит триггеры 1, 2 задержки, счетные триггеры 5,6, решающий блок

8, элемент 9 НЕ, электронный переключатель 11, ключевые элементы 12, 13, элемент

ИЛИ 14 и регенератор 15, Благодаря введению триггеров 3, 4 задержки, блока 7 выделения серий паузных комбинаций и элемента НЕ 10 в устройстве обеспечивается вЫравнивание скоростей не с разностной частотой, а в случайные моменты времени при появлении паузных комбинаций символов 010101 или 101010, 1 3. и. ф-лы, 3 ил, 1665516

30

40.45

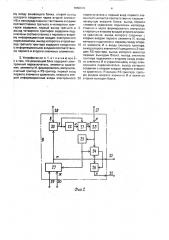

Изобретение относится к технике связи и вычислительной технике и может быть использовано в цифровых системах передачи например в радиорелейных системах для органиэации служебных каналов свяхи путем сопряжения независимых дельта-модулированных (ДМ) сигналов "по цифре". (Цель изобретения — повышение точности устройства за счет нерегулярной коррекции скорости передачи ДМ-сигнала, На фиг, 1 приведена функциональная схема устройства; на фи . 2 — выполнение решающего блока; на фиг. 3 — временные диаграммы работы.

Устройство содержит первый-четвертый триггеры 1 — 4 задержки, первый 5 и второй 6 счетные триггеры, блок 7 выделения серий

1 паузных комбинаций, решающий блок 8, первый 9 и второй 10 элементы Н Е, электронный переключатель 11, первый 12 и второй 13 ключевые элементы, элемент ИЛИ 14 и регенератор 15. На фиг, 1 обозначены информационный вход 16, первый 17, второй 18 тактовые входы, выход 19.

Блок 7 выделения серий паузных комбинаций символов 010101/101010 в простейшем случае может быть реализован на триггере и элементе равнозначности, Решающий блок 8 выполнен (фиг. 2) на первом 20 и втором 21 элементах сравнения, формирователе 22 импул ьсов (одновибраторе), первом 23 и втором 24 элементах И, счетном триггере 25, RS-триггере 26 и электронном переключателе 27, На фиг. 2 обоз. начены первый-четвертый входы 28-31 и первый 32 и второй 33 выходы блока 8, Регенератор 15 выполнен так же, как и в известном устройстве.

На фиг. 3 обозначены следующие сигналы: а — входной ДМ-сигнал на входе 16; б— тактовые импульсы с частотой fT на входе 17; в — сигнал на втором выходе первого счетного триггера 5; r, д — сигналы на выходах сответственно первого 1 и второго 2 триггеров задержки, е — тактовые импульсы с частотой fi на входе 18; ж — сигнал на втором выходе второго счетного триггера 6; з — сигнал на выходе первого элемента 20 сравнения решающего блока 8; и — сигнал на выходе формирователя 22 импульсов блока 8; к— сигнал на выходе второго элемента 21 сравнения блока 8„ л — сигнал с выхода блока 7 выделения серий паузных комбинаций; м, н— сигналы соответственно на втором 33 и первом 32 выходах решающего блока 8, о, и— сигналы на выходах соответственно первого 12 и второго 13 ключевых элементов; р— сигнал на выходе 19 устройства.

Устройство работает следующим ооразом.

Входной ДМ-сигнал, представляющий собой случайную последовательность дво-, ичных символов 1 и О длительностью r =T, 1

T= f >, поступает из линии связи на информационный вход 16 устройства, откуда подается на информационные входы первого

1 и второго 2 триггеров. Одновременно синхронная последовател ьность сопровождающих синхронных тактовых импульсов (ТИ) в виде меандра с длительностью т =Т/2 посту-, пает от устройства тактовой синхронизации (не показано) через вход 17 синхронных тактовых импульсов на вход первого счетного триггера 5. При этом символы ДМ-сигнала и синхронные тактовые импульсы сопровождаются фазовыми флуктуациями. Асинхронная последовательность тактовых импульсов также в виде меандра с длитель-1 ностью r =- Т /2 поступает без фазовых флуктуаций, например от местного кварцевого генератора, на вход 18 асинхронных тактовых импульсов устройства.

С противафазных выходов первого счет- ного триггера 5 синхронные тактовые импульсы уже с длительностью r = Т и с частотой, поделенной в два раза, подаются на тактовые входы первого 1 и второго 2 триггеров. В результате ДМ-сигнал разделяется на две последовательности с длительностью символов г = 2Т, одна из которых содержит четные, а другая — нечетные weменты входного ДМ-сигнала, Далее, эти последовательности четных и нечетных элементов ДМ-сигнала поступают соответственно на информационные входы третьего 3 и четвертого 4 триггеров, которые тактируются выходными сигналами решающего блока- 8, причем четвертый триггер 4 подключен к второму выходу 33 решающего блока 8 непосредственно, а третий триггер 3 — через второй элемент НЕ 10, Последовательность четных элементов ДМсигнала проходит на вход элемента ИЛИ 14 через второи ключевой элемент 13, На другой вход элемента ИЛ И 14 может поступать; или последовательность нечетных элементов ДМ-сигнала через электронный переключатель 11 и первый ключевой элемент

12, или же инвертированная последовательность четных элементов ДМ-сигнала с противофазного выхода третьего триггера 3.

Элемент ИЛИ 14 преобразует последовательности четных и нечетных элементов в общий ДМ-сигнал. Выходной регенератор

15 обеспечивает синфазность ДМ-сигнала с асинхронными тактовыми импульсами, Решающий блок 8 формирует свои сигналы путем сопоставления взаимного расположения асинхронных тактовых импульсов на выходе второго счетного триг1665516

10 в пачках символов, 15

45

55 гера 6 относительно синхронных тактовых импульсов на выходе первого счетного триггера 5. Если фронт асинхронных ТИ попадает в зону флуктуации (джиттера) синхронных

ТИ, т.е, разность между синхронным и асинхронным импульсами меньше длительности импульса, вырабатываемого одновибратором 22, то на выходе второго элемента 21 сравнения появляется сигнал, который перебрасывает счетный триггер 25. Импульс, являющийся разностью между синхронными и асинхронными тактовыми импульсами на выходе первого элемента 20 сравнения, запускает одновибратор 22, который формирует импульс, равный по длительности величине джиттера, Сигнал с выхода второго элемента 21 сравнения, появляющийся только тогда, когда фронт асинхронных тактовых импульсов попадает в зону флуктуации синхронных тактовых импульсов, может пройти на счетный триггер 25 через первый элемент И 23 при появлении в ДМ-сигнале комбинаций символов 010101 или ... I01010, Электроннь!й переключатель 27., управляемый счетным триггером 25, изменяет фазу тактовых импульсов, поступающих в блоке

8 на первый элемент 20 сравнения и с второго выхода 33 решающего блока 8 на тактовые входы третьего 3 и четвертого 4 триггеров, Таким образом, при fr < f, пропуск символов ДМ-сигнала происходит в моменты появления паузных комбинаций символов 010101 или 101010.

При f>> < fT.ñèãíàë.â решающем блоке 8 с выхода первого элемента И 23 проходит через второй элемент И 24 и устанавливает

RS-триггер 26 в единичное состояние. B резул ьтате электрон н ы и пере кл ючател ь .11 подключается к инверсному выходу третьего триггера 3. При этом, если на прямом выходе третьего триггера 3 был символ

"Единица", то в следующий тактовый момент на выход регенератора 15 пройдет символ "Ноль" с инверсного выхода третьего триггера 3 через электронный переключатель 11 и первый ключевой элемент 12, После этого триггер 26 сбрасывается в нулевое состояние импульсом с выхода электронного переключателя 27. В результате повторится символ "Единица" с прямого выхода третьего триггера 3. Следовательно, при fT > fT комбинация символов 010101 заменяется комбинацией 01010101, а комбинация символов 101010 — комбинацией 10101010 (подчеркнуты вставляемые символы), Таким образом, в устройстве выравнивание скорости осуществляется не регулярно с разностной частотой, а в случайные моменты времени, когда в сигнале появляются паузные комбинации символов 010101 или 101010, Тем самым уменьшаются гармонические помехи с разностной частотой

fT-fT в канале тональной частоты, а также искажения при ДМ с мгновенным компадированием, где приращения аппроксимирующего напряжения зависят от номера элемента

Формула изобретения

1. устройство для асинхронного переприема дельта-модулированного сигнала, содержащее первый и второй счетные триггеры, первый и второй триггеры задержки, решающий блок, электронный переключатель, первый и второй ключевые элементы, первый элемент НЕ, элемент ИЛИ и регенератор, вход первого счетного триггера является первым тактовым входом устройства, тактовый вход регенератора объединен с входом первого элемента НЕ и является вторым тактовым входом устройства, информационные входы первого и второго триггеров задержки обьединены и являются информационным входом устройства, первый выход первого счетного триггера соединен с тактовым входом первого триггера задержки, второй выход первого счетного триггера подключен к тактовому входу второго триггера задержки и первому входу решающего блока, первый выход которого соединен с управляющим входом электронного переключателя, выход первого элемента НЕ подключен к входу второго счетного триггера, первый выход которого соединен с вторым входом решающего блока и управляющим входом первого ключевогоэлемента, второй выход второго счетного триггера подключен к управляющему входу второго ключевого элемента, выходы ключевых элементов соединены с входами элемента ИЛИ, выход которого подключен к информационному входу регенератора, выход которого является выходом устройства, о т л и ч а ю щ е е— с я тем, что, с целью повышения точности устройства путем нерегулярной коррекции скорости передачи дельта-модулированного сигнала, в устройство введены блок выделения серий паузных комбинаций, второй элемент НЕ, третий и четвертый триггеры задержки, третий вход решающего блока подключен к второму выходу второго счетного триггера, выходы первого и второго триггеров задержки соединены с инфор-. мационными входами соответственно третьего и четвертого триггеров задержки и соответственно с первым и вторым входами блока выделения серий паузных комбинаций, выход которого подключен к четверто I ббЬэ1b

Му входу решающего блока, второй выход которого соединен через второй элемент

НЕ и непосредственно с тактовыми входами соответственно третьего и четвертого триг геров задержки, первый выход третьего и 5 выход четвертого триггеров задержки под- . ключены соответственно к первому и второ му информационным входам электронного переключателя, выход которого и второй выход третьего триггера задержки соединены 10 с информационными входами соответствен но первого и второго ключевых элементов, 2. Устройство по и. 1, о т л и ч а ю щ е е,с я тем, что решающий блок содержит алек- 15 тронный переключатель, элементы сравне ния, элементы И, формирователь импульсов, счетный триггер и RS-триггер, первый вход первого элемента сравнения, первый и второй информационные входы электронного 20 (переключателя и первый вход первого элемента И являются соответственно первым,,— четвертым входами блока, выход первого элемента сравнения подключен непосредственна и через формирователь импульсов к первому и второму входам второго элемента сравнения, выход которого соединен = вторым входом первого элемента И, выход которого подключен к первому входу второго элемента И и входу счетного триггера, выход второго элемента И соединен с Я-входом HS"òðèããåðà, выход которого является первым выходом блока, выход счетного триггера подключен к второму входу второго элемента И и управляющему входу электронного переключателя, выход которого соединен с вторым входом первого элемента сравнения, R-входом РЯ-триггера, третьим входом второго элемента И и является вторым выходом блока.

1665516

7 1

1 /0 /0011 д / Ð1 00 1

/ <1

f Of 0011 0101

Редактор Г.Гербер

Заказ 2399 Тираж 463 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 а)

r)

8)

ã1

d) е) я)

3) и)

z) л)

e) ю) и)

7)

p) Составитель О.Ревинский

Техред М,Моргентал Корректор 3 Лончакова