Устройство приема стартстопно-синхронной системы

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи. Цель изобретения - сокращение времени установлений связи при инверсии в канале связи. Устройство приема стартстопно-синхронной системы содержит выходной блок 1, стартстопный распределитель 2, первый, второй генератор 3 управляющих импульсов, накопитель 6, блок 7 стартстопной коррекции, входной блок 9, наборный блок 11, блок 12 совпадения, синхронный распределитель 13. Цель достигается введением счетчика 4, первого и второго дешифраторов 5, 8, блока 10 коммутации. 4 ил.

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (si>s Н 04 L 1/16

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4738909/09 (22) 18.09.89 (46) 23.07.91. Бюл, М 27 (72) H.B.Êàðàëêèí, В.И.Карпов, М,Д,Рубанов, В.В,Сударев, В.Л.Стишковский и

В,К,Дубанов (53) 621.394(088.8) (56) Шляпоберский В.И. Элементы дискретных систем. связи. — M,: Военное издательство, 1965, с.262. (54) УСТРОЙСТВО ПРИЕМА СТАРТСТОПНО-СИНХРОННОЙ СИСТЕМЫ,5U,, 1665522 А1 (57) Изобретение относится к электросвязи.

Цель изобретения — сокращение времени установлений связи при инверсии в канале связи. Устройство приема стартстопно-синхронной системы содержит выходной блок

1, стартстопный распределитель 2, первый, второй генератор 3 управляющих импульсов, накопитель 6, блок 7 стартстопной коррекции, входной блок 9, наборный блок 11, блок 12 совпадения, синхронный распределитель 13. Цель достигается введением счетчика 4, первого и второго дешифраторов 5, 8, блока 10 коммутации. 4 ил.

1665522

Изобретение относится к электросвязи и может использоваться в темграфии.

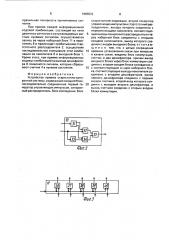

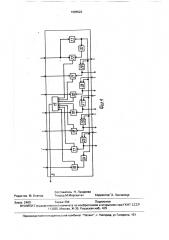

Цель изобретения — сокращение времени установления связи при инверсии в канале связи, На фиг.1 изображена структурная электрическая схема предлагаемого устройства; на фиг,2 —; на фиг.3 — схема наборного блока; на фиг.4 — схема накопителя.

Устройство содержит выходной блок 1, стартстопный распределитель 2, второй генератор 3 управляющих импульсов, счетчик

4, первый дешифратор 5, накопитель 6, блок

7 стартстопной коррекции, второй дешифратор 8, входной блок 9, блок 10 коммутации, наборный блок 11, блок 12 совпадения, синхронный распределитель 13, первый генератор 14 управляющих импульсов.

Накопитель 6 содержит элемент ИЛИ

15, элементы И 16 — 22, дифференциальную цепь 23, триггеры 24 — 30.

Блок 10 коммутации содержит триггер

31, элемент И 32, инвертор 33, элемент И 34, элемент ИЛИ 35.

Наборный блок 11 содержит элементы

И 36 — 40.

Устройство работает следующим образом.

В исходном состоянии с первого выхода триггера 31 блока 10 коммутации управляющий сигнал поступает на первый вход элемента И 32, Комбинация покоя в виде последовательности сигналов из пяти нулей и одной единицы через входной блок 9, элементы И

32, ИЛИ 36 блока 10 поступает на вход наборного блока 11 и на первый вход блока 12, содержащего элемент И на два входа, первый из которых подключен через инвертор.

Под действием сигналов с выходов синхронного распределителя 13, определяемых частотой генератора 14 и следующих синфазно с сигналами принимаемой информации, первые пять нулей записываются через элементы И 36 — 40наборного блока 11 в накопитель 6 на триггеры 25 — 29 соответственно, Шестой единичный импульс воздействует на первый вход блока 12, на второй вход которого синфазно поступает единичный импульс с выхода синхронного распределителя 13, В результате с выхода блока 12 выдается сигнал с нулевым уровнем, который удерживает в исходном (нерабочем) состоянии блок 7 стартстопной коррекции и, следовательно, генератор 3, стартстопный распределитель 2, Единичный сигнал с выхода стартстопного распределителя 2 поступает на первый вход элемента И 22 накопителя 6, разрешая подачу стопового

55 сигнала с выхода триггера 30 через элемент

ИЛ14 15 на выходной блок 1. Единичный сигнал с выхода дешифратора 8, представляющего элемента И-НЕ, сбрасывает счетчик 4 в нулевое состояние.

В случае инверсии принимаемых сигналов комбинация покоя представляет последовательность из пяти единиц и одного нуля, которая поступает через входной блок

9, элементы И 32, ИЛИ 36 блока 10 на вход наборного блока 11 и вход блока 12, Под действием сигналов с выхода синхронного распределителя 13 первые пять единиц записываются через элементы И 36-40 наборного блока 11 в накопитель 6 на триггеры

25 — 29. Эти сигналы с выходов триггеров 2529 поступают на дешифратор, на выходе которого появляется сигнал, регистрируемый счетчиком 4. При приеме шестого сигнала с нулевым уровнем на выходе блока 12 образуется управляющий сигнал, воздействующий на вход блока 7 стартстопной коррекции, который запускает генератор 3, обеспечивающий продвижение единицы в стартстопном распределителе 2.

При поступлении единичного сигнала с выхода стартстопного распределителя 2 на первый вход элемента И 16 накопителя 6 с триггера 24 через элемент ИЛИ 15 выдается стартовый (нулевой) импульс на выходной блок 1. В соответствии с оступлением сигналов с выхода стартстоп ного распределителя

2 на первые входы элементов И 17 — 21 происходит последовательное считывание сигналов, записанных на триггерах 24 — 29, через элементы И 17-21, ИЛИ 15 накопителя 6 на выходной блок 1, В конце стартстопного цикла единичный сигнал с выхода стартстопного распределителя 2 поступает на первый вход элемента И 22 и на вход дифференциальной цепи 23 накопителя 6.

В результате с выхода триггера 30 через элементы И 22, ИЛИ 15 выдается стоповый сигнал на выходной блок 1, а сигналом с выхода дифференциальной цепи 23 все триггеры накопителя 6 устанавливаются в нулевое состояние. При приеме подряд М > 6 комбинаций покоя в инверсном виде срабатывает счетчик 4 и на его выходе появляется сигнал, под действием которого срабатывает триггер 31 блока 10 коммутации, Управляющий сигнал с второго выхода триггера

31 поступает на первый вход элемента И 34.

Принимаемая информация с выхода блока 9 поступает теперь через инвертор 33, элементы И 34, ИЛИ 35 на вход наборного блока 11 и первый вход элемента 12 совпадения. В результате инверсии, производимой в блоке 10 коммутации, восстанавливается

1665522 правильная полярность принимаемых сигналов, При приеме каждой информационной кодовой комбинации, состоящей из пяти двоичных сигналов и сопровождаемых шестым нулевым сигналом, осуществляется запись ее через наборный блок 11 в накопитель 6 и происходит срабатывание стартстопного распределителя 2, осуществляя последовательное считывание этой комбинации иэ накопителя 6 в выходной блок 1.

Кроме этого, при приеме информационных кодовых комбинаций на выходе дешифратора 8 появляются сигналы, которые сбрасывают счетчик 4 в нулевое состояние, Формула изобретения

Устройство приема стартстопно-синхронной системы, содержащее входной блок, последовательно соединенные первый генератор управляющих импульсов, синхронный распределитель, блок совпадения, блок стартстопной коррекции, второй генератор управляющих импульсов и стартстопный распределитель, выходы которого соединены с первыми входами накопителя. соответствую5 щие выходы синхронного распределителя через наборный блок соединены с вторыми входами наполнителя, выход которого соединен с входом выходного блока, о т л и ч а ющ е е с я тем, что, с целью сокращения

10 времени установления связи при инверсии в канале связи, введены блок коммутации, счетчик и два дешифратора, причем выход входного блока через блок коммутации соединен с вторым входом блока совпадения и

15 с соответствующим входом наборного блока. соответствующие выходы накопителя соединены с входами дешифраторов, выход первого дешифратора соединен с первым входом счетчика, второй вход которого сое20 динен с выходом второго дешифратора, а выход счетчика соединен с вторым входом блока коммутации.

1665522

Составитель Н. Лазарева

Редактор М. Бланар Техред М.Моргентал Корректор Э. Лончакова

Заказ 2400 Тираж 394 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/S

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101